Vivado管脚分配与布局技巧:硬件实现的终极指南

发布时间: 2025-01-04 21:18:37 阅读量: 7 订阅数: 18

Verilog实现示波器 基于Xilinx vivado工具开发。运行平台:

# 摘要

Vivado是Xilinx公司推出的用于FPGA设计的集成设计环境,管脚分配是其关键步骤之一。本文对Vivado管脚分配的理论基础和实践操作进行系统性的探讨。首先概述了管脚分配的基本概念和重要性,然后深入分析了硬件考量因素如信号完整性和电源地线布局,以及软件工具支持,包括布局工具的使用和约束文件管理。实践操作章节详细介绍了如何在Vivado中进行初步设置、高级技巧和优化流程。最后,本文通过案例分析展示了管脚分配和布局在实战中的应用,重点讨论了优化案例和布局挑战的应对策略。文章旨在为FPGA开发者提供全面的管脚分配和布局指南,帮助他们提高设计效率和性能。

# 关键字

Vivado;管脚分配;信号完整性;布局优化;约束管理;案例分析

参考资源链接:[Vivado Design Suite UG903用户指南:约束使用详解](https://wenku.csdn.net/doc/1y3o5mbuh8?spm=1055.2635.3001.10343)

# 1. Vivado管脚分配概述

在现代数字电路设计中,Vivado设计套件扮演着至关重要的角色,而管脚分配作为设计流程中的关键步骤,直接关系到FPGA(现场可编程门阵列)或ASIC(应用特定集成电路)的性能表现。有效的管脚分配能够显著提高电路的工作效率,保证信号的完整性和可靠性,并且有利于后续的布局和布线工作。本章将简要介绍管脚分配的定义、目的及其在实际应用中的重要性,为后续章节的深入探讨打下基础。接下来,我们将探讨管脚分配的基础理论,以及在Vivado中的具体操作和优化流程。

# 2. Vivado管脚分配理论基础

### 2.1 管脚分配的基本概念

#### 2.1.1 管脚分配的目的和重要性

管脚分配是FPGA设计流程中的一个重要步骤,它涉及到将设计中的逻辑引脚映射到实际物理FPGA芯片的管脚上。这一过程的重要性在于,它不仅决定了信号的路径,还会影响到信号完整性、时序、功耗以及电路板的整体布局。一个好的管脚分配方案可以确保设计满足性能要求,避免潜在的电气问题,甚至在一些高可靠性场合,还能够提升系统的稳定性。

#### 2.1.2 管脚定义和约束类型

在Vivado中,管脚的定义通常通过XDC约束文件来实现,文件中详细描述了各个信号与物理管脚的对应关系。约束类型主要包括:

- I/O标准约束:决定管脚的电气标准,如LVCMOS、LVTTL等。

- 驱动强度约束:指定输出驱动的能力。

- 上拉/下拉约束:设置输入管脚在无信号输入时的默认状态。

- 差分对约束:定义哪些管脚应该组成差分信号对。

这些约束确保了设计能够在实际硬件中正确地工作,并且能够在不同的电压和电流条件下稳定运行。

### 2.2 管脚分配的硬件考量

#### 2.2.1 信号完整性

信号完整性问题指的是信号在传输过程中发生变形,导致无法正确被接收方识别。在管脚分配过程中,必须考虑信号的反射、串扰、同步切换噪声等问题。合理分配高速信号的管脚位置,尽量避免长走线和复杂布线,可以有效降低这些问题的发生。

#### 2.2.2 电源和地线布局

电源和地线的布局对于FPGA的稳定运行至关重要。不适当的布局可能会造成电源噪声,进而影响到芯片内部的逻辑操作。因此,在进行管脚分配时,需要为每个电源域合理分配管脚,并尽可能地减少电源和地线的环路面积。

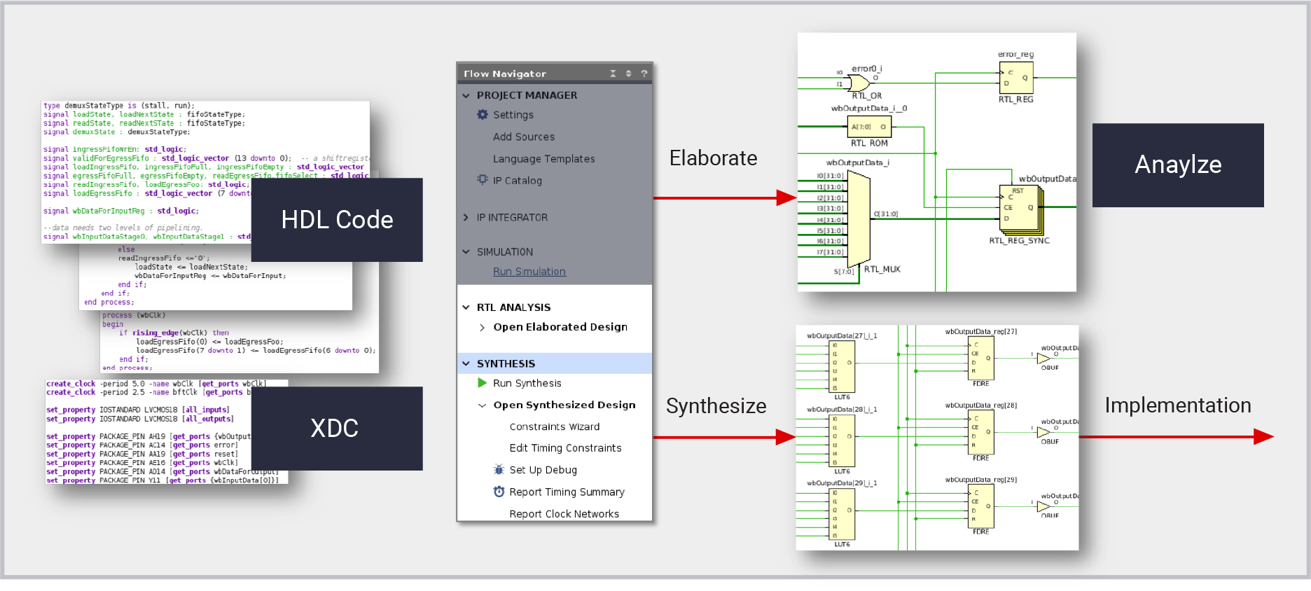

### 2.3 管脚分配的软件支持

#### 2.3.1 Vivado布局工具的使用

Vivado的布局工具提供了自动和手动两种管脚分配方式。自动分配简化了设计流程,特别是对于初学者和小规模设计。而手动分配则提供更细致的控制,使得设计者可以根据设计需求和硬件考量,逐个指定信号到管脚的分配。

#### 2.3.2 约束文件的编写和管理

在Vivado中,约束文件可以是静态的,也可以是与源代码相链接的。编写约束文件时,需要注意格式和语法的正确性,以确保工具能够正确解析。管理约束文件的最有效方法是使用版本控制系统,这样可以追溯设计变更,并且便于团队协作。

接下来,让我们进一步深入了解具体的Vivado布局工具使用和约束文件编写技巧,这些都是保障设计质量和效率的关键因素。

# 3. Vivado管脚分配实践操作

## 3.1 管脚分配的初步设置

### 3.1.1 创建项目和定义设备

在开始管脚分配之前,首先要创建一个新的Vivado项目,并且正确地选择和定义目标FPGA设备。创建项目涉及到一系列的步骤,这包括选择合适的模板、提供项目名称、设定项目保存路径、选择目标设备及其封装类型。

**创建项目步骤如下:**

1. 打开Vivado软件,点击“Create New Project”。

2. 在弹出的向导中,输入项目名称并选择项目存储路径,点击“Next”。

3. 选择“RTL Project”作为项目类型,并点击“Next”。

4. 在“Add Sources”界面,可以选择添加现有的源文件或跳过,点击“Next”。

5. 接下来,设置目标设备。这里需要选择正确的FPGA系列、器件型号和封装类型。确保所选设备与实际硬件相符,点击“Next”。

6. 最后,可以设置仿真和综合的选项,一般可以使用默认设置,点击“Finish”完成项目创建。

**定义设备步骤如下:**

- 在Vivado项目界面左下角,点击“Settings”。

- 在“Project Settings”窗口中,选择“IP”选项卡下的“Repository”页面。

- 确认或修改“Project Specific Repository”路径以适应IP库位置。

- 点击“Project Settings”界面左侧的“Project”选项卡,然后选择“Part”页面。

- 在此页面,可以重新选择或验证当前

0

0