【Allegro信号完整性】:线宽、间距的优化策略

发布时间: 2024-12-17 00:53:11 阅读量: 1 订阅数: 3

FTP上传下载工具,支持上传下载文件夹、支持进度更新.7z

参考资源链接:[Allegro线路设计规则详解:线宽、间距、等长与差分设置](https://wenku.csdn.net/doc/1xqqxo5raz?spm=1055.2635.3001.10343)

# 1. Allegro PCB设计基础与信号完整性概念

## 1.1 PCB设计基本概念

在电子工业中,印刷电路板(PCB)是现代电子设备不可或缺的组成部分。Allegro作为一个功能强大的PCB设计软件,广泛应用于复杂的电路设计中。在使用Allegro进行设计之前,了解PCB的基础知识和信号完整性的重要性是至关重要的。

## 1.2 信号完整性定义

信号完整性指的是一个电子系统中信号的质量,它影响到电子设备能否正常地传输和接收信号。信号完整性低可能导致数据传输错误、系统不稳定甚至损坏。对于高速电路设计而言,保证信号完整性尤为关键。

## 1.3 影响信号完整性的因素

信号完整性受到多种因素的影响,包括但不限于线路的长度、布局、线宽与间距、电容、电感等。掌握这些因素将有助于在Allegro PCB设计中做出更合理的决策,从而提升整个电路的性能。

在后续的章节中,我们会逐步深入探讨线宽和间距如何具体影响信号完整性,并提供实际操作的指导,帮助读者更好地在Allegro中进行PCB设计。

# 2. 线宽和间距对信号完整性的影响

## 2.1 理解线宽与信号传输

### 2.1.1 线宽与阻抗控制

在高速PCB设计中,控制特性阻抗是确保信号完整性的重要因素之一。特性阻抗主要取决于导线的宽度、厚度、介质的介电常数以及PCB板的厚度等因素。线宽是其中的一个可控变量,直接关系到信号的传输特性。

过窄的线宽会导致特性阻抗的增加,这会使得驱动端和接收端的阻抗匹配变得困难,从而引发信号反射。另一方面,过宽的线宽虽然可以降低特性阻抗,但可能会引起更多的串扰和空间占用问题。因此,在设计过程中需要精心选择合适的线宽,以满足特定的阻抗要求。

```mermaid

graph LR

A[选择线宽] --> B[计算特性阻抗]

B --> C{阻抗是否匹配}

C -->|是| D[继续设计]

C -->|否| E[调整线宽]

E --> B

```

在实际的PCB布局中,可以使用仿真软件来模拟线宽对特性阻抗的影响,以达到最佳匹配效果。

### 2.1.2 线宽对信号损耗的影响

信号在传输过程中的损耗主要包括介质损耗、铜线损耗和辐射损耗。其中,铜线损耗与线宽的平方根成反比。这意味着较宽的线能够减少铜线损耗,提高信号的质量。然而,增加线宽并非万能,因为过宽的线会使得PCB成本增加,同时还会增加布局的复杂度。

为了平衡性能和成本,设计师需要根据信号的频率和重要性来选择线宽。对于高频率或者关键信号,应该优先考虑使用较宽的线宽来减少损耗。在进行设计时,可以通过调整线宽来优化信号路径,确保信号在传输过程中的完整性和可靠性。

```mermaid

graph TD

A[选择线宽] --> B[分析信号频率]

B --> C[考虑信号重要性]

C --> D[确定铜线损耗要求]

D --> E[确定最佳线宽]

```

## 2.2 间距对信号完整性的双重效应

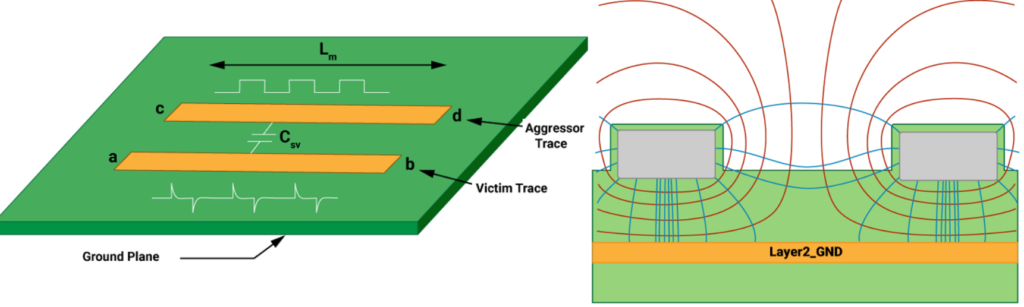

### 2.2.1 串扰与间距

串扰是指信号在传输线之间相互感应而产生干扰的现象。在高密度和高速度的PCB设计中,串扰是需要严格控制的因素。线与线之间的间距直接影响到串扰的程度,间距越大,串扰越小。然而,在布局限制下,增加间距有时并不现实,因此在设计中需要找到合适的折中方案。

在实际设计中,可以通过仿真工具来分析不同间距下的串扰情况,并根据分析结果调整线间距。此外,对于并行走线,可以采用等长布线策略来进一步降低串扰的影响。

```mermaid

graph TD

A[确定线间距] --> B[评估串扰风险]

B --> C{是否满足要求?}

C -->|是| D[继续布线]

C -->|否| E[调整线间距]

E --> B

```

### 2.2.2 电磁兼容性与间距选择

电磁兼容性(EMC)是评价电子产品电磁环境影响的指标。设计中需要充分考虑电磁兼容性,以减少设备间的干扰。间距的选择对于控制辐射和感应耦合至关重要。在设计时,合理的间距能够减少电磁干扰(EMI)的产生,提高电路的稳定性。

在实际操作中,不仅要关注同一层上的间距,还应考虑不同层之间的间距。例如,高速信号层与地层、电源层之间的间距对电磁屏蔽效果有着重要影响。通过合理设计,可以有效地提升PCB的整体电磁兼容性。

```mermaid

graph TD

A[选择间距] --> B[评估EMC风险]

B --> C{是否满足要求?}

C -->|是| D[继续布线]

C -->|否| E[调整间距]

E --> B

```

## 2.3 线宽和间距的理论优化模型

### 2.3.1 传输线模型与仿真

传输线模型是分析信号完整性问题的基础。在设计高速电路时,可以通过传输线模型来预测信号在导线上的行为,进而模拟出信号完整性的状况。常用的模型包括传输线方程、微带线模型和带状线模型等。通过这些模型,设计师可以在设计初期预测可能的问题,并对线宽和间距进行优化。

在仿真环节,可以利用如ADS(Advanced Design System)、Cadence等专业仿真软件来创建电路模型,然后进行仿真分析。仿真可以帮助设计师了解信号传输过程中可能出现的问题,并给出优化建议。

```mermaid

graph LR

A[创建传输线模型] --> B[进行仿真分析]

B --> C[识别信号完整性问题]

C --> D[优化线宽和间距]

D --> B

```

### 2.3.2 特性阻抗匹配的优化策略

特性阻抗匹配是确保信号完整性的关键步骤。当信号的阻抗与其源端和负载端的阻抗不匹配时,会发生信号反射,从而导致信号失真和接收端信号质量下降。理想的阻抗匹配可以确保信号传输的效率和完整性。

在实际设计中,优化策略包括调整线宽、使用串联或并联终端匹配技术以及选择合适的阻抗匹配元件等。设计师需要综合考虑电路布局、器件选型和信号特性,以达到最佳的阻抗匹配效果。

```mermaid

graph LR

A[分析信号特性] --> B[确定阻抗要求]

B --> C[调整线宽]

C --> D[选择匹配技术]

D --> E[匹配阻抗元件]

E --> F[验证阻抗匹配效果]

```

通过以上章节的分析,我们可以看到线宽和间距在信号完整性中的重要性以及如何通过理论模型和技术手段进行优化。在下一章节中,我们将进一步探讨在Allegro PCB设计中,如何应用这些理论进行线宽和间距的优化实践。

# 3. Allegro PCB设计中的线宽和间距优化实践

## 3.1 线宽优化的实操技巧

### 3.1.1 高速信号线宽设计准则

在设计高速信号时,线宽的优化是至关重要的。它不仅影响信号的传输速度,还关系到信号的完整性。通常,高速信号线宽的设计准则遵循以下几点:

- **阻抗控制**:在高速设计中,通常要求维持一个恒定的阻抗,以确保信号不会在传输过程中产生过多反射。阻抗的计算通常依据 PCB 材料、铜厚和介质厚度来确定。一般来讲,对于50欧姆的阻抗,线宽通常在10-12 mil左右。

- **温度影响**:PCB在不同温度下,铜的导电率会发生变化,这会影响信号线的特性阻抗。在设计时要考虑到这一点,特别是在特殊环境应用中。

- **制造公差**:PCB制造过程中存在一定的公差,如铜箔厚度变化、蚀刻不均匀等,因此在设计时应预留一定的余量,以确保阻抗的稳定。

-

0

0