集成电路设计的守护者:ERC检查技术深入讲解及稀缺的优化策略

发布时间: 2025-01-08 18:31:20 阅读量: 4 订阅数: 7

protel印制电路板设计:ERC检查.ppt

# 摘要

本文系统地探讨了集成电路设计中的电气规则检查(ERC)过程及其优化策略。首先,本文强调了ERC检查在确保设计完整性与可靠性方面的重要性,并介绍了其在集成电路设计流程中的关键位置。接着,通过阐述ERC检查的主要规则和规则的理论基础,本文揭示了电气连接规则、设备参数规则与设计规则检查(DRC)之间的关系。此外,本文还详细讨论了ERC检查工具的选择与应用,以及规则的设置和常见问题的解决方案。在优化策略部分,文章着重于提高检查性能、规则优化以及检查流程的自动化和智能化。最后,本文展望了ERC检查的未来发展趋势,包括新兴规则的挑战、人工智能应用前景以及智能化解决方案在集成电路设计中的作用。

# 关键字

集成电路设计;电气规则检查(ERC);信号完整性;电源完整性;性能优化;自动化与智能化

参考资源链接:[集成电路工艺分析技术:ERC检查的操作步骤详解](https://wenku.csdn.net/doc/2x5ng2e6n2?spm=1055.2635.3001.10343)

# 1. 集成电路设计与电气规则检查(ERC)

在现代电子产品的开发过程中,集成电路(IC)设计是至关重要的一环。电路设计的每一个细节都关系到最终产品的性能和可靠性。而电气规则检查(ERC)作为集成电路设计流程中的一个关键步骤,其重要性不容忽视。ERC的主要任务是在设计阶段早期识别出可能导致电气问题的设计缺陷,从而避免成本高昂的后期修改。

ERC检查确保设计满足特定的电气标准和规范,例如电压、电流限制和电气连接规则。在复杂电路中,这类检查尤其重要,因为错误和冲突可能会导致电路故障、性能下降甚至完全失效。所以,通过ERC检查可以确保电路板的功能完整性,提升产品质量,并加速产品的上市时间。

在集成电路设计流程中,ERC通常发生在电路图设计完成之后,实际的布局布线(Layout)开始之前。这是因为此时电路的逻辑连接已经固定,ERC可以较为准确地评估电路图设计的电气可行性。未通过ERC检查的设计,需要设计工程师进行修改,并重新验证,直至所有规则都满足要求。这样严格的检查流程,帮助减少了设计错误,增加了产品投产的成功率。

# 2. 电气规则检查(ERC)基础

### 2.1 ERC检查的重要性

#### 2.1.1 设计完整性与可靠性

在集成电路设计过程中,电气规则检查(ERC)是保证设计完整性与可靠性的重要步骤。通过 ERC,设计者可以确保电路中的每一个组件都有正确的电气连接,且所有电气参数符合预期的规范。这一步骤避免了设计缺陷,比如错误的电源与地连接,导致短路或过流,甚至整个电路板的损坏。

ERC 还能够识别设计中的潜在问题,诸如电气噪声、信号完整性问题等,这些问题如果不提前识别和解决,可能会在产品制造或使用过程中导致不可预料的故障。此外,由于产品越来越小型化和集成化,设计师需要对 ERC 给予更多的重视,以确保每一个电路节点都符合设计规范。

#### 2.1.2 ERC在集成电路设计流程中的位置

ERC 应在集成电路设计流程的多个阶段进行,以确保在整个设计周期内对电路的电气规则进行持续验证。具体来说,ERC 可以在以下阶段进行:

- **概念验证阶段**:此时进行初步的ERC检查,以验证设计的基本概念和电气连接是否合理。

- **设计细化阶段**:在电路图详细完成后和布局前,再次进行ERC检查,确认所有细节都符合设计规则。

- **布局后阶段**:设计已经落实到物理层面之后,进行 ERC 检查,确保布局没有破坏先前确认的电路规则。

- **生产前阶段**:在设计准备进入生产阶段之前,进行最终的 ERC 检查,以确保设计满足所有生产要求。

通过这样分阶段的 ERC 检查,能够显著降低在生产过程中发生错误的可能性,节省开发成本,并缩短产品上市时间。

### 2.2 ERC检查的主要规则

#### 2.2.1 电气连接规则

电气连接规则是 ERC 检查中最为基础的规则之一,这些规则确保了电路中各个组件的电气连接都是正确和安全的。常见的电气连接规则包括但不限于:

- **短路检测**:任何组件的电源和地之间都不应直接短路。

- **信号完整性**:确保信号线没有发生不合理的拉伸、分叉或短路,这可能影响信号质量。

- **电流限制**:电流超过组件允许值的连接是不被允许的。

#### 2.2.2 设备参数规则

设备参数规则关注的是电路中各个元器件的电气特性,如电阻、电容、电感以及二极管、晶体管等的电气参数是否在允许的范围内。这些规则检查保证了以下方面:

- **额定值检查**:确认元器件的工作电压、电流等参数是否超出其规格限制。

- **功能匹配**:确保所选元器件的特性与电路中的应用需求相匹配。

#### 2.2.3 设计规则检查(DRC)与ERC的对比

尽管 ERC 检查和设计规则检查(Design Rule Check, DRC)在集成电路设计过程中都起到了质量把关的作用,但它们检查的焦点有所不同。DRC 主要关注的是布局布线层面上的物理规则,比如走线宽度、间距、焊盘大小等,而 ERC 关注的是电路的电气行为规则。

ERC 和 DRC 的共同点在于它们都是确保设计符合制造和功能要求的重要步骤,不同点在于 ERC 更注重电路的电气特性和行为。

### 2.3 ERC检查工具的选择与应用

#### 2.3.1 常见ERC工具概述

市场上存在多种 ERC 工具供设计师选择,每种工具都有其特定的功能和优势。以下是一些常用的 ERC 工具:

- **Cadence PSpice**:广泛用于模拟电路和混合信号设计的ERC检查。

- **Altium Designer**:提供从原理图到PCB设计的全流程支持,包含内置的ERC功能。

- **Mentor Graphics PADS**:适用于PCB设计,提供丰富的ERC检查选项。

- **Synopsys PrimeTime**:虽然主要用于时序分析,但也具有基本的 ERC 功能。

#### 2.3.2 工具配置与使用技巧

在选择和配置ERC工具时,有若干最佳实践可以遵循:

- **选择合适的工具**:根据设计的复杂度和团队的经验选择工具,不必盲目追求最尖端的技术,而是选择最能够满足项目需求的工具。

- **定制规则文件**:大多数ERC工具允许用户根据特定的设计需求定制规则检查文件,确保检查的规则与实际设计相匹配。

- **模拟与实际相结合**:在使用ERC工具时,应结合仿真软件进行前仿真,以确保在实际生产前发现潜在的设计问题。

- **持续学习与更新**:随着新工具和新技术的不断出现,设计师应持续关注行业动态,及时更新知识和工具使用技能。

通过熟练掌握这些工具和技巧,设计师可以有效地运用 ERC 来提高设计的质量和效率。

# 3. ERC检查技术的理论与实践

在现代集成电路设计中,电气规则检查(ERC)不仅仅是一个技术流程,它更是确保电路设计可靠性和性能的关键步骤。ERC检查涉及复杂的电气规则,这些规则基于电路和工艺参数的深思熟虑,旨在捕捉设计中的潜在缺陷。本章将深入探讨ERC规则的理论基础、实际设置与执行过程,以及面对常见问题时的解决策略。

## 3.1 ERC规则的理论基础

### 3.1.1 信号完整性与电源完整性的理论

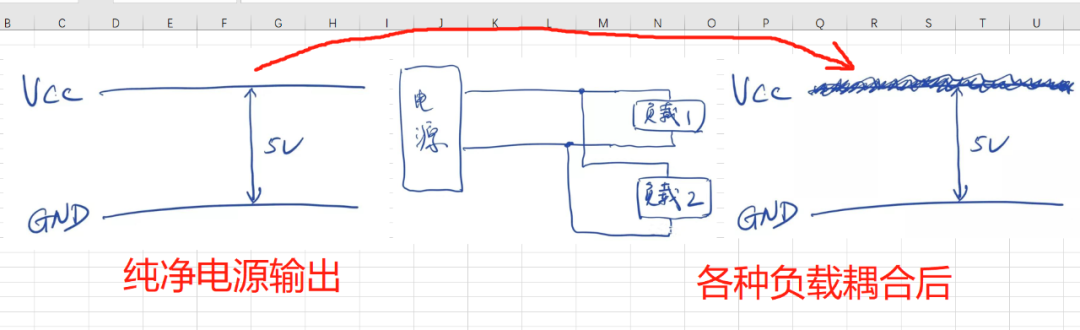

信号完整性和电源完整性是集成电路设计中两个核心的概念。信号完整性关注的是信号在传输过程中是否保持了其完整性,而电源完整性则关注电源网络能否为集成电路提供稳定的电源供应。 ERC规则的制定就是以这些理论为基础,确保设计满足这些核心要求。

信号完整性问题通常包括反射、串扰、时序偏差等,而电源完整性问题主要与电源噪声、电源平面阻抗有关。ERC规则需要能够检测到这些问题的潜在风险,并在设计阶段提前指出,避免将这些问题带入生产阶段。

### 3.1.2 ERC规则的电气逻辑

ERC规则的电气逻辑基于物理学原理,特别是电路论。电路论提供了分析和预测电路行为的数学模型。ERC规则通过一组预定义的条件和参数对电路进行分析,例如

0

0