【NAND Flash编程】:S3C2440存储效率提升的关键技术

发布时间: 2024-12-14 16:16:24 阅读量: 10 订阅数: 18

nand.rar_flash_s3c2440 nand flash

参考资源链接:[三星S3C2440A ARM9微控制器中文手册](https://wenku.csdn.net/doc/6401aceacce7214c316ed9d6?spm=1055.2635.3001.10343)

# 1. NAND Flash基础知识

在数字存储的领域中,NAND Flash凭借其独特的存储方式、较快的读写速度以及高存储密度等优点,在消费电子、移动通信以及固态硬盘等领域获得了广泛应用。为了全面理解NAND Flash,本章节将围绕其工作原理、结构特点以及与NOR Flash的区别来进行深入探讨。

## 1.1 NAND Flash的工作原理

NAND Flash通过非易失性的存储单元阵列来保存数据。数据以页(page)为单位进行读写,而擦除操作则以块(block)为单位执行。这种机制使得NAND Flash在读取速度快,但写入和擦除速度相对较慢。

## 1.2 NAND Flash的结构特点

NAND Flash由若干个块组成,每个块包含多个页。页是读写的最小单位,通常为2的幂次字节。块则是擦除的最小单位,大小通常比页大很多。这种结构使得NAND Flash在存储大量数据时更加高效。

## 1.3 NAND Flash与NOR Flash的对比

相比NAND Flash,NOR Flash的读取速度更快,但其价格较高且每比特成本较高,更适合执行代码或小文件存储。NAND Flash因其成本效益和较高的容量,通常用于数据存储。这两种技术在实际应用中各有优劣,选择时需根据具体需求权衡。

# 2. ```

## 第二章:S3C2440与NAND Flash的交互机制

### 2.1 S3C2440的存储控制器

S3C2440是三星公司推出的一款基于ARM920T内核的微处理器,广泛应用于嵌入式系统中。该处理器内置的存储控制器是实现与NAND Flash交互的关键硬件组件。控制器支持多种内存类型,其中包括NAND Flash,使其能够直接管理存储操作。

存储控制器通过配置相应的寄存器来控制NAND Flash的读写过程。它主要管理以下几个方面:

- I/O端口映射:设置控制NAND Flash的I/O端口,为后续的命令、地址和数据传输提供通道。

- 时序控制:调整读写时序以符合NAND Flash的工作模式。

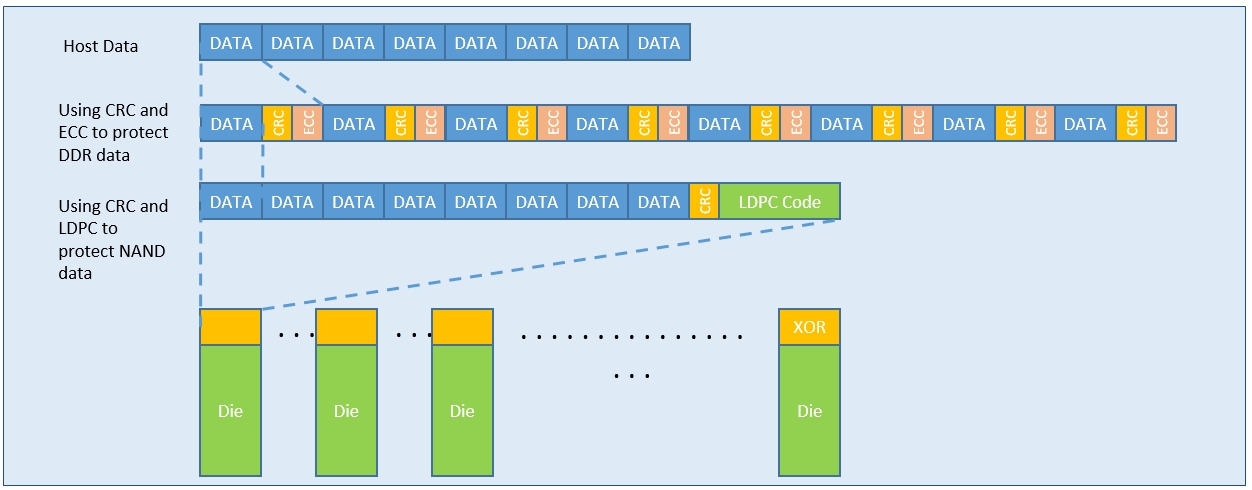

- ECC(Error-Correcting Code)支持:为数据提供硬件级的错误检测与纠正功能。

### 2.2 NAND Flash接口协议

#### 2.2.1 地址、数据和命令的传输机制

NAND Flash的接口协议定义了如何在S3C2440和NAND Flash之间传输地址、数据和命令。S3C2440通常会使用特定的引脚作为数据总线(DQ0-DQ7),用于传输8位数据。地址和命令则通过专门的命令和地址寄存器发送。

传输过程大致如下:

1. 在执行读写操作前,首先需要通过命令寄存器发送相应的命令。

2. 命令之后,将地址信息发送至地址寄存器,以便NAND Flash能够定位到正确的数据页或块。

3. 数据传输过程分为数据输入(写操作)和数据输出(读操作)两种模式。

#### 2.2.2 ECC纠错算法和读写流程

错误校验和纠正(ECC)是确保NAND Flash数据完整性的重要机制。S3C2440存储控制器内置了ECC单元,可以在写入数据到NAND Flash之前计算出校验信息,并在读取数据时验证和纠正错误。

ECC纠错算法的步骤包括:

1. 在写操作时,ECC单元生成校验码并附加到数据块中。

2. 数据写入NAND Flash存储介质。

3. 在读操作时,控制器读取数据和存储的校验码。

4. 使用ECC算法进行数据检验。

5. 如果检测到错误,ECC单元将尝试纠正这些错误。

### 2.3 S3C2440对NAND Flash的硬件支持

S3C2440提供了对NAND Flash的直接硬件支持,包括专用的NAND Flash接口、ECC硬件校验与处理能力,以及灵活的I/O配置。这些硬件特性使得开发者能够更高效地开发NAND Flash存储解决方案。

在硬件支持方面,S3C2440具备以下特点:

- 内置NAND Flash控制器,支持多种NAND Flash设备。

- 支持NAND Flash的页编程(Page Program)和块擦除(Block Erase)操作。

- 提供DMA(直接内存访问)功能,可以进行高效的内存传输。

- 支持坏块管理,可以在硬件层面上进行坏块的检测和替换。

在实际应用中,S3C2440的这些硬件特性能够有效地提升存储系统的性能,减少软件干预,从而达到优化整体存储效率的目的。

```

# 3. 存储效率的关键因素分析

在上一章中,我们了解了S3C2440与NAND Flash之间的交互机制,包括S3C2440的存储控制器和NAND Flash接口协议等。在本章中,我们将深入探讨存储效率的关键因素,具体包括NAND Flash的性能指标、坏块管理策略、垃圾回收机制以及内存映射和页缓存等影响因素。

## 3.1 NAND Flash的性能指标

### 3.1.1 读写速度

NAND Flash的读写速度是衡量其性能的重要指标之一。通常情况下,读写速度的单位是MB/s(兆字节每秒)。对于NAND Flash来说,读操作比写操作要快,尤其是随机读取。这主要是因为NAND Flash采用的是页(Page)作为读写的最小单位,而块(Block)是擦除的最小单位。由于块需要被完整擦除后才能进行写入,因此写入操作通常需要先读出整个块的内容,修改数据后再擦除并写回整个块,这样的操作过程大大降低了写速度。

### 3.1.2 寿命和可靠性

NAND Flash的寿命和可靠性同样至关重要。NAND Flash的寿命通常以擦写次数(P/E Cycles)来衡量,即一个块可以被擦除并重写的次数。由于每次擦写操作都会对存储介质造成损伤,因此擦写次数有限。例如,一些主流的NAND Flash芯片可以支持十万到百万次的擦写。超过这个限制,存储单元的可靠性就会下降,可能会导致数据丢失。

可靠性不仅与擦写次数有关,还与存储环境、使用模式等有关。例如,高温可能会加速存储介质的老化过程。因此,在高可靠性要求的场合,需要采用相应的设计和使用策略来延长NAND Flash的寿命。

## 3.2 影响NAND Flash存储效率的因素

### 3.2.1 坏块管理策略

坏块管理策略对NAND Flash的存储效率有着直接影响。坏块是指在生产过程中产生的不可用块或者在使用过程中因磨损导致失效的块。在NAND Flash中,块一旦发现坏块,就需要被隔离并标记,以便系统不会再使用它们。如何高效地管理坏块,避免坏块对正常块的干扰,对于提高存储效率至关重要。

### 3.2.2 垃圾回收机制

垃圾回收机制是NAND Flash管理中的一个重要组成部分。它负责在存储空间中回收不再使用的数据块,以便这些块可以被重新写入新数据。如果垃圾回收操作执行不力或策略不当,会导致大量空闲块被占用,进而导致实际可用存储空间减少,影响存储效率。因此,设计出高效的垃圾回收机制,对提升整体存储效率具有重要意义。

### 3.2.3 内存映射和页缓存

内存映射是一种将存储设备的块映射到虚拟内存地址的技术,这样就可以像访问内

0

0