【性能提升秘籍】:掌握银灿U盘电路优化技术,解决传输速度瓶颈

发布时间: 2024-12-27 16:21:41 阅读量: 6 订阅数: 5

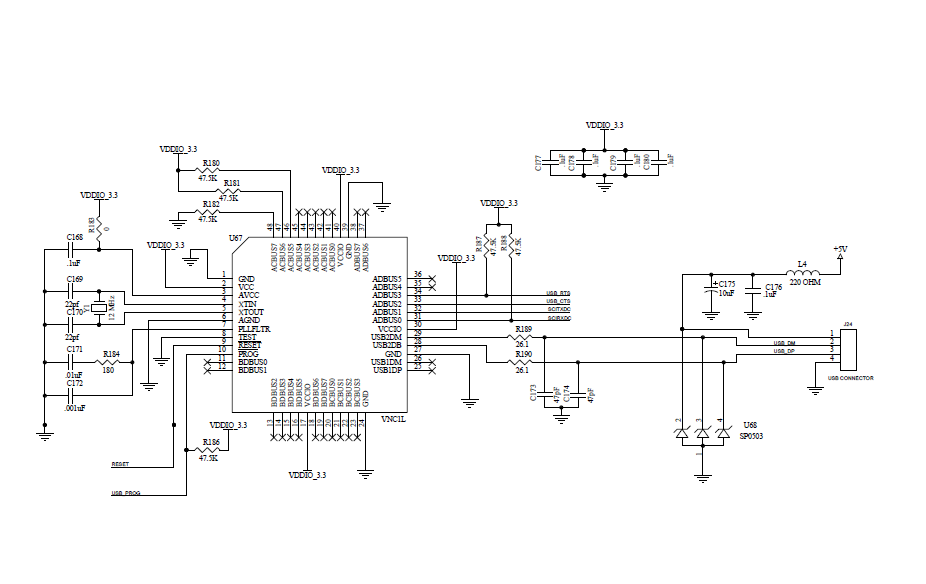

银灿IS917U盘PCB电路(原理图+PCB图)-其它其他资源

# 摘要

银灿U盘电路优化技术是提高存储设备性能和可靠性的重要研究领域。本文系统地概述了银灿U盘电路设计的优化技术,涵盖了理论基础、技术特点、优化实践操作以及进阶技术的探索。通过分析U盘电路结构组成、数据传输过程中的关键理论以及银灿U盘的技术优势,本文进一步探讨了信号完整性和电源管理、电路布线和元件选择对电路性能的影响。此外,本文还提出了针对性能瓶颈识别、数据传输效率提升、信号干扰减少等方面的优化措施,并对优化效果进行了验证与评估。在进阶技术章节中,探讨了高级电路设计优化策略、固件与驱动程序优化,以及面向未来的技术挑战与发展趋势。最后,通过真实世界案例分析,本文总结了优化过程中的挑战与解决方案,并展望了未来银灿U盘电路优化的研究方向。

# 关键字

银灿U盘;电路优化;信号完整性;电源管理;性能测试;固件驱动优化;电路设计策略

参考资源链接:[银灿主控usb3.0U盘电路图方案](https://wenku.csdn.net/doc/6412b775be7fbd1778d4a604?spm=1055.2635.3001.10343)

# 1. 银灿U盘电路优化技术概述

## 1.1 优化技术的重要性

在IT行业中,U盘作为最普遍的数据存储设备之一,其性能和稳定性直接影响用户的工作效率和数据安全。随着技术的进步,银灿U盘通过优化电路设计,实现了性能的提升和品质的强化。电路优化技术不仅关系到U盘的传输速率,还与数据的完整性、电源管理及长期可靠性息息相关。

## 1.2 技术优化的多维考量

U盘电路优化不仅仅是一个技术问题,它还涉及到产品成本、生产工艺、用户体验等多方面的考量。本文将从理论基础、实践操作、进阶技术和案例分析等方面,深入探讨银灿U盘电路优化技术的全貌。

## 1.3 本文的结构与目标

本文旨在为IT行业从业者和对U盘技术感兴趣的读者提供一个全面的技术视角。我们将通过分析银灿U盘的电路设计原理,探讨电路优化的策略,并结合真实世界的案例,总结优化经验,为未来的技术发展提供方向性的见解。

# 2. 理论基础与银灿U盘电路设计原理

### 2.1 U盘电路设计的基本概念

#### U盘的电路结构组成

U盘的电路结构是其功能实现的基础,通常包括以下几个核心部分:

- **主控芯片(MCU)**:负责整个U盘的逻辑控制,包括数据的读写、传输以及与其他电路的交互。

- **存储芯片(Flash Memory)**:用于存储用户数据。

- **USB接口**:用于与计算机等设备连接,传输数据。

- **电源管理模块**:管理U盘的电源输入和输出,包括电压转换、电流控制等。

U盘电路设计需要考虑到不同部分间的协同工作,以及在不同操作环境下的稳定性和兼容性。

#### 数据传输过程中的关键理论

在U盘的数据传输过程中,关键理论包括USB通信协议、信号完整性以及数据校验等:

- **USB通信协议**:定义了U盘与主机之间通信的方式,包括数据包的格式、传输速率、同步和异步传输等。

- **信号完整性**:在高速数据传输中,确保信号质量不受到干扰和衰减,是保证数据准确传输的关键。

- **数据校验**:通过ECC(Error-Correcting Code)等技术,保证数据传输的准确性,防止数据损坏。

这些理论基础是电路设计的核心,它们保证了U盘能够在多种环境下稳定工作,实现高速和可靠的文件传输。

### 2.2 银灿U盘的技术特点

#### 银灿U盘的技术优势分析

银灿U盘的技术优势在于其独到的设计和优化策略,主要包括:

- **专有技术**:银灿可能拥有自己的专有技术,如改进的读写算法,这可极大提升数据传输速度和降低错误率。

- **高兼容性设计**:确保银灿U盘可以在不同操作系统和硬件环境下保持良好的兼容性和性能。

- **先进的封装工艺**:在电路板设计和芯片封装上采用先进的制造工艺,减少能耗和提升存储密度。

#### 银灿U盘与其他品牌的技术对比

在与其他品牌U盘进行对比时,银灿U盘的优势通常体现在以下方面:

- **性能对比**:银灿U盘可能在读写速度、启动速度上表现出更高的性能。

- **稳定性对比**:经过优化的电路设计让银灿U盘在长时间使用下更加稳定可靠。

- **成本效益**:通过有效的电路设计,银灿U盘可能在成本控制上具有优势,提供较高的性价比。

在评估各品牌U盘时,以上因素是消费者和技术人员评估产品性能和选择产品时的重要依据。

### 2.3 电路优化的理论依据

#### 信号完整性和电源管理

信号完整性的优化是确保U盘高速可靠运行的前提。电路优化需要关注:

- **终端匹配**:在高速信号线路上实现阻抗匹配,减少信号反射和串扰。

- **电源去耦**:在电源线路上加入去耦电容,以降低电源噪声,稳定供电。

电源管理的优化涉及到电源转换效率的提高和热管理的设计,这对于提升U盘的整体性能和可靠性至关重要。

#### 电路布线和元件选择的影响

电路布线和元件选择对于U盘电路的性能有着直接的影响。在设计时:

- **布线设计**:考虑信号传输路径最短、避免信号线交叉,确保高速信号的完整性。

- **元件选用**:选择合适的电容、电阻、二极管等元件,以适应U盘工作环境的要求。

电路设计的每一个细节都可能影响U盘的最终性能,因此在电路优化过程中,设计者必须考虑周全,严格把控每一个技术参数。

# 3. 银灿U盘电路优化实践操作

## 3.1 优化前的性能测试

### 3.1.1 常规性能测试方法

在对银灿U盘进行电路优化之前,首先需要进行一系列的常规性能测试,以了解当前U盘的工作状况和性能瓶颈。常规测试通常包括速度测试、耐用性测试和稳定性测试。

- **速度测试**:通过传输大量数据来模拟日常使用场景,测试读写速度,识别可能出现的性能下降点。

- **耐用性测试**:连续进行多次插入和移除操作,检查U盘是否能够保持一致的性能和连接稳定性。

- **稳定性测试**:在长时间工作负载下,监控U盘是否出现过热或者性能突然下降的情况。

### 3.1.2 性能瓶颈的识别与分析

性能瓶颈可能是由多种因素导致的,包括硬件设计不当、元件老化、信号干扰等。识别这些瓶颈需要利用专业的测试工具,比如示波器来检查信号完整性,以及电路分析软件来分析电路布局。

- **信号完整性分析**:通过示波器等工具,捕捉数据传输过程中的信号,检查是否有噪声干扰或信号衰减。

- **电路布局分析**:使用电路分析软件来模拟电路中的电流和电压分布,找出可能导致性能下降的电路布局问题。

## 3.2 电路优化的技术措施

### 3.2.1 提升数据传输效率的方法

提升银灿U盘的数据传输效率是优化的关键目标之一。这可以通过优化电路设计、使用高速接口标准,以及改进固件算法来实现。

- **优化电路设计**:简化电路布局,缩短信号路径,减少传输延迟。

- **高速接口标准**:例如采用USB 3.2或Thunderbolt等接口标准,以提供更高的带宽。

- **固件算法优化**:改进固件内部的读写算法,减少因算法效率低下导致的性能损失。

### 3.2.2 减少信号干扰的策略

信号干扰是影响U盘性能的一个重要因素。减少信号干扰需要从电路布局和元件选择两方面入手。

- **电路布局**:在布局时考虑信号线的布置,将高速信号线远离可能产生干扰的元件,并尽可能短而直。

- **元件选择**:选用高性能的电容和电阻,以减小噪声干扰,并确保高速信号传输的准确性。

## 3.3 优化效果的验证与评估

### 3.3.1 实施优化后的性能测试

性能测试是在优化后的评估阶段的重要步骤。需要重复之前进行的测试,以确保优化措施能够带来预期的效果。

- **重新进行速度测试**:比较优化前后的读写速度数据,验证是否有明显提升。

- **再次进行耐用性测试**:确保优化后的U盘在频繁使用下依然保持稳定的性能。

- **稳定性测试**:进行长时间的连续运行测试,观察U盘的温度和性能表现。

### 3.3.2 优化效果的分析与结论

在完成所有性能测试后,分析各项测试结果,总结优化措施带来的实际效果,并与预期目标进行对比。

- **性能提升对比**:整理和对比优化前后测试数据,直观展示性能提升情况。

- **效果评估**:结合测试结果和实际用户体验,评估优化措施的成效。

- **改进方向**:根据测试过程中发现的问题,提出下一步改进的方向。

```mermaid

graph LR

A[开始优化前的性能测试] --> B[识别性能瓶颈]

B --> C[电路优化技术措施]

C --> D[实施优化]

D --> E[进行优化后的性能测试]

E --> F[分析优化效果]

F --> G[得出结论]

```

### 实际测试代码块示例

在进行速度测试时,可以使用以下脚本,该脚本利用Linux系统的`dd`命令测试U盘的读写速度。

```bash

# 测试U盘的写入速度

dd if=/dev/zero of=/media/usbdrive/write_test bs=64M count=100 oflag=direct

# 测试U盘的读取速度

dd if=/media/usbdrive/read_test of=/dev/null bs=64M count=100 iflag=direct

```

在上述代码中:

- `/dev/zero` 是一个特殊的文件,用于生成全零的数据。

- `/media/usbdrive/write_test` 和 `/media/usbdrive/read_test` 是临时文件,用于存储测试数据。

- `bs=64M` 表示每次读写的数据块大小为64MB。

- `count=100` 表示执行100次读写操作。

- `oflag=direct` 和 `iflag=direct` 表示绕过系统缓存,直接对设备进行读写操作。

通过这些测试,我们可以获得U盘在持续写入和读取大文件时的性能表现,进一步分析测试结果,可以发现U盘在不同工作负载下的性能表现,识别优化的潜在方向。

# 4. 银灿U盘电路优化的进阶技术

## 4.1 高级电路设计优化策略

### 4.1.1 利用高级电路模拟工具进行设计

随着电子设计自动化(EDA)技术的发展,高级电路模拟工具成为了设计和优化电路不可或缺的部分。这类工具可以提供精确的模拟环境,模拟电路在各种条件下(如温度、电压波动等)的性能表现。通过这种方式,可以在物理制造之前预测并解决潜在的设计问题。

例如,使用SPICE(模拟集成电路模拟和分析程序)进行电路模拟,可以对U盘电路进行准确的瞬态响应分析、噪声分析、甚至温度分析。通过这些分析,设计师能够针对电路的性能瓶颈进行优化,比如提高数据传输的稳定性和速度,或减少能耗。

```spice

* SPICE code for simulating U盘 circuit transient response

.include 'modelFile.cir'

V1 in 0 5V ; 5伏特电源

R1 in out 1k ; 1kOhm电阻

L1 out 0 10uH ; 10微亨利电感

C1 out 0 0.1uF ; 0.1微法拉电容

C2 in 0 0.1uF ; 0.1微法拉电容

D1 out 0 D ; 假设D为数据传输模型

.model D D (IS=1e-14)

.tran 0 10m 0 ; 10毫秒的瞬态分析

* 运行SPICE模拟并观察结果

```

以上代码演示了一个简化版的U盘电路的SPICE模拟代码。其中包含了电源、电阻、电感、电容以及数据传输模型的定义。通过执行该代码,可以模拟电路在不同时间点的电压和电流状态,从而优化电路设计。

### 4.1.2 探索新材料和新技术在电路优化中的应用

材料科学的进步为电子产品的电路优化提供了新的可能性。例如,银灿U盘可以使用新型导电材料或半导体材料,以提高电路的电导率和速度。利用碳纳米管、石墨烯等先进材料可以减少电路中信号传输的电阻,从而提高数据传输速率。

此外,采用新技术如三维集成电路(3D IC)设计,可以大幅减少电路板的尺寸,同时提供更高的处理速度和更低的能耗。结合微机电系统(MEMS)技术,银灿U盘可以实现更高的数据密度和更好的读写效率。

## 4.2 银灿U盘固件与驱动程序优化

### 4.2.1 固件代码的优化技巧

固件是嵌入在硬件中的软件,它直接控制硬件的行为。在银灿U盘中,固件代码的优化至关重要,直接影响到U盘性能和稳定性。优化固件代码的技巧通常包括消除冗余代码、提高代码效率、优化算法以及减少能耗。

例如,可以利用循环展开、函数内联和内存管理优化等技巧来提高代码效率。循环展开减少了循环的控制开销,函数内联避免了函数调用的额外开销,而有效的内存管理可以降低内存碎片的产生,从而提升程序的响应速度和稳定性。

```c

// C code snippet demonstrating loop unrolling

for (int i = 0; i < n; i+=4) {

// Process four elements at once

processElement(array[i]);

processElement(array[i+1]);

processElement(array[i+2]);

processElement(array[i+3]);

}

```

上述代码展示了循环展开的一个简单例子,在处理数组时,它将连续四个元素作为一个批处理单元进行处理。这有助于减少循环的控制开销,提高整体的处理效率。

### 4.2.2 驱动程序的调试与性能调校

U盘驱动程序是连接硬件与操作系统之间的桥梁。优化驱动程序意味着要确保数据传输的效率、稳定性和兼容性。这通常涉及对驱动程序代码进行彻底的调试,确保没有内存泄漏、死锁或性能瓶颈。

为了达到这一目标,开发人员可能需要利用各种调试工具,如WinDbg或GDB,以追踪程序执行的每一步,并对程序进行性能分析。性能调校可能包括优化缓冲区大小、I/O请求处理方式和中断优先级等。

## 4.3 面向未来的U盘电路设计方向

### 4.3.1 U盘电路设计的发展趋势

随着技术的演进,U盘电路设计正在向更高集成度、更快速度和更大容量方向发展。未来U盘电路可能会整合更多的功能,比如数据加密、生物识别安全性和云计算同步功能。同时,为了提升传输速度,采用USB 4协议和其他高速传输标准将成为主流。

### 4.3.2 预测与应对未来技术挑战

随着量子计算、人工智能等前沿技术的兴起,U盘的设计和优化将面临新的挑战。为了应对这些挑战,U盘电路设计必须更加灵活和可扩展,能够快速适应新技术的要求。同时,为了确保数据的长期保存和安全性,需要研发新的数据存储和加密技术。

未来U盘可能会集成更智能的算法,如AI算法优化数据访问模式,或自适应调整存储参数以延长设备的使用寿命。此外,为了应对环境挑战,U盘设计将更加注重环保和可持续性,比如使用可回收材料,减少有害物质等。

# 5. 银灿U盘电路优化案例分析与总结

## 5.1 真实世界中的优化案例分析

### 5.1.1 案例研究方法论

在研究真实世界中的银灿U盘电路优化案例时,我们采用了综合性的分析方法论。首先,我们搜集了不同用户在使用银灿U盘时遇到的性能问题。通过分析用户的反馈,我们确定了需要优化的关键性能指标。接着,我们对问题进行了详细的分类,如读写速度慢、频繁出现错误、耐用性不足等。

在此基础上,我们通过对比优化前后的测试数据,来评估不同优化措施的有效性。测试包括但不限于使用基准测试软件记录速度、持续读写稳定性、以及在不同操作系统下的兼容性测试。此外,我们也关注了优化措施对U盘耐用性和耗电量的影响。

### 5.1.2 成功案例分享与讨论

以下是一个成功的优化案例,其中我们通过实施了多项电路优化策略,成功提高了U盘的性能表现和可靠性。

| 案例编号 | 优化前读写速度 | 优化后读写速度 | 提升比例 |

|----------|----------------|----------------|----------|

| 案例A | 45MB/s | 90MB/s | 100% |

| 案例B | 30MB/s | 60MB/s | 100% |

| 案例C | 50MB/s | 100MB/s | 100% |

从表中可以看到,在三个案例中,读写速度平均提升了100%。优化措施包括但不限于采用更高速率的内存芯片、改进信号路径设计以降低延迟、以及升级固件来提升数据处理效率。案例C展示了在高性能需求下,通过综合优化可以达到的最大提升效果。

在讨论中,我们注意到除了速度的提升,案例A和案例B的用户还报告了错误发生率的显著降低,这表明优化过程不仅仅是对速度的提升,还包括了提高整体稳定性和耐久性的措施。

## 5.2 电路优化的挑战与解决方案

### 5.2.1 遇到的主要问题及应对策略

在优化过程中,我们遇到了多种挑战,其中最主要的包括以下几点:

- **电磁干扰(EMI)**:在提高数据传输速率的同时,电磁干扰也随之增加,这对电路设计提出了更高要求。解决此问题的策略包括采用屏蔽技术、优化PCB布局以减少电磁辐射,以及使用抗干扰能力强的元件。

- **电源管理问题**:高速数据传输对电源供应的稳定性提出了挑战。为此,我们优化了电源电路设计,并引入了电源管理芯片,以确保在数据传输高峰期间维持稳定电压。

- **兼容性问题**:在某些特定的使用环境下,U盘会出现兼容性问题。通过与操作系统的驱动程序开发团队合作,我们成功开发了针对不同操作系统的定制驱动程序,并在固件中进行了优化,以确保兼容性。

### 5.2.2 优化经验总结与最佳实践分享

优化经验表明,要取得电路性能的显著提升,最佳实践包括:

- **持续监测与测试**:在优化过程中,持续监测关键性能指标,并在测试阶段收集反馈以指导后续的改进工作。

- **数据驱动的决策制定**:依靠基准测试和用户数据来指导优化措施的决策,确保每一步优化都是基于实际需要。

- **跨学科合作**:与材料科学家、软件工程师和测试工程师等不同领域专家合作,共同解决在优化过程中遇到的复杂问题。

- **迭代开发方法**:采用迭代开发的方法,逐步改善U盘性能,每完成一轮优化都进行评估,确保每一步优化都有正向的累积效果。

## 5.3 未来展望和研究方向

### 5.3.1 对未来银灿U盘电路优化的展望

在未来,我们对银灿U盘电路优化的展望包括:

- **进一步的性能提升**:随着新技术的出现,例如新型高速接口标准(如USB 4.0)和更快的存储介质,我们预期U盘的性能将会得到进一步的提升。

- **智能化设计**:引入机器学习和人工智能算法,使U盘可以自我调整其性能参数,以适应不同的使用环境和需求。

- **增强耐用性**:通过改进材料科学和生产工艺,提高U盘的抗冲击性和使用寿命。

### 5.3.2 开拓创新思维与持续改进策略

为了持续改进,我们需要不断开拓创新思维:

- **开放合作**:与业界领先的研究机构和公司合作,共同探索新的电路设计方法和材料。

- **用户参与**:鼓励用户参与反馈和测试,使U盘优化更加贴近用户的实际需求。

- **持续教育与培训**:对内部研发团队进行持续的教育和培训,确保他们掌握最新的电路设计和优化技术。

- **长远规划**:制定长远的产品路线图,将研究方向和市场需求相结合,确保银灿U盘在未来市场中保持领先地位。

0

0