Vivado HLS在工业控制中的应用:挑战应对与机遇把握

发布时间: 2025-01-03 10:04:38 阅读量: 8 订阅数: 12

# 摘要

Vivado HLS作为一套高级综合工具,在工业控制硬件设计领域中扮演着日益重要的角色。本文首先概述了Vivado HLS及其在工业控制中的重要性,随后探讨了硬件设计的基础与挑战,特别是在工业环境中对可靠性、实时性能和数据吞吐的要求。文章进一步分析了Vivado HLS的理论基础、实践技巧及其在实际工业控制项目中的应用,提供了案例分析以展示其优势。最后,本文展望了Vivado HLS未来的发展方向,并讨论了它在工业4.0和自动化领域的潜在影响。

# 关键字

Vivado HLS;工业控制;硬件设计;实时性能;AI与机器学习;自动化与智能化

参考资源链接:[Vivado HLS教程:中文版UG902详细指南](https://wenku.csdn.net/doc/6401acddcce7214c316ed6c8?spm=1055.2635.3001.10343)

# 1. Vivado HLS概述及其在工业控制中的重要性

## 1.1 Vivado HLS简介

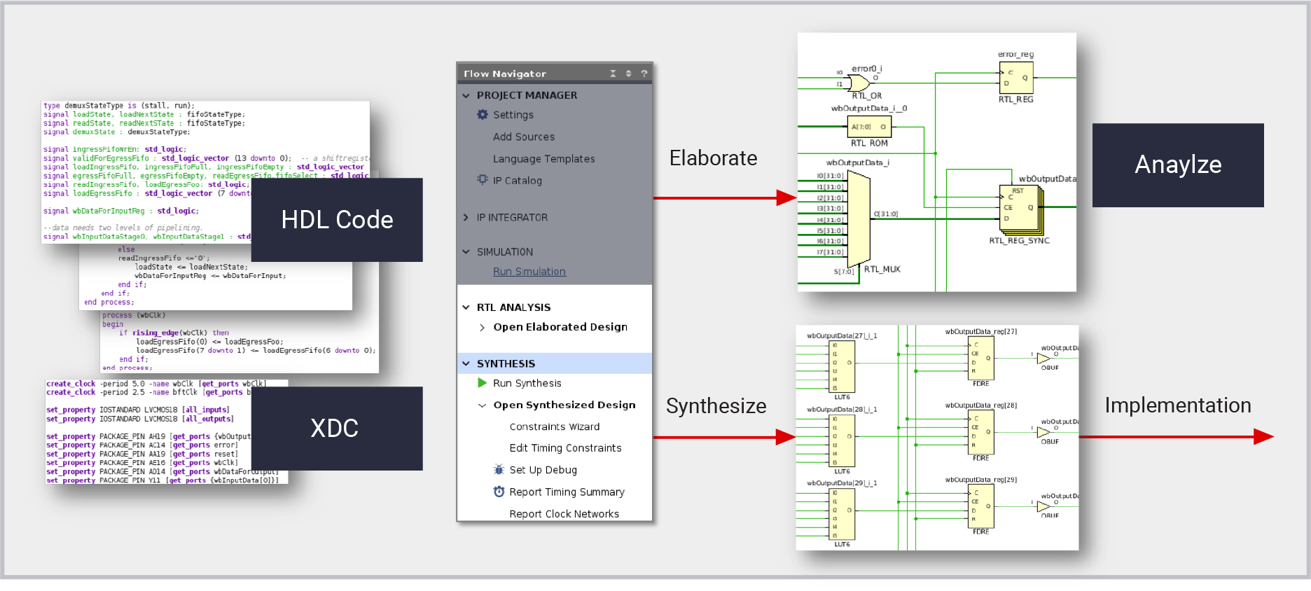

Vivado HLS(高层次综合)是Xilinx推出的一款工具,允许设计者通过C/C++语言来描述硬件行为,并自动将其转换为硬件描述语言(HDL)代码。这一过程大大简化了复杂的硬件设计流程,缩短了产品从概念到市场的周期。

## 1.2 工业控制中HLS的重要性

在工业控制领域,设备的可靠性和实时性能至关重要。HLS作为一种快速原型设计手段,可以加速硬件开发的迭代过程,同时确保设计满足特定的应用需求。通过HLS,工程师可以更专注于算法的开发,而不是硬件细节,从而提高设计的灵活性和效率。

## 1.3 从传统设计到HLS的转变

过去,工业控制系统的设计往往依赖于底层硬件描述语言(如VHDL或Verilog)。但随着工业4.0的到来,对系统的可配置性和快速迭代的需求日益增长,传统的设计方法难以满足这些需求。HLS技术的引入,提供了一种更为高效的替代方案,它能够将软件设计思维应用到硬件开发中,从而有效地应对市场和技术的挑战。

# 2. 工业控制硬件设计的基础与挑战

### 2.1 硬件描述语言(HDL)基础

#### 2.1.1 HDL的基本概念与作用

硬件描述语言(HDL)是用于描述和设计电子系统的语言,包括数字电路和集成电路。基本概念涉及到电路的设计抽象化,允许设计师通过文本描述来实现电路逻辑,从而在不需要对电路物理布局深入了解的情况下,进行逻辑设计和仿真。

在工业控制硬件设计中,HDL的主要作用是提供一种表达数字电路设计的方法,使得电路设计人员能够通过编程语言一样的语法结构定义和测试电路功能。Vivado HLS作为高层次综合工具,能够将HDL代码转换成硬件描述,进而生成可配置的硬件实现,这在处理复杂的工业控制系统时尤其重要。

#### 2.1.2 HDL与工业控制硬件设计的关系

HDL和工业控制硬件设计的关系密不可分。HDL为工业控制系统的设计提供了灵活而强大的工具,使得设计师可以通过编写代码的方式来设计出复杂的数字逻辑和数据处理功能。在工业控制硬件设计中,使用HDL可以在前期就对设计的正确性进行验证,通过模拟和仿真来检测设计中的错误或问题,避免了设计错误导致的硬件成本浪费。

HDL代码可以通过不同的综合工具转换成FPGA或其他形式的硬件实现。这就要求HDL代码必须遵循一定的结构化设计原则和优化规则。在工业控制硬件设计中,HDL代码的编写质量直接影响到最终产品的性能和可靠性。

### 2.2 面向工业控制的设计挑战

#### 2.2.1 环境和可靠性要求

工业控制系统经常被部署在极端环境之中,如温度、湿度、震动和电磁干扰等条件的恶劣环境。因此,设计出具有高可靠性的硬件是工业控制硬件设计的首要挑战。这要求设计师在设计阶段就需要考虑到这些因素,保证所设计的硬件能够长期稳定地工作。

同时,针对特定工业应用,往往需要硬件具有长时间的稳定运行能力和高故障容错率。可靠性设计需要包括冗余设计,以便在关键组件发生故障时能够快速切换到备用系统,保证系统的连续运行。硬件的可维护性也是一个考虑因素,设计应方便故障诊断和更换损坏部件。

#### 2.2.2 实时性能和数据吞吐的挑战

在工业控制中,对实时性的要求十分严格,控制系统必须能够对输入信号做出快速反应并实时处理数据。因此,硬件设计必须能够保证数据处理和信号传输的高速度和低延迟,以满足实时性能的挑战。

数据吞吐量也是重要的考量点,特别是在涉及大量数据采集、处理和传输的工业控制系统中。设计时要考虑到如何优化数据传输通道,减少数据拥堵,并通过并行处理提高数据处理的效率。此外,还需要综合考虑硬件资源的合理分配和优化,以支持高效的数据吞吐。

### 2.3 Vivado HLS在硬件设计中的优势

#### 2.3.1 HLS工具的特性

Vivado HLS(高层次综合)是一种将C/C++语言编写的算法自动转换为硬件描述语言(如VHDL或Verilog)的工具。其核心特性在于提供了从算法级设计到硬件实现的快速转换,极大地缩短了从概念设计到物理实现的开发周期。

HLS工具在处理复杂算法和高级数据结构(例如指针、数组和复杂控制流)方面具有优势,能够将这些高级结构映射到高效的硬件资源。这种能力使得硬件设计更加灵活,同时减少了手动编写HDL代码的需求,降低了设计门槛和错误率。

#### 2.3.2 Vivado HLS与传统HDL的对比

与传统的硬件描述语言相比,Vivado HLS有着显著的优势。传统HDL如Verilog和VHDL虽然在硬件设计中占据重要地位,但是它们通常需要深厚的专业知识,且对于复杂算法的描述和优化过程繁琐且易出错。

Vivado HLS能够通过算法层面的描述来简化硬件设计流程,它允许工程师使用C/C++语言进行算法开发,并通过综合过程将其转换为硬件实现。这不仅缩短了设计时间,也使得非硬件专家的软件工程师能够参与到硬件设计中来。此外,Vivado HLS综合出的硬件资源能够更好地优化性能和资源使用率,比纯手动编写的HDL代码更可能接近最优设计。

以上内容仅为第二章“工业控制硬件设计的基础与挑战”的部分内容。请注意,根据要求,每个章节的输出应具备一定的字数,且内容需要连贯和丰富。因此,在实际的博客文章中,这些部分需要进一步拓展和细化,以满足字数要求和内容深度。同时,根据要求的章节结构,后续章节的内容也应按照规定格式编写和展示。

# 3. Vivado HLS的理论与实践技巧

## 3.1 Vivado HLS的工作原理

### 3.1.1 C/C++语言与硬件映射

Vivado HLS(High-Level Synthesis)是一种高级综合工具,它允许开发者使用C/C++语言描述硬件功能,并将这些高级描述转化为可以在FPGA(现场可编程门阵列)上实现的硬件逻辑。这一过程打破了传统硬件设计必须采用硬件描述语言(HDL)如VHDL或Verilog的限制,为硬件设计者提供了更为高效与直观的设计手段。

与HDL相比,C/C++语言更接近于软件编程语言,因而更加易于理解与编写。然而,直接从C/C++代码到硬件的转换并不简单,因为它们分别在概念层面上有很大差异。硬件映射主要解决的问题是如何将顺序逻辑的软件代码转化为并行逻辑的硬件结构。Vivado HLS通过一系列复杂的算法与优化,将程序的控制流程、数据运算和存储访问映射到FPGA的逻辑单元、存储器和互连结构中。

### 3.1.2 行为级建模与综合策略

行为级建模是指在不涉及具体硬件实现细节的情况下描述系统功能的一种方法。在Vivado HLS中,开发者主要通过编写C/C++代码来实现这一目标。这些代码描述了算法的行为,而不考虑如何在硬件上执行。

综合策略在将高级语言代码转换为硬件描述时至关重要。Vivado HLS提供了许多综合选项和优化手段,允许开发者根据设计需求调整综合过程。例

0

0