【测试与验证绝招】:确保Multisim中D触发器电路的精确性

发布时间: 2024-12-02 01:49:55 阅读量: 59 订阅数: 32

参考资源链接:[Multisim数电仿真:D触发器的功能与应用解析](https://wenku.csdn.net/doc/5wh647dd6h?spm=1055.2635.3001.10343)

# 1. Multisim中D触发器电路的理论基础

## 1.1 D触发器电路的定义和工作原理

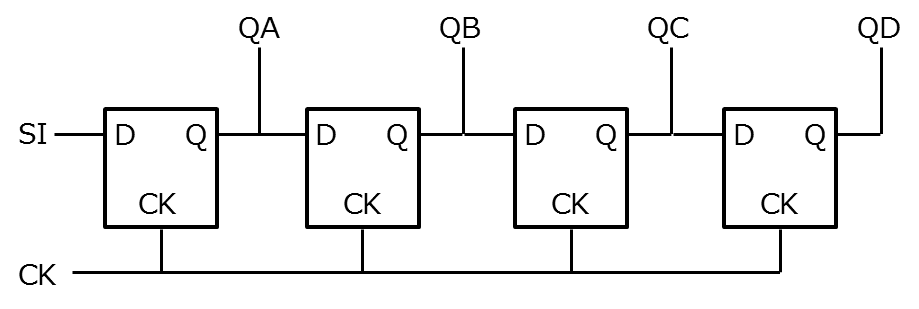

D触发器,全称数据触发器(Data Flip-Flop),是数字电路中常用的一种时序逻辑电路元件。它的特点是,当在时钟信号的上升沿到来时,输入端D的数据会被“记忆”并输出到Q端,而Q端的输出保持直到下一个时钟信号的上升沿到来。

D触发器的工作原理可以概括为:在时钟信号的上升沿,如果输入端D为高电平,则输出端Q变为高电平;如果输入端D为低电平,则输出端Q变为低电平。这个过程是可逆的,即可以通过改变输入端D的状态来改变输出端Q的状态。

## 1.2 D触发器的种类和特性

在Multisim中,D触发器主要有两类:边沿触发D触发器和电平触发D触发器。边沿触发D触发器的特点是只在时钟信号的上升沿或下降沿发生变化,电平触发D触发器则在时钟信号为高电平或低电平时发生变化。

D触发器的主要特性包括:时序性(只在特定时刻改变状态)、记忆性(能够记住输入端的状态)和稳定性和抗干扰能力。在设计D触发器电路时,我们需要充分考虑到这些特性,以确保电路的正常工作。

# 2. D触发器电路的设计与仿真

## 2.1 Multisim中D触发器的基本操作

### 2.1.1 D触发器组件的引入和配置

在Multisim中设计D触发器电路首先需要熟悉其基本组件的引入和配置。D触发器是数字电路中的一种基本组件,用以实现数据的存储和延时功能。在Multisim软件中,你可以通过以下步骤引入D触发器组件:

1. 打开Multisim软件。

2. 在组件库面板中,找到“Basic”选项卡,并选择“Flip-Flops”子选项卡。

3. 从中选择D型触发器(D Flip-Flop),拖拽到工作区即可。

配置D触发器时,你需要注意其引脚功能。D触发器通常包括以下几个引脚:

- D (Data):数据输入端。

- CLK (Clock):时钟输入端。

- Q 和 Q'(或 Q̅):输出端和反相输出端。

- PRE (Preset) 和 CLR (Clear):置位和复位端(可选,依据具体触发器型号而定)。

### 2.1.2 D触发器的工作原理和特性

D触发器工作原理是,在每个时钟上升沿到来时,数据输入端D上的电平被转移到输出端Q,并在下一个时钟上升沿到来之前保持不变。若具有预置和清除功能,则在PRE端置高电平会使输出Q置高电平,CLR端置高电平会使输出Q置低电平。

在Multisim中进行仿真时,D触发器的这些特性可以方便地通过仿真波形来观察。为了理解其工作特性,你需要:

1. 在D触发器的D输入端施加逻辑电平信号。

2. 设置时钟信号到CLK输入端。

3. 观察Q和Q'输出端的波形变化。

下表总结了D触发器的一些关键特性:

| 特性 | 描述 |

| --- | --- |

| 同步 | 数据的改变发生在时钟信号的上升沿 |

| 存储 | 时钟上升沿后,D端的数据被锁存到Q端 |

| 置位和复位 | 可通过PRE和CLR端在任意时刻改变输出状态 |

| 无竞争 | 输出端状态变化不会相互影响 |

通过下图的示例电路,你可以观察到D触发器的工作原理:

```mermaid

flowchart LR

A[D Input] -->|Data| B[CLK]

C[CLK] -->|Clock| D[D Flip-Flop]

D -->|Output| E[Q]

D -->|Inverse Output| F[Q']

G[Preset] -->|Set HIGH| H[Q HIGH]

I[Clear] -->|Set HIGH| J[Q LOW]

```

### 代码块示例和逻辑分析

一个基本的D触发器仿真测试代码如下:

```verilog

module d_flip_flop_test;

reg d, clk;

wire q;

d_flip_flop dff1(.D(d), .CLK(clk), .Q(q));

initial begin

// 初始化输入

d = 0; clk = 0;

forever #5 clk = ~clk; // 产生时钟信号

end

initial begin

// 时序仿真过程

#10 d = 1;

#20 d = 0;

#20 d = 1;

#20 $stop; // 停止仿真

end

endmodule

// D触发器模块

module d_flip_flop(input D, input CLK, output reg Q);

always @(posedge CLK)

Q <= D;

endmodule

```

在这段Verilog代码中,模块`d_flip_flop_test`用于设置D触发器的输入信号并产生时钟信号,而模块`d_flip_flop`则实现了D触发器的逻辑。`always @(posedge CLK)`块确保了在时钟上升沿时对输出Q进行赋值。

## 2.2 设计模拟电路时的注意事项

### 2.2.1 理解时序电路的基本概念

在设计模拟电路时,尤其是在使用D触发器这样的时序元件时,理解时序电路的基本概念至关重要。时序电路能够根据输入信号的变化以及内部状态的变化产生输出,其工作依赖于输入信号的时间顺序。

以下是设计时序电路时应考虑的几个关键点:

1. **时间依赖性**:时序电路的输出不仅依赖于当前的输入,还依赖于之前的状态或历史。

2. **状态转换**:电路中的状态转换应当是可预测的,并且状态的改变通常发生在时钟信号的触发下。

3. **初始化状态**:在模拟开始前应确保电路有一个明确的初始化状态,以避免不确定的行为。

在设计D触发器电路时,你应确保:

- 时钟信号的清洁和稳定,避免毛刺影响电路工作。

- 输入信号和输出信号的同步,确保数据的有效传输。

- 电路设计中已包含必要的去抖动逻辑,以处理机械开关带来的信号抖动。

### 2.2.2 考虑电路中可能出现的问题和解决办法

在设计和仿真D触发器电路时,可能出现的问题及其解决办法需要提前考虑:

- **时钟偏斜(Clock Skew)**:多个时钟信号到达各触发器的时间不一致,这可能导致数据在寄存器间传输错误。解决办法是使用统一的时钟源,并优化信号布线路径。

- **建立时间和保持时间违例**:若D输入在时钟上升沿附近不稳定,可能会导致输出不稳定。为避免这种情况,应当确保D信号在时钟边沿到来之前和之后一定时间内

0

0