【中断系统专家解读】:锐能微7302中断机制深入解析

发布时间: 2025-01-08 21:13:03 阅读量: 22 订阅数: 14

锐能微 7302最新手册

# 摘要

中断系统是现代微处理器架构中的核心组成部分,对于实现高效、实时的任务处理至关重要。本文首先介绍中断系统的基本理论,包括中断的定义、分类、管理流程及与微处理器的交互。随后,针对锐能微7302微架构的中断机制进行深入解析,探讨其控制单元的结构、优先级管理、响应和返回流程。文章接着阐述了中断机制的编程实践,涵盖环境搭建、中断处理程序设计及性能调优。此外,本文还分析了7302中断机制在实时系统、多核处理器环境及现代操作系统中的应用,并展望了中断技术的发展趋势和潜在改进方向,提出了一系列优化策略和应用前景。通过对7302中断机制的全面探讨,本文旨在为系统设计师和开发者提供有价值的参考和指导。

# 关键字

中断系统;微架构;中断管理;中断控制单元;实时系统;多核处理器

参考资源链接:[锐能微RN7302三相多功能电能计量芯片最新手册详解](https://wenku.csdn.net/doc/o4v9ijsuga?spm=1055.2635.3001.10343)

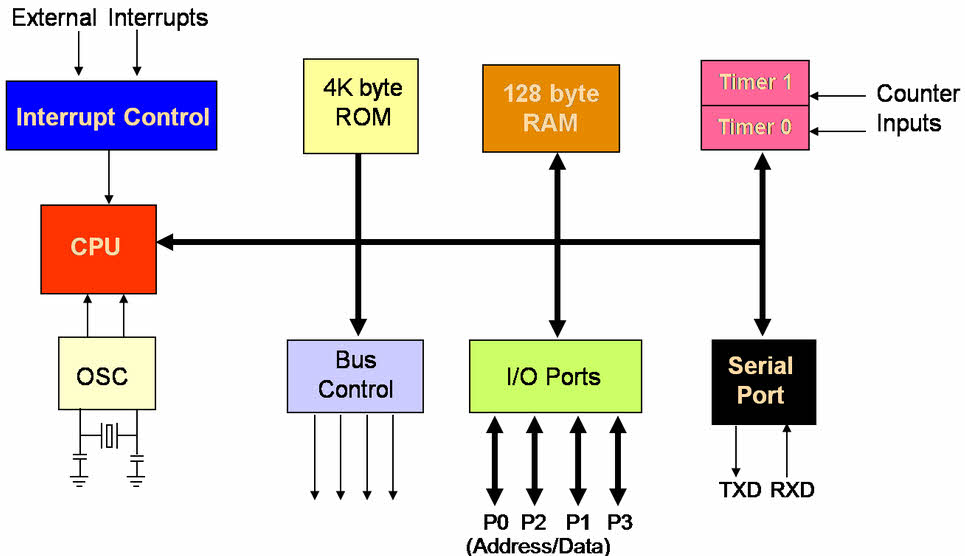

# 1. 中断系统基础与7302微架构概述

中断系统是现代微处理器和操作系统中不可或缺的一部分,它允许处理器在执行主程序时,能够及时响应外部或内部事件。在本章节中,我们将首先探讨中断系统的基础知识,随后将目光聚焦在锐能微7302微架构上,对它特有的中断机制进行初步的介绍。

## 1.1 中断系统概述

中断系统的工作原理可以比喻为日常生活中的电话接打过程。当电话铃响时,我们暂时中断手头的工作,接电话进行交流,之后再返回先前的工作状态。同理,在计算机系统中,当中断信号触发时,处理器会暂停当前任务,转而处理更高优先级的任务或应对外部事件,待处理完毕后,再恢复到被中断的任务。

## 1.2 7302微架构简介

锐能微7302微架构是针对高性能计算领域而设计的处理器架构。它的中断机制是它的一大亮点,7302提供了高效率的中断处理能力,其设计允许系统快速响应各种复杂的中断场景。这为实时系统、多核处理器环境以及现代操作系统的高效运行提供了强有力的硬件支持。

在后续章节中,我们将深入探讨中断系统的理论基础,分析7302微架构下的中断控制单元结构,以及中断机制在实际应用中的表现。我们也会针对编程实践和性能优化给出详细说明,并展望未来中断技术的发展趋势。

# 2. 中断系统的理论基础

## 2.1 中断的基本概念

### 2.1.1 中断的定义和作用

中断是一种使处理器能够响应外部事件的技术。当中断发生时,处理器将暂停当前的工作流程,转而处理一个紧急任务,完成后返回原先的任务继续执行。这种机制对于任何需要及时响应外部事件的系统至关重要,如实时系统、多任务操作系统等。

中断的作用体现在以下几个方面:

- **提高了CPU的利用率**:允许CPU在等待I/O操作完成的同时执行其他任务。

- **增强了系统的响应性**:对高优先级任务做出快速响应,如键盘输入或网络数据包。

- **支持多任务并发执行**:操作系统通过中断来切换不同任务的执行,实现并行工作。

### 2.1.2 中断的分类

中断按其来源可以分为两大类:硬件中断和软件中断。

**硬件中断**通常由硬件设备触发,如键盘、鼠标或网络接口卡。硬件中断又分为可屏蔽中断(Maskable Interrupts)和非可屏蔽中断(Non-Maskable Interrupts, NMI)。可屏蔽中断可以通过编程被暂时忽略,而非可屏蔽中断通常用于表示系统级的紧急情况,如电源故障或硬件错误。

**软件中断**是由执行特定的软件指令(如系统调用)触发的。软件中断允许程序请求服务或通知操作系统发生了一些需要处理的情况。在x86架构中,如`int`指令就是软件中断的一个例子。

## 2.2 中断管理与处理流程

### 2.2.1 中断向量表和中断服务程序

当中断发生时,处理器通过一个预先定义的数据结构——中断向量表来找到并执行相应的中断服务程序(Interrupt Service Routine, ISR)。中断向量表包含指向中断服务程序入口的指针,每个中断都有一个唯一的向量,关联一个特定的中断号。

中断向量表通常位于内存的特定位置,操作系统在启动时初始化这个表,并可能根据需要动态地添加或替换向量表项。中断服务程序是实际处理中断的代码段,通常由设备驱动程序实现。

### 2.2.2 中断优先级和嵌套

为了处理多个同时发生的中断,中断系统必须具有优先级管理机制。优先级决定了哪个中断应该首先被处理。中断优先级通常在硬件层面设定,也可以通过编程在软件中进行调整。

当中断发生时,如果当前正在处理一个低优先级中断,高优先级的中断可以打断它,这种处理机制称为中断嵌套。为了支持嵌套,操作系统通常需要在中断服务程序中保存和恢复中断状态,以确保中断处理过程的正确性。

## 2.3 中断与微处理器的交互

### 2.3.1 硬件中断信号的处理

硬件中断信号通过中断控制器传送到微处理器。中断控制器的主要任务是接收来自不同硬件设备的中断请求(Interrupt Request, IRQ),并将其传递给CPU。它还会处理多个设备同时请求中断的情况,通常是通过硬件优先级或轮询机制来决定哪个设备的中断请求应被优先处理。

微处理器内部有一个中断使能寄存器(Interrupt Enable Register),它控制哪些中断可以被CPU接受。当一个中断发生时,CPU会检查这个寄存器,并根据优先级和使能状态决定是否响应中断。

### 2.3.2 中断请求和确认机制

当中断被触发时,硬件中断信号会被发送到处理器。中断信号会通过中断请求线(IRQ)发送到CPU的中断控制器。处理器通过查询中断控制器的状态来确认中断源。

一旦CPU接受了一个中断请求,它会完成当前正在执行的指令,并开始执行中断处理流程。在x86架构中,这通常意味着CPU会跳转到一个预定义的中断向量,并开始执行相应的中断服务例程。在处理完中断后,处理器会返回到被中断的指令继续执行。

# 3. 锐能微7302中断机制详解

## 3.1 7302中断控制单元的结构

中断控制单元是微处理器中断系统的核心部分,负责接收中断信号、确定中断优先级、选择中断服务程序执行以及控制中断的启用或屏蔽等。理解7302中断控制单元的结构,对于掌握其中断机制至关重要。

### 3.1.1 中断控制器的主要组件

中断控制器由多个组件构成,包括中断请求寄存器(IRR)、中断屏蔽寄存器(IMR)、中断服务寄存器(ISR)以及优先级解析器等。

- **中断请求寄存器(IRR)**:当外部设备发出中断请求时,中断请求寄存器记录哪些中断源是活跃的。

- **中断屏蔽寄存器(IMR)**:用于控制哪些中断信号被屏蔽,也就是不允许某些特定中断打断当前执行的操作。

- **中断服务寄存器(ISR)**:记录当前正在服务的中断,避免嵌套的中断请求导致的混乱。

优先级解析器则是决定哪一个中断源可以优先获得处理器的响应。

### 3.1.2 中断源和中断目标的映射关系

7302中断控制单元支持动态优先级和固定优先级两种模式,允许中断源与中断向量表中的目标进行灵活的映射。

- **动态优先级模式**:在该模式下,中断的优先级可以动态调整,优先级较高的中断可以抢占正在服务的低优先级中断。

- **固定优先级模

0

0