Allegro PCB 16.3新手必备:5个步骤精通约束设置

发布时间: 2025-01-04 17:01:17 阅读量: 8 订阅数: 17

034-基于AT89C52的矩阵键盘扫描proteus仿真设计.rar

# 摘要

本文深入探讨了Allegro PCB 16.3在电子设计中的约束设置,涵盖了从基础理论到高级应用的全过程。文章首先介绍了约束设置的目的与类型,并阐述了其在PCB设计中的重要作用。随后,通过理论与实践相结合的方式,详细说明了如何在Allegro PCB 16.3中配置电气约束和物理约束,包括信号完整性要求、电气规则、组件间距、布局规则、布线宽度和层叠结构的设计。此外,本文还探讨了设计规则检查(DRC)的执行和反馈调整,动态约束的使用,多板级设计约束管理,以及如何利用约束进行自动化设计。最后,通过具体案例分析,展示了从零开始设置约束到优化现有设计的完整流程,为读者提供了实用的参考和指导。

# 关键字

Allegro PCB 16.3;约束设置;电气约束;物理约束;设计规则检查(DRC);自动化设计

参考资源链接:[Allegro 16.3约束设置详解:线宽、线距与差分线配置](https://wenku.csdn.net/doc/33bungmauc?spm=1055.2635.3001.10343)

# 1. Allegro PCB 16.3概述

在当今电子设计自动化(EDA)领域中,Allegro PCB 16.3作为一款强大的PCB设计工具,为工程师们提供了从设计到制造的全流程支持。其拥有高度集成的环境,支持复杂的多层和高速信号设计,因此在高性能电路板设计中得到了广泛应用。

Allegro PCB 16.3的功能丰富,不仅包含了基本的原理图捕获与编辑、PCB布局与布线,还包括了高级的信号完整性和功率完整性分析功能。除此之外,该版本增强了对高密度互连(HDI)设计的优化能力,同时强化了与制造环节的衔接,从而提高设计的准确性和可靠性。

为充分利用Allegro PCB 16.3的全部潜力,设计者需掌握其提供的约束设置功能。约束设置是确保设计符合电气与物理要求的关键步骤,而接下来的章节将详细介绍约束设置的理论基础与实践操作,以及如何在Allegro PCB 16.3中进行高效的约束管理。

# 2. 约束设置的理论基础

### 2.1 约束设置的定义和目的

在PCB设计中,约束设置是确保设计达到既定性能标准的关键步骤。设计师通过定义一系列的参数,来控制电路板上各个组件的布局、电气连接以及信号完整性。正确地设置约束有助于提高设计的可靠性,减少设计迭代次数,缩短产品上市时间。

#### 2.1.1 约束设置在PCB设计中的作用

约束设置对PCB设计至关重要。它可以保证电路板在物理布局上满足产品性能要求。例如,时钟信号可能需要特殊的布线策略,以避免由于布线延迟导致的时序问题。此外,约束还帮助设计师在布局中实现信号的正确排序和分组,防止信号之间的串扰和干扰。

#### 2.1.2 约束类型及其重要性

约束分为电气约束和物理约束两大类。电气约束关注的是信号完整性、电源分配、时序等问题。而物理约束则关注组件间距、布局、布线宽度、层叠结构等方面。理解不同类型的约束对于实现一个高效、可靠的设计是必要的。

### 2.2 约束设置的基本原则

#### 2.2.1 理解电气约束和物理约束

电气约束通常包括信号的阻抗匹配、端接策略、信号的上升/下降时间等。物理约束则关注布局中元件的位置、布线的路径和宽度等。理解这些约束的含义及其对设计的影响是设计师必须具备的技能。

#### 2.2.2 设计规则检查(DRC)与约束设置的关系

设计规则检查(DRC)是PCB设计过程中的一个验证步骤,确保设计满足一系列预先设定的规则。约束设置在很大程度上决定了DRC检查是否能顺利通过。DRC结果可以指导设计师调整约束,以符合设计要求和生产标准。

通过本章节的介绍,我们可以看到约束设置在PCB设计中的重要性,以及电气与物理约束之间的区别。下一章节将详细介绍如何在Allegro PCB 16.3中配置这些约束,并进行实际操作。

# 3. Allegro PCB 16.3约束设置实践

## 3.1 配置电气约束

### 3.1.1 设置信号完整性要求

在现代电子设计中,信号完整性(Signal Integrity,简称SI)是确保电路按照预期工作的一个关键因素。对于高速和高密度的PCB设计,信号完整性管理显得尤为重要。在Allegro PCB 16.3中,配置电气约束需要考虑以下几个方面:

- **阻抗控制**:确保布线的阻抗与所需阻抗相匹配,以防止信号反射和电磁干扰。

- **时序约束**:对于数字信号,必须确保信号在规定的时间内传输,满足数据传输速率要求。

- **串扰限制**:减少邻近信号线之间的相互影响,特别是在高速运行的条件下。

通过在Allegro PCB 16.3中设置电气规则,设计师可以详细定义上述要求,确保PCB设计达到预期的性能。

```mermaid

flowchart LR

A[开始设计] --> B[创建项目]

B --> C[定义信号完整性约束]

C --> D[设定阻抗规则]

C --> E[设置时序规则]

C --> F[设定串扰限制]

D --> G[执行DRC]

E --> G

F --> G

G --> H[分析结果并优化]

H --> I[完成设计]

```

### 3.1.2 创建和应用电气规则

创建电气规则是确保信号完整性和避免电气问题的第一步。在Allegro中,可以通过以下步骤创建和应用电气规则:

1. 打开电气规则设置界面(Design –> Electrical Rules)。

2. 点击“New Rule”创建新的规则。

3. 根据需要选择规则类型,例如“Net Class”以设置特定信号类别的电气参数。

4. 定义规则的具体参数,如电压电平、电流负载、最大容差等。

5. 将规则应用于特定的网络或整个设计。

6. 使用“Design Check”功能执行设计规则检查(DRC),确保电气规则的正确性。

```mermaid

classDiagram

class Rule {

<<interface>>

+type

+parameters

+applyTo()

}

class SignalIntegrityRule {

+impedanceConstraint()

+timingConstraint()

+crosstalkConstraint()

}

class DRC {

+run()

+interpretResults()

}

Rule --> SignalIntegrityRule : implements

SignalIntegrityRule --> DRC : utilized for

```

## 3.2 配置物理约束

### 3.2.1 设定组件间距和布局规则

组件的物理布局对于整个PCB的性能同样至关重要。合理的组件间距可以预防由于过热导致的电路故障,同时也有助于信号的正确传输。在Allegro PCB 16.3中,布局规则的设置通常包括以下步骤:

1. 确定组件的热分布和散热要求,合理分配组件位置。

2. 为不同类型的组件设置最小间距,比如IC和高功率元件。

3. 利用“布局向导”或者手动放置组件,确保布局的合理性。

4. 利用“布局规则检查(ERC)”来验证布局是否符合预设的规则。

### 3.2.2 规划布线宽度和层叠结构

布线宽度直接影响到电路的电流承载能力和信号损耗。合理的层叠结构设计能够减少信号串扰,并提高EMI(电磁干扰)性能。在规划布线宽度和层叠结构时,需要考虑以下因素:

- **布线宽度**:根据信号的电流要求和阻抗控制要求来确定。

- **层叠结构**:根据设计的复杂性、成本、重量以及热管理需求来决定。

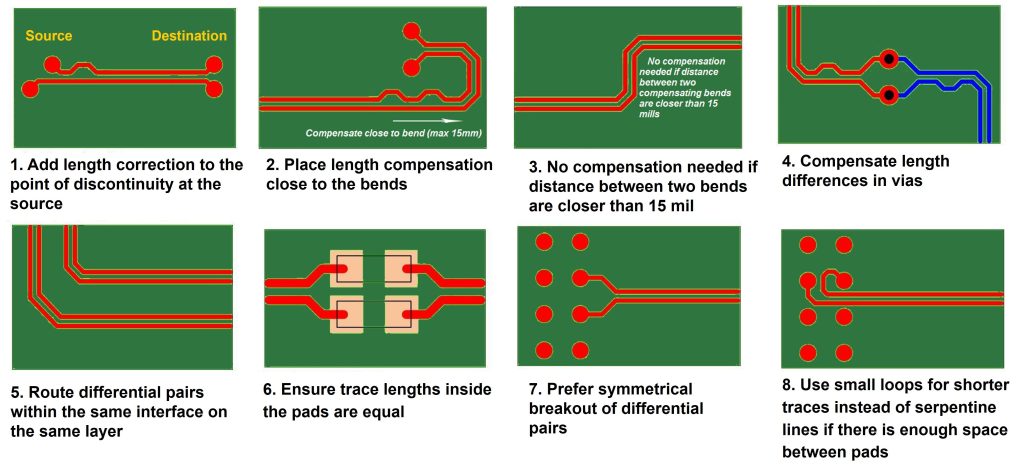

- **布线策略**:高速信号需要特别的布线技巧,如微带线、带状线以及差分信号对布线。

在Allegro PCB 16.3中,可以通过“布线向导”或者手动编辑的方式来完成布线宽度的设定。层叠结构的规划则需要利用“层叠管理器”来进行。

## 3.3 进行设计规则检查(DRC)

### 3.3.1 执行DRC并解读结果

设计规则检查(Design Rule Check,简称DRC)是确保PCB设计满足所有物理和电气约束的关键步骤。在Allegro PCB 16.3中执行DRC的流程如下:

1. 点击工具栏中的“DRC”按钮或者使用快捷键“Shift + F8”启动规则检查。

2. 选择需要执行的规则集,如电气规则、物理规则等。

3. 启动检查过程,系统将自动扫描设计中的违规之处。

4. 检查完成后,查看违规信息列表,并分析违规的具体原因。

```mermaid

sequenceDiagram

participant U as User

participant A as Allegro PCB 16.3

U ->> A: Initiate DRC

A ->> A: Run DRC Checks

A ->> U: Display Violation List

U ->> A: Review and Analyze Violations

```

### 3.3.2 根据DRC反馈调整设计

在分析了DRC的结果后,设计人员需要根据反馈的信息对PCB设计进行相应的调整。调整的过程可能包括:

- 修改元件布局,改善散热和信号路径。

- 调整布线策略,如增加布线宽度,改变布线层,或者优化布线路径。

- 更新层叠结构,以适应更复杂的信号要求或热管理需要。

- 根据电气规则的反馈,调整信号完整性相关参数。

这个过程可能会重复多次,直到所有的DRC反馈都得到解决为止。

在接下来的章节中,我们会探索Allegro PCB 16.3的高级应用,并通过案例分析来展示如何应用本章内容解决实际问题。

# 4. 约束设置的高级应用

在前一章节中,我们已经深入探讨了Allegro PCB 16.3中约束设置的基本配置和应用。本章将进一步深入到约束设置的高级应用领域,探索动态约束的使用、多板级设计中的约束管理,以及如何利用约束进行自动化设计,旨在提供更灵活、高效的设计流程。

## 4.1 动态约束的使用

动态约束是高级约束管理中的重要组成部分,其灵活的特性能够应对复杂多变的设计需求。动态约束的使用需要理解其概念和实现技巧。

### 4.1.1 理解动态约束的概念

动态约束与静态约束相对,它允许约束条件根据设计环境的变化而自动调整。在Allegro PCB中,动态约束可以通过条件表达式来定义,以适应不同的设计状态和规则变化。比如,根据布线密度自动调整走线宽度,或者根据特定的信号类型改变阻抗控制值。

动态约束通常用于高级的设计场景,例如高速设计中对于特定信号的特殊处理。动态约束的优势在于其能够减少手动修改的工作量,同时保持设计的灵活性。

### 4.1.2 实现动态约束的技巧与示例

实现动态约束涉及多个步骤,包括定义动态条件、编写相应的约束表达式和规则验证。下面的示例将展示如何通过Allegro PCB的约束管理器设置一个简单的动态约束。

#### 示例:动态布线宽度约束

假设我们需要根据不同的布线区域动态地调整布线宽度。

1. 打开Allegro PCB约束管理器。

2. 选择“Constrains”菜单,然后“Route Width”进入布线宽度设置。

3. 在“New”中创建一个新的布线宽度规则。

4. 在“Expression”字段中输入以下动态表达式来定义布线宽度:

```

(set 'width (if (> 2.0 (get_distance_from_axis cline_axis "Y")) 5.0 10.0))

```

5. 这个表达式检查了走线与其Y轴的水平距离,根据距离动态设置宽度值。当距离小于或等于2.0时,设置宽度为5.0,否则为10.0。

6. 应用规则并保存。

通过这种方式,设计师可以根据实际的布线需求灵活地调整规则,而无需在设计发生变化时重新手动设置约束。

## 4.2 多板级设计中的约束管理

在多板级设计中,每个板可能有不同的约束设置。此时,约束管理的重要性不言而喻,需要掌握如何在不同板级设计之间维护和同步约束。

### 4.2.1 多板级设计约束设置要点

在多板级设计中,各板可能包含不同的组件和不同的布线要求。为保证整个系统的完整性和功能的一致性,以下是几个关键的约束设置要点:

- **统一命名规则**:在开始设计之前,应确定跨板组件和信号的命名规则,以便在整个设计中保持一致性。

- **模块化约束**:设计时将常用的约束定义为模块,可以方便地在多个板之间重复使用。

- **全局与局部约束的平衡**:某些约束需要在全局范围内保持一致(如电压和电源要求),而局部约束则根据单个板的具体需求进行设置。

### 4.2.2 维护和同步不同板级设计的约束

随着项目进展,设计更改是常见的情况,因此维护和同步不同板级设计的约束至关重要。可以采取以下措施:

- **使用版本控制系统**:通过版本控制系统跟踪和管理设计文件的更改,确保所有板级设计文件同步更新。

- **约束同步脚本**:编写自动化脚本,能够在板级设计之间同步更新约束规则。

- **中央约束库**:建立一个中央约束库,所有的板级设计都从这个库中读取约束规则,一旦中央库更新,所有依赖该库的设计也自动更新。

## 4.3 利用约束进行自动化设计

自动化设计流程能显著提高设计效率和准确性,借助约束的自定义和模板,可以实现设计流程的自动化。

### 4.3.1 自动化设计流程简介

自动化设计流程是通过预先定义好的规则和参数来执行设计任务,减少手动操作,保证设计的一致性。通过合理地利用约束,自动化流程可以分为以下几个步骤:

1. **定义设计需求**:明确设计目标和约束条件。

2. **创建规则模板**:根据设计需求创建约束规则模板。

3. **实施自动化脚本**:编写脚本来实现约束规则的自动应用。

4. **设计验证**:通过自动化的DRC和ERC(电气规则检查)验证设计。

5. **迭代优化**:根据验证结果进行必要的调整,然后迭代设计过程。

### 4.3.2 创建自定义约束集和模板

创建自定义约束集和模板是自动化设计的关键,下面将介绍如何创建约束模板,并通过示例演示其应用。

#### 示例:创建约束模板

1. 打开Allegro PCB约束管理器。

2. 选择“Create Template”来定义新的约束模板。

3. 命名模板,并根据项目需求选择约束类型,如走线宽度、布线优先级、阻抗控制等。

4. 在模板中定义约束规则,比如:

```

Rule: Min Width

Type: Width

Minimum: 4 mil

```

5. 保存模板,以便在多个项目中重用。

通过使用这个模板,设计师可以在不同的项目中快速应用相同的约束规则,简化设计流程并减少错误。

综上所述,高级约束应用为PCB设计提供了更高的灵活性和效率。从动态约束的设置到多板级设计的约束同步,再到自动化设计流程的实现,每一步都是对设计能力的提升。通过本章节的介绍,设计师可以掌握更高级的约束管理技巧,以适应日益复杂的设计需求。

# 5. 约束设置案例分析

## 5.1 案例研究:从零开始设置约束

### 5.1.1 创建新项目并设置基础约束

在深入分析案例之前,首先需要明确约束设置对于一个新PCB项目的重要性。创建一个新项目时,及时有效地建立约束能够确保设计符合预期的性能标准,并且减少后期修改的需求。基础约束的设置包括定义信号完整性规则、电气规则、组件间距以及布线规则等。

创建新项目时,首先需要确定设计的需求,例如信号的速度、电流承载能力、电源需求等。根据这些需求,我们可以开始设置以下基础约束:

1. **定义信号完整性要求**:在Allegro中,我们需要定义信号的速度要求,并且根据信号类型(如时钟、高速、低速等)设置不同的约束。

```bash

# 示例代码块 - 设置信号完整性要求

set_termprop -class net -prop maxDelay 10 [find net *CLK*]

set_termprop -class net -prop minDelay 1 [find net *CLK*]

```

以上代码块将时钟信号的最大和最小延迟分别设置为10纳秒和1纳秒,确保信号能够准时到达目的地。

2. **创建和应用电气规则**:在Allegro PCB Editor中,通过约束管理器(Constraint Manager)创建电气规则,并将其应用于特定的网络或网络集。

```bash

# 示例代码块 - 创建电气规则

create电气规则规则 -class net -name "HighSpeedRule" -maxDelay 10 -minDelay 1

```

此命令创建了一个名为"HighSpeedRule"的新电气规则,最大和最小延迟分别为10纳秒和1纳秒。

3. **设定组件间距和布局规则**:组件间距是基于电路板的热管理、机械强度和组装便利性来确定的。我们可以使用Allegro PCB Editor的布局编辑器(Layout Editor)来直观地设置和调整间距。

```bash

# 示例代码块 - 设定组件间距

set_component_space -comp [find refdes U1] -value 100 mil

```

该代码示例将组件U1的间距设置为100mil。

4. **规划布线宽度和层叠结构**:布线宽度与电流承载能力直接相关,需要根据电路板的电流需求进行设置。同时,层叠结构的规划需要考虑信号的完整性、散热性能以及电磁兼容性(EMC)。

```bash

# 示例代码块 - 规划布线宽度

set_track_prop -class net -prop width 8 mil [find net *VCC*]

```

以上代码将所有VCC网络的布线宽度设置为8mil。

创建项目并完成基础约束设置后,将形成一个结构化的框架,为后续更详细的PCB设计提供了依据。

### 5.1.2 遇到的问题及解决方案

在设置基础约束时,设计者可能会遇到多种问题,例如:

- **资源限制**:在有限的PCB面积中实现高密度布局可能会导致无法满足某些间距要求。

- **信号完整性问题**:高速信号的布线可能难以满足时序要求,尤其是在复杂的布线环境中。

- **热管理问题**:高功率器件可能无法有效地散热,导致电路板工作温度过高。

针对这些问题,设计者可以采取以下解决方案:

- **进行分层设计和优化**:通过增加PCB层数来提供更多的布线空间,同时还能改善信号的回流路径。

- **使用高级布线技术**:使用差分布线、微带线(Microstrip)和带状线(Stripline)等技术,以优化信号的传输特性。

- **整合热管理措施**:在设计中增加散热片或热管,使用导热材料,优化铜箔(copper pours)的布局来增强热辐射和传导。

例如,解决信号完整性问题时,可以使用如下命令调整特定网络的布线策略:

```bash

# 示例代码块 - 调整布线策略以提高信号完整性

set_net_prop -class net -name "CLK_line" -route_method preferred

set_net_prop -class net -name "CLK_line" -impedance 50ohm

```

这里将CLK_line网络的布线策略设置为首选,并设定了50欧姆的阻抗匹配,有助于提高信号完整性。

通过上述示例,我们可以看到从零开始设置约束的过程,以及在此过程中遇到的一些常见问题和解决方案。这些内容为后续优化现有设计的约束提供了坚实的基础。

# 6. Allegro PCB 16.3优化技巧

## 6.1 优化信号完整性

信号完整性是PCB设计中极为重要的方面,它直接影响到电路的性能与可靠性。为确保信号传输过程中不产生失真、反射、串扰等信号完整性问题,设计师需采取以下优化措施:

- **保持信号路径一致性**:确保高速信号路径长度相等,以减少传输延迟和数据同步问题。

- **合理设置阻抗匹配**:通过调整走线宽度和使用适当的线路层,控制阻抗,以减少信号反射。

- **使用终端匹配技术**:如源端和负载端的电阻终端匹配,可以降低信号波形的振铃和过冲。

- **差分对设计**:对于高速信号,使用差分对可以有效降低噪声和干扰。

```

示例代码块:

; 设置阻抗为50欧姆

; 注意:不同的PCB材料和厚度,阻抗计算公式会有所不同。

; 这里只是一个示例,具体数值需要根据实际情况进行计算。

DRC 检查阻抗匹配时的错误信息:

SPURIOUS RINGING VIOLATION, NET: Reset, layer: TOP, impedance: 49.7 ohms (should be 50)

```

## 6.2 提升电源和地线设计质量

电源和地线设计是确保电路稳定运行的关键。电源平面和地线设计的不合理可能会导致电流环路过大,进而引起电磁干扰(EMI)。以下是一些实用的优化建议:

- **使用宽线布设电源和地线**:较宽的走线可以减少电阻,降低电源线上的电压降。

- **分割电源平面**:对于具有多种不同电压需求的复杂电路板,采用分割电源平面的方法,可减少电压间的干扰。

- **就近供电原则**:在高速和高功耗元件附近直接放置去耦电容,以减少瞬时电流引起的电压波动。

```

优化流程示例:

1. 识别高速元件和高功耗元件。

2. 为这些元件定义专门的电源和地线。

3. 在元件引脚附近放置去耦电容。

4. 调整走线宽度和电源平面设计。

5. 执行DRC确认设计是否满足要求。

```

## 6.3 布线优化策略

在Allegro PCB 16.3中,布线是一个动态且复杂的过程,它需要遵循一系列的优化策略以确保布局的合理性与效率:

- **智能布线算法**:利用软件内置的智能布线算法,如"飞线"技术,可以快速完成初步布线,减少手动布线的工作量。

- **层叠管理**:适当使用多层板,并进行有效的层叠管理,能提高布线的灵活性和信号的完整。

- **信号优先级设置**:根据信号类型和重要程度设置不同的优先级,保证关键信号的布线质量。

- **走线长度控制**:限制关键信号的走线长度,避免过长的走线引起的时间延迟和信号衰减。

```

层叠管理示例表格:

| 层次 | 类型 | 用途 | 颜色代码 |

|------|------|----------------|----------|

| TOP | 信号 | 顶层信号 | 红色 |

| MID1 | 电源 | 中间电源平面 | 绿色 |

| MID2 | 地线 | 中间地线平面 | 蓝色 |

| BOT | 信号 | 底层信号 | 红色 |

```

在Allegro PCB 16.3中,以上提到的优化策略可以帮助设计师提升设计的质量和效率,减少设计周期,优化最终产品的性能。随着PCB设计复杂度的增加,运用现代化的工具进行优化成为了保证设计成功的关键步骤。

0

0