数字集成电路设计第五章:工艺变革对电路设计的影响剖析

发布时间: 2024-12-15 08:50:41 阅读量: 10 订阅数: 17

(1)第一章 Verilog HDL数字集成电路设计方法概述.docx

参考资源链接:[数字集成电路设计 第五章答案 chapter5_ex_sol.pdf](https://wenku.csdn.net/doc/64a21b7d7ad1c22e798be8ea?spm=1055.2635.3001.10343)

# 1. 数字集成电路设计基础

数字集成电路的设计是现代电子工程的核心组成部分,它涵盖了从概念提出到最终产品实现的整个过程。本章将为您提供一个对数字集成电路设计过程的全面了解,包括基础的理论知识和设计原则,以帮助读者建立起集成电路设计的基础。

## 1.1 集成电路设计概述

数字集成电路设计过程涉及将多个晶体管及其互联集成在一块硅片上,形成具有特定逻辑功能的电路。随着集成电路的发展,设计复杂度呈指数级增加,但其核心原则始终围绕着可实现性、可靠性和效率展开。

## 1.2 设计方法论

从最初的电路图绘制到版图设计,再到最终的物理验证,数字集成电路的设计需要经过若干阶段,每个阶段都遵循特定的方法和工具。现代设计流程越来越多地采用自上而下的设计方法,强调在高层次上定义电路功能,并逐步细化。

## 1.3 设计实现与验证

设计完成后的验证过程至关重要,包括功能验证、时序验证和功率验证等。这些验证保证了电路在实际制造和使用中的性能满足设计预期,降低了失败的风险。

在接下来的章节中,我们将探讨工艺技术的演进,如何影响集成电路的设计,并深入分析集成电路设计中的一些关键技术与挑战。

# 2. ```

# 第二章:工艺技术的历史演进

## 2.1 半导体物理与工艺基础

### 2.1.1 半导体材料的物理特性

半导体材料是现代电子设备中的核心,其物理特性决定了它们在集成电路中的应用。硅是目前最广泛使用的半导体材料,其物理特性包括:

- **能隙宽度**:硅的能隙宽度约为1.1eV,适中的能隙使得在室温下可以有效控制电子和空穴的导电性质。

- **载流子迁移率**:硅中的电子和空穴迁移率在室温下分别为1400和450 cm²/Vs,适合形成有效的电流。

- **热导率**:硅具有较高的热导率,有助于散热,使设备在运行时保持良好的热稳定性。

- **化学稳定性**:硅在常温下与空气中的氧气反应形成二氧化硅层,具有极好的化学稳定性。

由于这些物理特性,硅成为了集成电路设计中的首选材料,使得半导体物理研究在工艺技术发展史上占据了重要位置。

### 2.1.2 早期工艺技术的发展

早期的半导体工艺技术发展,可以说是从一个简单的PN结二极管开始的。随着晶体管的发明,固体电路的发展经历了若干个重要阶段:

- **点接触晶体管**:这种晶体管结构简单,但可靠性较低,主要用于早期的电子设备中。

- **扩散型晶体管**:通过扩散杂质到硅基底中形成PN结,较点接触型性能更稳定,尺寸更小。

- **平面型晶体管**:引入光刻技术,在硅片上形成图案化的氧化层,减少了器件尺寸,提高了生产效率。

- **集成电路**:将多个晶体管集成在同一个芯片上,开启了微电子时代。

## 2.2 制造工艺的进步与分代

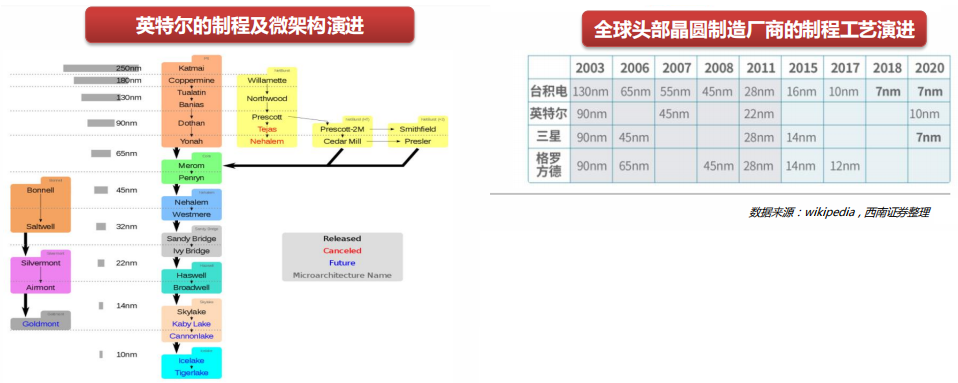

### 2.2.1 微米时代到纳米时代的转变

随着工艺技术的进步,从微米级制造工艺向纳米级工艺转变是集成电路领域的一大飞跃。这一转变带来了以下影响:

- **特征尺寸的减小**:特征尺寸从微米级别缩减到纳米级别,极大地提升了晶体管密度,降低了功耗。

- **量子效应的显著性增加**:随着尺寸的缩小,量子效应变得越来越显著,对设计和制造提出了新的挑战。

- **新材料的应用**:为了应对量子效应和尺寸效应,新型半导体材料如高介电常数材料被引入。

### 2.2.2 晶圆尺寸的变迁及其影响

晶圆尺寸的不断增大,显著地提升了集成电路的制造能力和经济效益。主要影响包括:

- **生产效率的提升**:更大尺寸的晶圆允许在每个生产周期中制造更多的芯片,从而降低了单个芯片的成本。

- **制造复杂性的增加**:更大尺寸的晶圆也带来了制造过程中的均匀性控制问题。

- **设备与工艺的更新**:随着晶圆尺寸的增加,制造设备和工艺也必须进行相应的更新和优化。

本章从半导体物理的基础出发,逐步深入到制造工艺的演进,为读者描绘出工艺技术发展的历史脉络,并为后续章节中工艺变革对电路设计影响的深入分析打下了坚实的基础。

```

# 3. 工艺变革对电路设计的直接影响

## 3.1 工艺尺寸缩小带来的挑战

### 3.1.1 亚阈值泄漏与功耗问题

随着集成电路制造工艺的不断进步,晶体管尺寸的缩小使得单个晶体管的功耗大幅降低,电路的整体功耗也随之减少。然而,这一进步同时也带来了亚阈值泄漏(subthreshold leakage)问题,对电路设计提出了新的挑战。

在纳米尺度工艺下,晶体管关闭时的亚阈值电流(即晶体管处于关闭状态但仍然有微量电流流过)变得不可忽视。这种泄漏电流会导致静态功耗增加,尤其是在大规模集成电路中,这一问题更为显著。亚阈值泄漏会减少电池寿命,提高设备发热量,并可能增加设备对冷却系统的需求。

为了应对亚阈值泄漏带来的功耗问题,设计人员开始采用多阈值电压CMOS(Multi-Threshold CMOS, MTCMOS)技术。通过使用高阈值电压晶体管来减少泄漏电流,同时使用低阈值电压晶体管以保持开关速度,实现功耗的优化管理。此外,动态阈值电压调整(Dynamic Threshold Voltage Adjustment)技术也逐渐被引入,该技术通过控制晶体管的阈值电压来降低泄漏电流。

### 3.1.2 制造过程中的物理限制和偏差

随着晶体管尺寸缩小至纳米级别,制造过程中的物理限制和偏差变得越来越明显。例如,光刻技术在更小尺寸上遇到了分辨率的限制,而且晶体管内部的电子迁移率和载流子迁移率的变化也会影响电路的性能。在如此微小的尺度下,材料缺陷和杂质也更容易引起电路性能的波动。

为了克服这些物理限制和偏差,设计者和制造商必须更加紧密地合作,采用更先进的制造工艺技术,如极紫外光(EUV)光刻技术,它能够提供更精细的图案定义。同时,设计时需要考虑更严格的制造偏差,比如在设计规则检查(Design Rule Check, DRC)和制造工艺设计(Design for Manufacturing, DFM)过程中。

此外,统计性工艺控制(Statistical Process Control, SPC)方法的引入也帮助制造商更精确地监控和调整工艺参数,从而减少制造偏差对最终电路性能的影响。

## 3.2 新型材料与器件结构的应用

### 3.2.1 高介电常数材料与低介电常数材料

为了应对工艺尺寸缩小带来的功耗问题,集成电路产业引入了高介电常数(High-K)材料和低介电常数(Low-K)材料。这些材料分别用于替代传统二氧化硅(SiO2)作为晶体管栅介质和互连层的电介质,以减少电容性负载和信号传输延迟。

高介电常数材料能有效降低栅漏电流,从而减少功耗,并允许晶体管门拥有更厚的栅介质,提高其电容。低介电常数材料则用来减少芯片内部线间互连的电容,降低信号传输延迟,进一步提升电路的速度和效率。

高介电常数和低介电常数材料的引入对电路设计造成了影响,设计师需要重新评估信号完整性、热管理和机械稳定性等问题。此外,对于这些新材料的掺杂、蚀刻和清洗等制造过程,也需要开发新的工艺技术。

### 3.2.2 新型晶体管结构:FinFET与GAA

随着传统平面晶体管面临物理极限,集成电路设计领域涌现出了新型晶体管结构,其中最具代表性的就是FinFET(Fin型场效应晶体管)和GAA(Gate-All-Around)晶体管。这两种结构的共同特点是利用立体的几何形状来增加控制沟道的栅极面积,从而提高控制效率,并减少短沟

0

0