【Zynq PL与软件协同】:动态加载在系统集成中的决定性角色

发布时间: 2024-12-27 21:37:12 阅读量: 10 订阅数: 9

xilinx zynq PL(Programming Logic) 动态加载实现

# 摘要

随着技术的迅速发展,Zynq平台因其PL(Programmable Logic)与软件的高效协同而受到广泛关注。本文首先概述了Zynq PL与软件的协同工作原理,详细介绍了Zynq PL的编程模型和开发环境搭建。接着,对动态加载的概念、重要性及其在Zynq PL中的实现进行了深入探讨,并分析了动态加载对资源和性能的影响。文章进一步探讨了动态加载的设计策略与实际应用案例,重点介绍了在特定领域如图像处理系统中的应用。最后,本文总结了动态加载调试和优化的方法,并展望了动态加载技术的未来趋势以及所面临的挑战,强调了动态加载技术在提高系统灵活性与可维护性方面的重要性。

# 关键字

Zynq PL;动态加载;软件协同;AXI接口;IP核;系统集成

参考资源链接:[Zynq-7000 SOC动态加载PL文件:Linux下FPGA Manager与xdevcfg驱动](https://wenku.csdn.net/doc/4e9h00tyeu?spm=1055.2635.3001.10343)

# 1. Zynq PL与软件协同概述

## 1.1 背景与协同的重要性

在现代电子系统设计中,软件与硬件的紧密结合变得越来越重要。Zynq®-7000可扩展处理平台(Zynq-7000 EPP)由Xilinx开发,将FPGA的灵活性与处理器的高性能进行了集成,创建了一个系统级芯片(SoC),用于广泛的嵌入式和工业应用。Zynq-7000 EPP结合了ARM处理器核心和可编程逻辑(PL)阵列,这种集成允许软件开发者和硬件设计师协同工作,以优化性能、功耗和功能。

## 1.2 Zynq PL与软件协同的工作模式

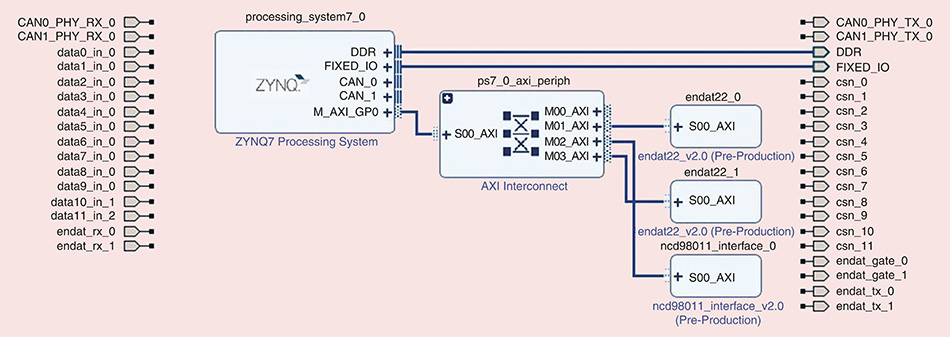

Zynq PL的设计目标是提供一个能够与软件运行在处理器核心上进行交互的硬件环境。为了实现这种协同,Zynq提供了多种通信机制,最常用的通信接口是高级可扩展接口(AXI),它允许处理器核心与PL之间进行高速、高效的数据交换。此外,Zynq的可编程逻辑允许开发者实现自定义的硬件加速器,这些加速器可被软件通过预定义的接口调用。

## 1.3 应用案例与协同优势

一个典型的使用案例是实时图像处理系统,在这种系统中,Zynq的处理器核心可以负责操作系统级别的任务和用户接口,而PL则可以实现图像处理算法的硬件加速。这样可以极大提高性能,降低功耗,并且提供更好的用户体验。与传统分离式的软硬件设计相比,Zynq PL与软件的协同工作模式可以在一个单一的芯片上实现更高效、更简洁的系统解决方案。

# 2. Zynq PL基础与编程模型

## 2.1 Zynq架构简介

### 2.1.1 Zynq SoC架构概述

Zynq平台将ARM处理器核心与可编程逻辑(Programmable Logic,简称PL)相结合,提供了一种系统级芯片(System on Chip,简称SoC)解决方案,实现了软件可编程性和硬件可定制性的完美融合。Zynq架构利用双核ARM Cortex-A9处理器,强大的多核处理性能与灵活的FPGA逻辑资源相结合,提供了广泛的可扩展性和设计灵活性。

Zynq架构的核心是ARM处理子系统(PS)和FPGA可编程逻辑子系统(PL)。PS部分负责执行操作系统和高级软件应用程序,而PL部分则提供用户定制的硬件加速器和接口功能,允许设计人员在硬件层面上实现性能优化。Zynq架构使得在同一芯片上可以运行操作系统和实时控制逻辑,提供了极大的灵活性和高效的集成设计。

### 2.1.2 PL(Programmable Logic)的角色和功能

可编程逻辑(PL)在Zynq架构中扮演着核心的角色,它将FPGA的灵活性和高性能与ARM处理器的处理能力结合在一起。通过PL,设计者能够添加自定义硬件功能,实现专用的硬件加速模块,提升系统性能并优化功耗。

PL部分包含了大量的逻辑单元、存储资源、专用的硬件接口以及高速串行通信接口。它允许开发者设计和实现定制的逻辑电路,例如数字信号处理(DSP)单元、图像处理引擎、自定义总线接口等。通过将这些功能直接集成到PL中,可以绕过PS中的处理器和操作系统开销,实现硬件级别的高效并行处理。

## 2.2 Zynq PL的编程环境搭建

### 2.2.1 Xilinx开发工具链安装与配置

要开始Zynq PL的设计和编程,首先需要安装并配置Xilinx提供的开发工具链。Xilinx开发工具链主要包括Vivado Design Suite和SDK(Software Development Kit)。Vivado是用于设计和实现FPGA逻辑的软件套件,而SDK用于开发嵌入式软件应用程序。

安装Vivado时,需要根据目标Zynq SoC选择合适的安装选项,确保安装包含了支持特定Zynq平台的IP核和预设。安装完成后,需要配置Xilinx工具链的环境变量,通常在用户的bashrc或相应的shell配置文件中进行设置。比如,对于Linux系统,可以在`.bashrc`文件中添加类似以下的路径配置:

```bash

export XILINX_VIVADO=<vivado-installation-path>/Vivado/2021.1/bin

export XILINX_SDK=<sdk-installation-path>/SDK/2021.1/bin

export PATH=$PATH:$XILINX_VIVADO:$XILINX_SDK

```

在配置环境变量之后,还需要下载并安装Zynq平台的板级支持包(Board Support Package, BSP)和特定的硬件描述文件(HDL)。这些文件通常可以在Xilinx的官方网站上找到,也可以通过Vivado软件直接下载。

### 2.2.2 创建和编译PL项目的基本步骤

一旦开发环境配置完成,就可以创建一个Zynq PL项目并进行编译。以下是创建和编译PL项目的基本步骤:

1. 打开Vivado软件,选择“Create New Project”来启动项目创建向导。

2. 在向导中填写项目名称、位置以及选择项目类型(如RTL Project)。

3. 选择目标Zynq SoC器件,并根据需要添加现有的HDL源文件或创建新的源文件。

4. 通过Vivado的IP Catalog添加所需的IP核,或创建自定义的IP核。

5. 利用Vivado的Block Design视图将所选IP核配置并连接起来,构建整个PL设计。

6. 使用Vivado的“Synthesis”和“Implementation”步骤对设计进行综合和布局布线。

7. 对生成的比特流文件(bitstream)进行生成和下载,以将设计加载到Zynq PL中。

```bash

vivado -mode batch -source <tcl-script-file>.tcl

```

以上命令使用Tcl脚本来执行创建项目、综合、布局布线以及生成比特流的整个流程。这是批量操作或自动化工具中的常见实践,例如在持续集成/持续部署(CI/CD)工作流中。

## 2.3 Zynq PL与软件的通信机制

### 2.3.1 AXI接口规范

在Zynq架构中,处理器子系统(PS)与可编程逻辑(PL)之间的通信主要通过高级可扩展接口(Advanced eXtensible Interface,简称AXI)进行。AXI是ARM公司开发的一种高性能、高带宽的内存映射接口,专为高性能、高吞吐量的通信设计。它支持多种数据传输模式,包括单次传输、突发传输等。

AXI接口规范定义了各种信号和协议,用于处理器和硬件加速器之间的交互。它主要分为以下几个通道:

- 读通道(Read Channel):处理器读取PL中的数据

- 写通道(Write Channel):处理器向PL写入数据

- 写响应通道(Write Response Channel):表明写操作的完成和状态

- 读数据通道(Read Data Channel):返回处理器的读请求数据

在设计Zynq PL时,使用AXI接口能够实现与PS部分的高效通信,同时保持硬件设计的简洁性。设计者可以在Vivado中直接添加AXI接口的IP核,通过简单的配置和连接,实现复杂的通信逻辑。

### 2.3.2 IP核生成和集成

在Zynq PL设计中,IP核(Intellectual Property Core)是可复用的硬件模块,用于提供特定的功能,如DSP处理、数据缓冲等。IP核的生成和集成是设计过程中的关键步骤,有助于提高设计效率和可靠性。

生成IP核的过程通常涉及以下步骤:

1. **定义IP核接口和行为**:确定IP核需要提供的功能,定义其输入输出接口以及内部行为。

2. **创建IP核模板**:在Vivado中创建IP核模板,提供一个基础的框架用于进一步的开发。

3. **编写

0

0