【32位ALU项目开发全程】:Logisim-MA从原型设计到成品制作

32位alu设计实验logisim-ma开发笔记

摘要

本文详细介绍了32位算术逻辑单元(ALU)的设计、实现与测试过程。从概念分析到最终的物理制作和验证,全面涵盖了项目需求分析、理论基础、原型设计、仿真测试以及硬件实现。本文首先介绍了32位ALU的基本概念和需求,随后探讨了使用Logisim工具进行ALU设计原理的实现,包括设计基本逻辑门电路和理解32位数据处理的重要性。接下来,文章转入32位ALU的原型设计与测试,重点描述了如何在Logisim中建立原型、验证功能及初步的性能优化。第四章深入到详细设计与仿真阶段,包括设计细节完善、仿真测试以及文档撰写。最终,在第五章中,从原型到实体制作的转换被详述,包括硬件组件的选择、PCB布局设计、组装、固件编程以及性能评估。最后一章总结了整个项目的回顾与经验,指出了潜在的改进方向和未来应用的可能性。

关键字

32位ALU;Logisim;原型设计;仿真测试;硬件实现;性能优化

参考资源链接:32位ALU设计实验:Logisim-MA开发笔记解析

1. 32位ALU项目的概念与需求分析

在现代计算领域,算术逻辑单元(ALU)是构成中央处理单元(CPU)的关键组件之一。它是执行所有算术和逻辑运算的硬件电路,通常包括处理器中的核心部分。对于专业IT从业者而言,深入理解ALU的设计和实现能够带来诸多益处,包括性能优化、故障排除,以及在需要高度定制解决方案时进行硬件创新。

1.1 ALU项目的目标与意义

本项目旨在设计和实现一个32位的ALU,它将支持一系列基本的算术运算(如加、减、乘、除)以及逻辑运算(如与、或、非、异或)。项目的成功将有助于加深我们对于处理器内部工作机制的理解,并为开发高效、优化的处理器设计奠定基础。

1.2 需求分析

对于32位ALU的需求分析包括了功能需求和性能需求两个方面。功能需求确保ALU能够正确执行所有预定的运算功能,而性能需求则关注运算速度、资源占用和功耗等指标。这一分析阶段对于项目的方向和最终的实现至关重要,因为它定义了设计的具体范围和限制。通过对目标用户的需求进行详尽的调研和理解,可以确保设计的ALU能够满足实际应用中的要求。

1.3 项目范围与限制

本项目将采用Logisim这一教育用的电路模拟工具来设计ALU,以降低硬件实现的风险和成本。尽管Logisim不支持直接的硬件部署,但它提供了一个强大的平台来模拟复杂的电路设计。同时,这也允许设计师在实际构建物理原型之前,先行在模拟环境中验证设计的正确性。我们将遵循一系列的步骤,从概念设计到详细设计,再到最终的测试和验证,确保最终交付的ALU产品能够满足预定的目标和需求。

2. Logisim工具的基本使用与ALU设计原理

2.1 Logisim的界面和基本操作

2.1.1 Logisim界面布局和功能模块

Logisim是一款直观且功能强大的电路设计模拟软件,特别适合于教学和电子系统原型设计。其界面布局被设计为直观、易用,以方便用户创建电路图。在Logisim的主界面上,主要区域被划分为三个部分:工具栏、侧边栏和画布区域。

- 工具栏:包含了文件操作、编辑操作、查看选项以及模拟控制等常用功能,用户可以利用它创建和编辑电路。

- 侧边栏:展示了不同类型的电路元件,比如输入输出设备、逻辑门、算术运算元件等,用户可以通过拖拽的方式将它们添加到画布上。

- 画布区域:用户在这个区域中实际绘制电路图。画布的大小是动态的,用户可以缩放查看不同部分的细节。

2.1.2 如何在Logisim中设计基本逻辑门电路

在Logisim中设计基本逻辑门电路可以遵循以下步骤:

- 打开Logisim:启动软件后,选择一个空白画布开始设计。

- 添加电路元件:从侧边栏中选择逻辑门,比如AND、OR、NOT门,然后拖拽到画布上。

- 连接电路元件:使用画布上的连线工具,将逻辑门的输入输出引脚相连,构建电路逻辑。

- 添加输入输出端口:在侧边栏中找到输入输出设备,例如开关(用于输入)和LED灯(用于输出),将它们添加到画布上,并与逻辑门电路相连。

- 模拟电路:点击工具栏上的“模拟”按钮,使用开关输入不同的信号,观察LED灯的亮灭来验证电路设计的正确性。

2.2 32位ALU的理论基础

2.2.1 ALU的功能定义和重要性

算术逻辑单元(ALU)是计算机处理器中的核心组成部分,负责执行所有的算术和逻辑运算。ALU的设计直接影响着计算机的整体性能,特别是在执行复杂的数据处理任务时。

- 算术运算:包括加法、减法、乘法、除法等基本运算,以及更高级的运算如平方根、指数等。

- 逻辑运算:涉及位运算,如AND、OR、NOT、XOR,以及移位操作等。

- 状态标志:ALU还需要生成状态标志,例如零标志(ZF)、符号标志(SF)、进位标志(CF)等,这些标志用于控制程序流程。

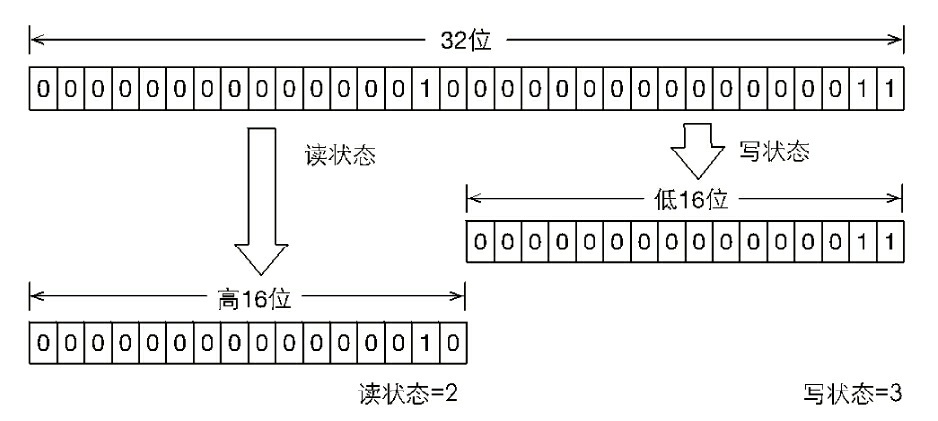

2.2.2 32位数据处理和运算逻辑

32位ALU的处理能力基于32位宽的数据总线,意味着它可以一次处理32位宽的数据。这为更复杂的数值计算和数据传输提供了基础。在32位ALU中实现的运算逻辑,如下:

- 算术运算:32位ALU能够处理高达2^32个不同数值的加减运算,包括处理溢出和进位。

- 逻辑运算:逻辑运算对32位宽的数据进行逐位操作,能够进行高效的位级数据处理。

- 位移和旋转:ALU还可以进行位移和旋转操作,这对数据的编码和解码至关重要。

2.3 设计32位ALU的前期准备

2.3.1 项目需求的进一步细化

在设计32位ALU之前,需要将需求细化为具体的设计参数,包括:

- 数据宽度:确定为32位,用于所有内部数据路径。

- 支持的操作:明确ALU需要支持的算术和逻辑操作。

- 性能要求:设定性能标准,如运算速度和功耗。

- 接口规范:定义与其他系统组件如寄存器堆和控制单元的接口。

2.3.2 设计文档的编写和审阅

设计文档应详细记录ALU的设计方案,包括:

- 功能描述:用文字和图示说明ALU如何实现各种运算。

- 数据流:描述数据如何在ALU内部流动,包括关键路径的详细分析。

- 接口定义:明确列出ALU对外的信号接口。

- 异常处理:定义ALU遇到的可能异常情况和处理机制。

在文档完成初稿后,需要组织内部和外部审阅,确保设计无误且满足所有需求。

3. 32位ALU的原型设计与测试

3.1 在Logisim中实现32位ALU原型

创建32位数据路径和控制单元

在设计32位ALU的原型时,首要步骤是创建数据路径和控制单元。数据路径是ALU中用于处理数据的部分,它包括寄存器、算术逻辑单元、以及用于数据传输的总线。控制单元则负责接收外部控制信号,并根据这些信号来控制数据路径中各个组件的操作。

在Logisim中,开始设计时需要熟悉其提供的图形化界面布局和功能模块。首先,我们需要绘制32位的输入输出端口,以便于数据的输入和结果的输出。接下来,设计寄存器,可以使用Logisim内置的触发器组件来实现。算术逻辑单元(ALU)的构建较为复杂,可能需要利用组合逻辑门电路,例如加法器、减法器、逻辑门等,来实现所需的功能。

下面是一个简化的代码示例,用于展示如何在Logisim中使用文本输入创建一个32位的寄存器:

- // 创建32位寄存器的Logisim代码示例

- // 假设我们要创建一个名为 "Register" 的32位寄存器

- // 1. 创建一个寄存器 (Register) 组件

- logisim.create("Register", 'register', {

- bits: 32,

- size: { width: 16, height: 4 },

- location: { x: 100, y: 50 }

- });

- // 2. 创建一个时钟信号来驱动寄存器

- logisim.create("Clock", 'clock', {

- location: { x: 50, y: 50 }

- });

- // 3. 连接时钟信号到寄存器的时钟输入端

- logisim.connect("Clock", "out", "Register", "clk");

在上述代码中,首先使用logisim.create方法创建了一个32位的寄存器组件,并设置了其大小和位置。然后创建了一个时钟信号组件,并将其输出端连接到寄存器的时钟输入端。在实际操作中,寄存器组件的每