【确保可测性】:设计时序节拍发生器的可测试性在Verilog HDL中的实现

摘要

时序节拍发生器是数字电路设计中的关键组件,其可靠性直接影响整个系统的性能。本文首先介绍了时序节拍发生器的基本概念,随后深入探讨了Verilog HDL编程基础,包括语言的语法结构、时序控制以及测试平台的编写技巧。接着,文章转向可测试性设计理论,阐述了设计的可测试性要求、技术方法和评估指标。在可测试性实现方面,本文着重讲述了模块化、抽象化、可观测性和可控性设计的重要性,并展示了如何在Verilog中实现这些功能。最后,通过实践案例分析,本文提供了时序节拍发生器设计实例、可测试性评估以及后续测试与优化步骤。本文旨在为设计者提供一套全面的时序节拍发生器设计与测试的理论和实践指南。

关键字

时序节拍发生器;Verilog HDL;可测试性设计;模块化;内建自测试;故障覆盖率

参考资源链接:Verilog HDL实现:时序节拍发生器与序列逻辑设计

1. 时序节拍发生器的基本概念

1.1 时序节拍发生器的作用与重要性

时序节拍发生器是数字电路中一个不可或缺的组件,它负责产生精确的时序信号以同步电路内的其他元素。在复杂的数字系统中,时序节拍发生器提供的时钟信号决定了整个系统的工作节奏。此外,它对于电路稳定性和性能优化起到关键作用,使得电路操作得以预测和控制。

1.2 时序节拍发生器的类型及其应用场景

时序节拍发生器可以是简单的时钟发生器,也可以是具有复杂功能的锁相环(PLL)或延迟锁相环(DLL)。在不同的应用场景中,如微处理器、存储设备、通信接口等,时序节拍发生器的设计和应用也有所不同,以适应系统的特定需求。

1.3 设计时序节拍发生器时需考虑的因素

在设计时序节拍发生器时,工程师需要考虑到时钟频率的稳定性、相位噪声、电源管理以及温度、电压和工艺的变异对时钟信号的影响。此外,设计时还应考虑到系统的扩展性、功耗、成本以及与现有系统的兼容性等因素。这些因素综合决定着最终产品的质量和可靠性。

2. Verilog HDL编程基础

2.1 Verilog语言的语法结构

2.1.1 模块定义与端口描述

Verilog HDL 是一种用于电子系统级设计的硬件描述语言,它允许设计师使用文本描述来表达硬件电路的结构和行为。在 Verilog 中,一个基本的设计单位称为“模块”。模块是具有特定功能的最小单元,它可以是组合逻辑电路,也可以是时序逻辑电路,甚至可以包含子模块。

一个典型的模块定义通常包括模块声明、端口列表、内部信号声明、逻辑描述和模块结束标志。下面是模块定义和端口描述的一个例子:

- module clock_generator(

- input wire clk, // 时钟输入

- input wire reset, // 复位信号

- output reg out_clk // 时钟输出

- );

- // 时序逻辑实现

- endmodule

在这个例子中,clock_generator 是模块的名称,它接受两个输入信号 clk 和 reset,以及一个输出信号 out_clk。在 Verilog 中,input 和 output 关键字用于声明模块的端口,端口类型可以是 wire 或 reg。wire 用于组合逻辑的连续赋值,而 reg 通常用于时序逻辑的赋值。

2.1.2 数据类型与赋值操作

Verilog 提供了多种数据类型来支持硬件描述的需求。其中最常用的数据类型包括:

wire: 用于表示逻辑连接线,通常用于组合逻辑的输出。reg: 用于表示寄存器或存储元素,可以被赋值语句赋值,用于时序逻辑。integer: 整型变量,通常用于循环计数或中间计算。real: 实数类型,用于浮点数运算。time: 用于存储时间值。bit: Verilog-2001 引入的新类型,可以有多个值,但不包括高阻态。

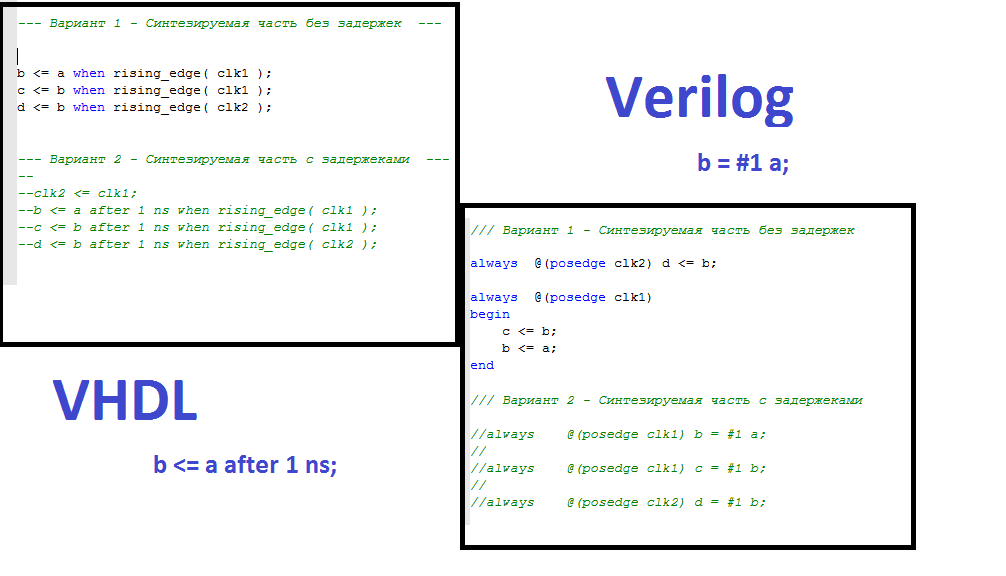

在 Verilog 中,赋值操作分为连续赋值和过程赋值。连续赋值使用 assign 关键字,而过程赋值则用在 always 块中。过程赋值可以是阻塞赋值(=)或非阻塞赋值(<=),阻塞赋值在模拟中是顺序执行的,而非阻塞赋值在每个 always 块结束后才执行,这在描述时序逻辑时非常重要,有助于避免竞争条件。

- reg a, b;

- wire y;

- assign y = a & b; // 连续赋值

- always @(posedge clk) begin

- a <= b; // 非阻塞赋值

- b = a; // 阻塞赋值

- end

在上面的代码中,y 被连续赋值为 a 和 b 的逻辑与结果。而在 always 块中,a 使用非阻塞赋值更新为 b 的值,而 b 使用阻塞赋值立即更新为 a 的当前值。

2.2 Verilog中的时序控制

2.2.1 时钟信号的定义与使用

在数字设计中,时钟信号起着至关重要的作用,它为整个系统提供了一个同步基准。在 Verilog 中,always 块通常用于描述时序逻辑,而 posedge 和 negedge 关键字用于指定时钟的上升沿或下降沿触发。

- module flip_flop(

- input wire clk,

- input wire d,

- output reg q

- );

- always @(posedge clk or posedge reset) begin

- if (reset) begin

- q <= 0;

- end else begin

- q <= d;

- end

- end

- endmodule

在这个边沿触发的 D 触发器模块中,输出 q 在时钟的上升沿被更新为输入 d 的值,或者当复位信号 reset 为高时,输出 q 被强制置零。

2.2.2 延迟和阻塞非阻塞赋值的理解

在 Verilog 中,赋值操作可以通过延迟来模拟信号传播延迟。延迟可以是固定的也可以是不确定的。在描述组合逻辑时,# 符号用于指定延迟量。

- reg [3:0] a;

- wire [3:0] b;

- assign #5 b = a; // 5个时间单位的延迟

阻塞和非阻塞赋值在时序逻辑中有着不同的应用。阻塞赋值(=)要求赋值在仿真中是立即执行的,这在组合逻辑中是需要的。然而,使用阻塞赋值来描述时序逻辑可能会导致意外的仿真行为,因为它们可能引起冒险条件。非阻塞赋值(<=)允许在 always 块执行结束时才进行赋值,这更好地模拟了硬件中的行为。

- always @(posedge clk)