Linux开发利器教程:一步到位安装与配置make命令

发布时间: 2024-12-21 20:31:51 阅读量: 6 订阅数: 12

# 摘要

本文对Linux系统下的make命令进行了系统性介绍,涵盖了make命令的基础知识、高级配置、实践应用以及调试与维护。通过解析Makefile的结构和规则,详细阐述了make命令的工作原理和语法,并通过高级配置展示了条件语句、函数、自动变量和特殊变量的应用。此外,本文还提供了综合案例分析,包括简单和复杂项目的Makefile配置以及监控实际的编译和链接过程。最后,探讨了make命令的替代品如CMake、Meson等,并总结了最佳实践和技巧。本文旨在为Linux环境下的开发者提供全面的make命令使用指南,提升项目构建和管理的效率。

# 关键字

make命令;Makefile;编译链接;自动变量;版本控制;项目构建

参考资源链接:[Linux中无make命令的安装与解决教程](https://wenku.csdn.net/doc/6412b6e1be7fbd1778d484f0?spm=1055.2635.3001.10343)

# 1. Linux系统下的make命令概述

Linux 系统中,`make` 命令是项目构建与管理的核心工具,尤其在软件开发领域扮演着重要角色。开发者通过编写 `Makefile` 文件来定义程序编译、链接的规则和依赖关系。`make` 命令可以根据文件修改时间,智能地构建或更新程序,极大提高构建效率。本章将带您快速了解 `make` 命令的基础知识,为后续深入学习和实践打下坚实基础。

# 2. make命令基础

## 2.1 make命令的工作原理

### 2.1.1 Makefile的结构解析

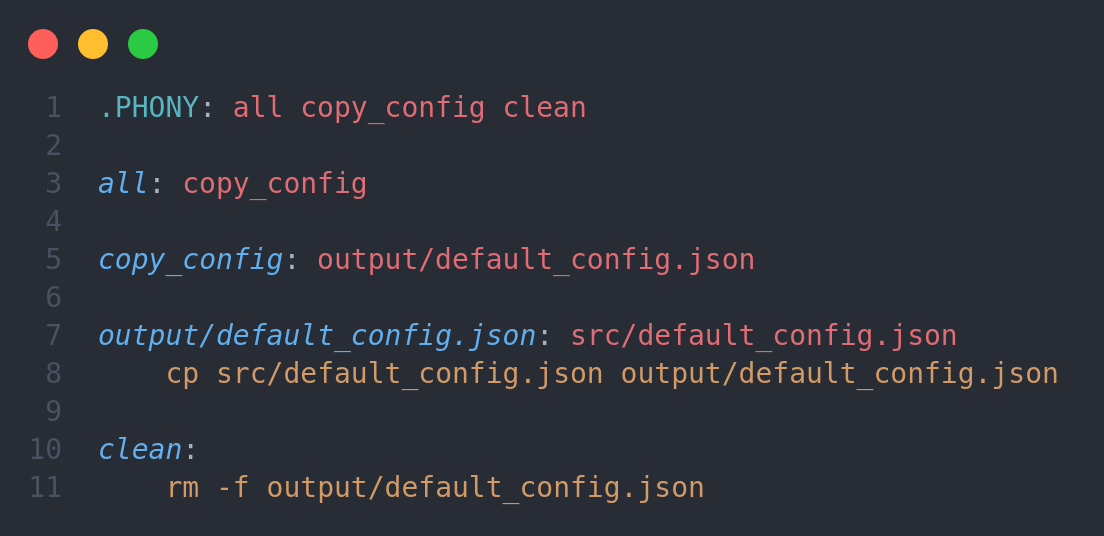

Makefile文件是make工具的基础,它定义了一系列的规则来告诉make如何编译和链接程序。一个典型的Makefile文件主要包含以下几个部分:

- 目标(target):通常是要生成的文件名,也可以是执行的动作,如编译器、程序或其他命令。

- 依赖(dependencies):列出生成目标所需的文件或目标。

- 命令(commands):用于创建目标的shell命令。

Makefile中还包含一些特殊的结构,例如:

- 变量(variables):用于存储经常使用的字符串或文件名列表等,简化Makefile。

- 模式规则(pattern rules):允许使用模式匹配定义规则,适用于一类相似的文件。

结构解析的实质是对Makefile文件中的各个部分进行详细解读和运用,以便于更加灵活和高效地使用make命令。

### 2.1.2 规则、目标和依赖关系的介绍

**规则 (Rule)**:是Makefile文件的核心,描述了如何根据依赖文件生成目标文件。

一个基本的Makefile规则示例如下:

```makefile

target: dependencies

commands

```

**目标 (Target)**:是一个文件名,也可以是一个动作的名称。它指向最终要生成或执行的文件或命令。

**依赖关系 (Dependencies)**:指定为了生成目标所需的输入文件或其它目标。当依赖关系中的文件比目标文件更新时,make会执行规则中定义的命令。

这里,我们首先通过一个简单的例子来理解规则的工作流程:

```makefile

app: main.o utils.o

gcc -o app main.o utils.o

```

上面的Makefile中,“app”是目标,它的依赖项是“main.o”和“utils.o”。如果这些依赖项中有任何一个比目标“app”新,make将执行后面缩进的命令来重新编译“app”。

## 2.2 Makefile的基本语法和规则

### 2.2.1 常用的内置规则和变量

**内置规则**:make提供了一些默认的规则,用来简化常见的构建任务。例如:

```makefile

%.o: %.c

gcc -c $< -o $@

```

这个规则定义了如何将`.c`文件编译成`.o`文件,`$<`代表第一个依赖文件,`$@`代表目标文件。

**变量**:Makefile中的变量类似编程语言中的常量,可以存储路径、编译器选项等,使用时可以用`$(VARIABLE_NAME)`的形式来引用。

```makefile

CC=gcc

CFLAGS=-Wall

```

这里定义了编译器`CC`和编译器选项`CFLAGS`。在命令行中,只需要使用`$(CC)`和`$(CFLAGS)`即可。

### 2.2.2 自定义变量和模式规则的应用

**自定义变量**:在Makefile中创建用户自己的变量,用于控制编译过程,如包含头文件的路径、库的路径等。

```makefile

INCLUDE_PATH = -I./include

LIB_PATH = -L./lib

```

在编译时,你可以通过添加变量来简化命令。

**模式规则**:允许我们定义适用于一组文件的规则。通常使用通配符或模式来匹配文件名。

```makefile

%.o: %.c

gcc $(CFLAGS) -c $< -o $@

```

模式规则`%.o: %.c`表示任何以`.o`结尾的目标都可以使用`.c`为依赖的规则来构建。

## 2.3 make命令的实践基础

### 2.3.1 创建第一个Makefile示例

创建一个简单的Makefile来编译一个C程序,这个程序由两个源文件`main.c`和`utils.c`组成。

```makefile

# 定义编译器和编译选项

CC=gcc

CFLAGS=-Wall

# 定义目标文件和最终的可执行文件

TARGET=app

OBJS=main.o utils.o

# 最终的构建规则

$(TARGET): $(OBJS)

$(CC) $(CFLAGS) -o $@ $^

# .PHONY 表示这个目标不是一个文件名

.PHONY: clean

# 清理编译生成的文件

clean:

rm -f $(OBJS) $(TARGET)

```

在终端中输入`make`,Makefile将会执行默认的目标规则来生成`app`。

### 2.3.2 常用的make命令选项

- `-n` 或 `--just-print`:仅显示将要执行的命令,不实际执行。

- `-f` 或 `--file`:指定Makefile文件。

- `-p` 或 `--print-data-base`:在执行之前,输出Makefile中的所有规则和变量。

- `-s` 或 `--silent`:在执行时不输出命令。

- `-j` 或 `--jobs`:并行执行命令,加快构建速度。例如`make -j4`会用4个进程并行构建。

例如,使用`make -p`命令可以在编译之前查看Makefile的内容,包括所有的规则和变量设置。这对于调试和验证Makefile的配置非常有用。

## 2.4 Makefile的文件命名和位置

Makefile可以在不同的目录下存在,并且可以有不同的名称。通常,在Linux和Unix系统中,默认的Makefile名称是Makefile或者makefile。

1. **文件命名**:用户可以自定义Makefile文件的名称,通过使用`-f`参数可以指定Makefile的路径和名称。例如:`make -f custom-makefile`。

2. **文件位置**:当make被调用时,它会在当前目录下搜索Makefile,如果该目录下不存在Makefile,make会在父目录下搜索。用户也可以通过`-C`参数指定make的工作目录。

```shell

make -C /path/to/directory

```

3. **使用相对路径和绝对路径**:在Makefile中,路径的指定可以是相对路径或绝对路径。在依赖项和命令中,使用相对路径是常见的做法。

- **相对路径**:相对于Makefile所在的位置。

- **绝对路径**:从根目录开始指定完整路径。

4. **文件搜索顺序**:如果Makefile没有在指定路径下找到,make会根据环境变量`VPATH`指定的目录来查找。如果没有设置`VPATH`,make将只在当前目录和其父目录下查找Makefile。

为了理解Makefile的文件命名和位置的进一步应用,考虑下面的场景:

假设当前目录为`/home/user/project`,并且想要编译`src`目录下的程序,但是Makefile位于`/home/user/project/makefiles`目录下。

可以使用以下命令进行编译:

```shell

make -f /home/user/project/makefiles/Makefile

```

或者在`/home/user/project`目录下设置环境变量`VPATH`指向Makefile所在的目录:

```shell

export VPATH=/home/user/project/makefiles

make

```

**总结**:make命令的工作原理涉及Makefile文件的结构和规则的解析。Makefile由目标、依赖、命令等组成,并定义变量和模式规则来管理构建过程。在实践中,创建第一个Makefile示例和理解make命令的基本选项对于使用make工具来说是必不可少的。同时,了解Makefile文件命名和位置对于构建过程的组织和管理同样重要。

# 3. make命令的高级配置与应用

## 3.1 条件语句和函数的高级应用

### 3.1.1 条件判断和逻辑运算的使用

在Makefile中使用条件语句可以让编译过程更加灵活,可以根据不同的条件执行不同的规则。条件判断主要通过`ifeq`、`ifneq`、`ifdef`和`ifndef`等关键字实现。逻辑运算符包括`&&`(与)、`||`(或)和`!`(非)。

例如,以下是一个条件判断的例子:

```makefile

# 检查编译器类型,并设置不同的编译选项

ifeq ($(CC),gcc)

CFLAGS += -Wall -Werror

else

CFLAGS += -W -Xlinker -zmuldefs

endif

```

在上述Makefile片段中,如果变量`CC`的值为`gcc`,则为`CFLAGS`添加`-Wall`和`-Werror`标志。否则,使用其他标志。这样的条件语句对于在不同的编译环境下保持代码的一致性非常有用。

### 3.1.2 函数的定义和调用

Makefile中可以定义和调用函数来执行更复杂的文本处理。例如,`wildcard`函数可以获取匹配模式的文件列表,`p

0

0