操作系统内核开发的秘密武器:汇编技术深度解析

发布时间: 2025-01-05 19:39:28 阅读量: 5 订阅数: 11

停车场管理系统c语言.docx

# 摘要

本文旨在探讨操作系统内核与汇编技术的应用和实践,系统地介绍了汇编语言的基础知识、体系结构特点及其在内核开发中的具体应用。通过对x86和ARM架构下汇编指令的深入分析,本文揭示了汇编语言在操作系统启动流程、内存管理、中断处理以及驱动程序开发中的关键作用。同时,本文还着重讨论了内核级编程中的汇编技巧与优化,包括性能优化技术、C语言与汇编的混合编程以及面向未来的汇编语言发展趋势。通过对高级汇编编程案例的分析,本文展示了汇编语言在系统调用实现、内核调试和跨平台实现方面的高级技巧和策略。

# 关键字

操作系统内核;汇编技术;体系结构;内存管理;中断处理;性能优化

参考资源链接:[汇编语言程序设计:实现十进制数相加](https://wenku.csdn.net/doc/93y2smnbkx?spm=1055.2635.3001.10343)

# 1. 操作系统内核与汇编技术概述

在现代计算环境中,操作系统内核和汇编技术构成了计算机科学的基础。本章旨在对这两者的关系及其在计算机架构中的重要性进行探讨。

## 操作系统的角色

操作系统(OS)是管理计算机硬件与软件资源的系统软件,它作为应用程序与硬件之间的桥梁,负责调度任务、管理内存、设备驱动等关键功能。

## 汇编语言的重要性

汇编语言是一种低级语言,与机器语言有着一对一的对应关系。它的效率高,直接控制硬件资源,在内核开发中不可或缺。由于其能够进行精确的内存和寄存器操作,因此在性能敏感区域和硬件接口处,汇编语言被频繁使用。

## 内核开发中的汇编技术

在操作系统的内核开发中,汇编语言通常用于启动引导程序、中断和异常处理、以及与硬件直接交互的部分。通过深入理解汇编技术,开发者可以编写更加高效、稳定的内核代码,实现对系统行为的精准控制。

此章节为读者提供了一个操作系统内核开发与汇编技术的基础概览,为后续章节更深入的技术讨论打下基础。

# 2. 汇编语言基础和体系结构

## 2.1 汇编语言的基本组成

### 2.1.1 指令集架构概述

在深入探讨汇编语言细节之前,理解它所依赖的指令集架构(Instruction Set Architecture,ISA)是至关重要的。ISA定义了计算机处理器的硬件接口,包括可以执行的指令、寄存器、存储器访问方式、I/O等。

指令集架构可以划分为两大类:复杂指令集计算机(Complex Instruction Set Computer,CISC)和精简指令集计算机(Reduced Instruction Set Computer,RISC)。CISC架构的代表是x86架构,而RISC架构的代表则是ARM。在不同的架构下,汇编语言的指令集、寻址模式和寄存器结构都有所不同。

x86架构以其广泛的兼容性和向后兼容性而闻名,它支持多种操作模式,比如实模式、保护模式和长模式,这些模式适应了从个人电脑到服务器的不同需求。而ARM架构则以其高效率和低能耗特性,在移动设备和嵌入式系统领域占据主导地位。

### 2.1.2 汇编语言的语法规则

汇编语言是一种低级语言,直接与机器语言交互,它依赖于特定架构的指令集。一个简单的汇编指令通常包括标签(可选)、操作码(也称为助记符)和操作数(可选)。在x86架构中,语法规则还涉及到了操作数的大小前缀,如`byte ptr`、`word ptr`和`dword ptr`等。

下面是x86架构下的一个简单的汇编指令示例:

```assembly

mov eax, 1 ; 将数字1移动到eax寄存器

```

在此指令中,`mov`是操作码(助记符),表示移动数据的指令;`eax`是目标操作数,指定数据将被放置到哪个寄存器中;而`1`是源操作数,表示要移动的数据值。

指令的复杂性可以从简单的数据传输到复杂的算术运算和逻辑运算,再到控制流程的跳转和循环。汇编语言的编写通常涉及对寄存器和内存的直接操作,要求程序员对硬件架构有深入的理解。

## 2.2 x86架构下的汇编指令

### 2.2.1 数据传输指令详解

数据传输指令是汇编语言中最基本的指令类别之一,主要用于在寄存器、内存和I/O端口之间移动数据。在x86架构中,数据传输指令包括MOV、PUSH、POP等。

例如,MOV指令是最常用的指令,它可以将数据从源移动到目的地:

```assembly

mov al, [0x1234] ; 将内存地址0x1234处的值移动到AL寄存器

mov [esi+4], ebx ; 将EBX寄存器的值移动到ESI寄存器偏移4个字节的内存地址

```

在编写数据传输指令时,程序员需要理解数据的对齐和大小,因为不同的数据类型(如字节、字、双字和四字)需要不同的指令前缀来指定操作数的大小。未对齐的数据访问可能会导致性能下降或在某些处理器上引发异常。

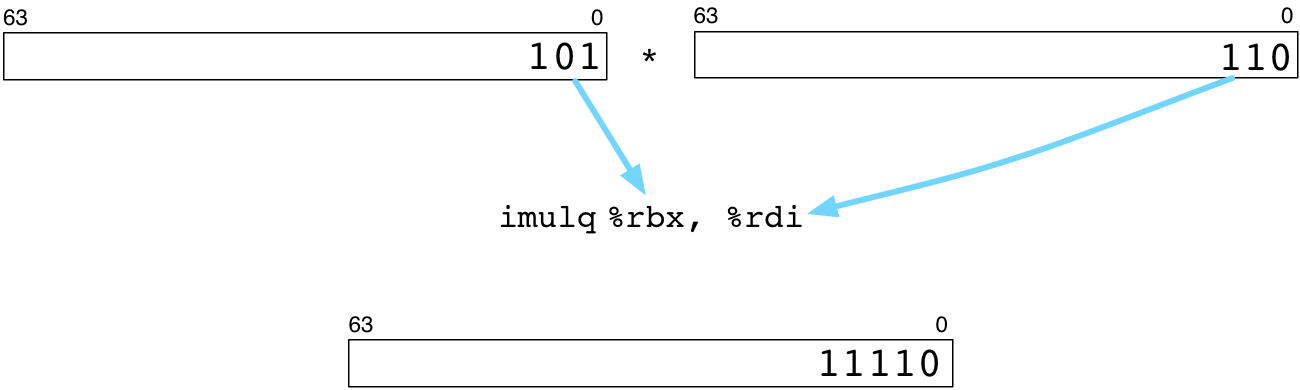

### 2.2.2 算术与逻辑指令应用

算术与逻辑指令涉及数据的计算和处理,是编写高效汇编程序不可或缺的部分。它们包括加法(ADD、ADC)、减法(SUB、SBB)、乘法(MUL)、除法(DIV)等算术运算,以及逻辑运算(AND、OR、XOR、NOT)等。

这些指令可以直接操作CPU的标志寄存器,例如零标志(ZF)、进位标志(CF)、溢出标志(OF)等,这些标志在执行条件分支指令时非常有用。

以ADD指令为例:

```assembly

add eax, ebx ; 将EBX寄存器的值加到EAX寄存器

```

上述指令执行后,如果EAX寄存器的值为零,则零标志ZF将被设置为1。程序员可以利用这些标志来执行条件跳转或循环。

### 2.2.3 控制流指令和异常处理

控制流指令用于改变程序执行的顺序,例如无条件跳转(JMP)、条件跳转(JZ、JNZ、JE、JNE等)、函数调用(CALL)和返回(RET)等。

异常处理指令则涉及异常和中断,它们允许程序响应错误条件或其他重要的系统事件。中断指令(INT)和中断返回(IRET)是关键的控制流指令。

```assembly

int 0x80 ; 触发系统调用中断

```

异常处理指令通常用于实现系统调用、处理硬件中断以及软件异常。它们允许系统从用户态切换到内核态,以便执行特权操作。

## 2.3 ARM架构下的汇编指令

### 2.3.1 ARM与Thumb指令集对比

ARM架构具有两种指令集:ARM和Thumb。ARM指令集是32位的,而Thumb指令集是16位的,旨在提供更高的代码密度。ARM架构中的处理器可以在两种模式之间切换,这使得它们能够根据运行时需求平衡性能和代码大小。

在编写ARM汇编程序时,程序员需要根据目标处理器的支持情况和性能要求选择合适的指令集。由于Thumb指令集的宽度较小,因此在内存受限的应用中,如嵌入式系统,它通常比ARM指令集更为高效。

### 2.3.2 ARM架构中的特殊指令应用

ARM架构有一些特有的指令,例如数据处理指令(如MOV、ADD、SUB),数据传输指令(如LDR、STR),以及控制流指令(如B、BL、BX)。此外,ARM架构还支持条件执行指令,这意味着某些指令只有在满足特定的CPU标志状态时才会执行。

例如:

```assembly

addeq r0, r1, r2 ; 如果之前的操作导致了等值标志(EQ)被设置,则执行加法操作

```

这种条件执行可以减少分支指令的使用,提高程序执行效率。

### 2.3.3 处理器状态切换和权限控制

ARM架构的处理器支持不同的执行状态:用户态和特权态。处理器状态切换通常通过系统调用指令(如SVC)实现。特权态允许执行敏感指令,如内存管理指令和系统寄存器访问。

权限控制是通过访问权限级别(Privilege Level)和异常处理来实现的。在处理异常时,处理器进入异常模式,这是一种特权模式,允许执行中断服务程序。

处理器状态切换和权限控制对于实现安全可靠的操作系统至关重要,它们为不同级别的代码执行提供了硬件支持。

在这一章节中,我们详细地介绍了汇编语言的基础组成,包括指令集架构的概念、数据传输指令、算术与逻辑指令、控制流指令等。我们强调了理解架构细节的重要性,以及这些细节如何影响汇编语言的编写。此外,我们还探讨了ARM架构中的特定指令及其应用,以及状态切换和权限控制在实现安全和高效程序设计中的作用。在接下来的章节中,我们将进一步深入到汇编语言的实践中,特别是在内核开发中的应用。

# 3. 汇编技术在内核开发中的实践

## 3.1 操作系统启动流程中的汇编代码

### 3.1.1 BIOS与UEFI启动机制概述

在探讨操作系统内核开发之前,理解启动过程中的汇编代码是至关重要的。操作系统启动时首先与硬件进行交互的是固件,传统的个人计算机使用的是BIOS(基本输入输出系统),而较新的硬件平台开始采用UEFI(统一可扩展固件接口)作为启动机制。

**BIOS**是计算机启动后首先加载的一段程序,它执行硬件初始化,并检查系统状态,然后加载引导扇区到内存,并将其执行权转移给引导扇区。BIOS通常是16位实模式下运行的代码,这使得其只能访问有限的内存空间。

与BIOS不同,**UEFI**采用模块化设计,能够运行在保护模式下,支持更大的内存空间,并且提供了

0

0