【GNU make效率秘籍】:用Makefile提升代码生产力

摘要

GNU make是一个广泛使用的构建自动化工具,特别适用于C/C++、Python等语言编写的项目。本文旨在为初学者和中级用户全面介绍make工具及其核心文件Makefile的编写和优化。文章首先概述了make工具的基本概念,接着深入讲解了Makefile的结构和组成,包括规则、目标、依赖、命令、变量、模式规则等。在此基础上,文章着重探讨了如何通过条件判断、循环、环境定制和模块化管理来实现高效、可维护的Makefile。此外,本文还深入探讨了Makefile在版本控制集成、调试、错误处理以及跨平台项目中的高级技巧和应用案例。通过学习本文内容,用户能够掌握编写高效且具有扩展性的Makefile,从而提升项目的构建效率和维护性。

关键字

GNU make;Makefile;规则;依赖;版本控制;跨平台构建

参考资源链接:GNU make中文手册:Makefile编写详解

1. GNU make工具概述

GNU make是一个用于构建和编译软件的自动化工具,其核心是通过Makefile文件中定义的一系列规则来控制软件的构建过程。通过自动化这些构建步骤,make能够有效地管理项目依赖关系,提高开发效率,并减少人为错误。make工具广泛应用于C/C++、Java等编程语言的项目中,几乎成为软件开发中不可或缺的组成部分。在本章中,我们将概述make工具的基本功能和使用场景,为深入理解Makefile的编写和优化打下坚实的基础。

2. Makefile基础

2.1 Makefile规则和目标

2.1.1 规则的基本语法和组成

Makefile规则是用来指示make程序如何编译和链接程序的指令集合。一个规则通常包含三个部分:目标(target)、依赖(dependencies)和命令(commands)。

- 目标(target):通常是一个文件名,代表规则的最终生成产物,例如编译生成的可执行文件或目标文件。

- 依赖(dependencies):列出创建目标所必须的文件或其它目标,目标的创建依赖于这些文件的更新。

- 命令(commands):描述了如何通过依赖文件来创建目标的步骤,通常是一些shell命令。

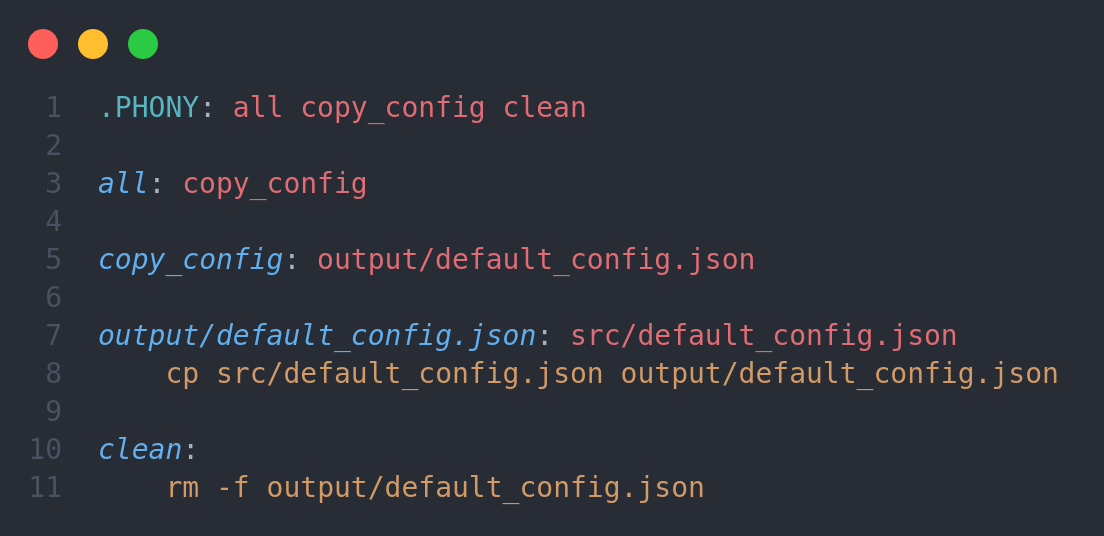

规则的基本语法如下:

- target ... : dependencies ...

- commands

在上述结构中,命令前必须有一个制表符(Tab键),而不是空格。

举个简单的例子,假如有一个main.o目标文件依赖于main.c和header.h文件,而生成main.o的命令是gcc -c main.c。对应的Makefile规则可以这样写:

- main.o: main.c header.h

- gcc -c main.c

这个规则告诉make,如果main.c或header.h比main.o新,或者main.o不存在,就执行gcc -c main.c来生成main.o。

2.1.2 目标(target)、依赖(dependencies)和命令(commands)

- 目标(target):通常是我们希望

make构建的最终产物,可以是执行文件、库文件、甚至是某个操作,比如“clean”通常是一个伪目标,用来清除之前的构建结果。 - 依赖(dependencies):帮助Makefile识别当哪些源文件发生变化时,需要重新构建目标。依赖关系可以是文件,也可以是目标,甚至是规则本身。

- 命令(commands):是执行实际构建工作的地方,可以是编译命令、链接命令,也可以是调用其他程序或脚本来处理源文件。

对于Makefile中的每一个规则,make会检查其依赖是否满足,如果不满足,它会寻找对应的依赖规则并试图构建它们。只有当所有依赖项都比目标更新时,或者目标不存在时,make才会执行命令。

此外,Makefile还支持模式规则,使得构建过程更加灵活和可重用。

2.2 Makefile的变量和模式规则

2.2.1 变量的定义和使用

变量在Makefile中是被广泛使用的,它用于存储文件名、编译选项、路径等重复使用的信息。

变量的定义方式如下:

- CC=gcc

- CFLAGS=-Wall

- OBJ=main.o utils.o

使用变量时,在变量名前加$(...)或者${...}。比如使用上面定义的变量CC,可以这样引用:$(CC)。

例子:

- CC=gcc

- CFLAGS=-Wall

- OBJ=main.o utils.o

- EXEC=program

- $(EXEC): $(OBJ)

- $(CC) -o $(EXEC) $(OBJ) $(CFLAGS)

在上述例子中,我们定义了三个变量CC、CFLAGS和OBJ。$(CC)表示gcc编译器,$(CFLAGS)表示编译选项,$(OBJ)表示目标文件列表。构建可执行文件program时,make会使用这些变量。

2.2.2 模式规则的应用和扩展

模式规则为Makefile提供了更加强大的构建能力。模式规则使用%通配符来匹配一系列文件。

例如,一个简单的模式规则,用来编译所有的.c文件到对应的.o文件:

- %.o : %.c

- $(CC) -c $(CFLAGS) $< -o $@

这里的$<代表规则中的第一个依赖(例如%.c匹配到的文件),$@代表规则中的目标(例如%.o匹配到的文件)。当运行make,它会根据模式规则自动匹配.c文件到.o文件并执行相应的编译命令。

模式规则极大地简化了Makefile的编写,并使得它对于不同类型的文件具有更好的通用性和扩展性。

2.3 Makefile的自动化变量和函数

2.3.1 自动化变量介绍和使用场景

自动化变量是make的内置变量,它们在命令执行时自动获取值,使得Makefile编写更为高效。最常见的自动化变量包括:

$@: 表示规则中的目标(target)。$%: 当目标(target)是一个静态库文件时,表示目标中归档成员的文件名。$<: 规则中的第一个依赖文件。$?: 所有比目标(target)新的依赖文件列表。$^: 所有的依赖文件列表。$+: 类似于$^,但是会保留重复的依赖项。$*: 在模式规则和静态模式规则中,表示模式匹配的部分。

使用场景举例:

- %.o : %.c

- gcc -c $< -o $@

上述规则使用$<来表示编译的源文件,$@来表示生成的目标文件。当make执行时,它会自动将实际的文件名代入这些自动化变量中,从而无需硬编码文件名。

2.3.2 内置函数及其高级用法

Makefile提供了许多内置函数,用于字符串处理、文件名操作、条件判断、信息查询等。

函数的使用格式:

- $(function arguments)

例如,使用wildcard函数获取当前目录下所有的.c文件:

- SRC=$(wildcard *.c)

使用patsubst函数,对某个变量中