FPGA JFM7K325T系统集成秘笈:打造高效系统的关键步骤

发布时间: 2024-12-01 16:36:24 阅读量: 36 订阅数: 25

FPGA JFM7K325T官方中文技术手册.pdf

参考资源链接:[复旦微电子JFM7K325T FPGA技术手册:亿门级创新架构解析](https://wenku.csdn.net/doc/6401ad32cce7214c316eea68?spm=1055.2635.3001.10343)

# 1. FPGA JFM7K325T系统集成概览

## 简介

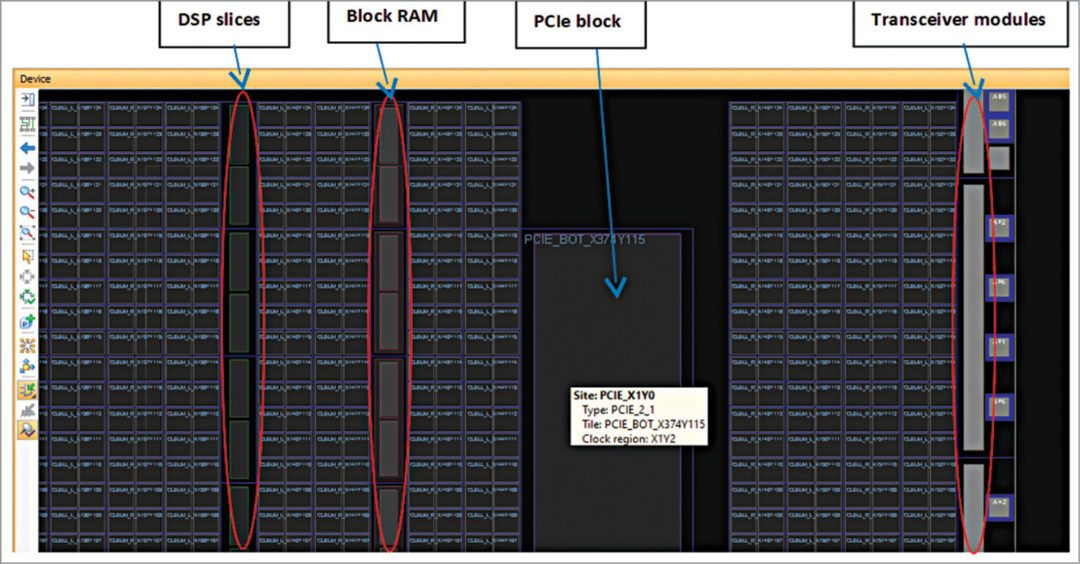

FPGA(现场可编程门阵列)凭借其可重配置性和高效处理能力,在系统集成中扮演着核心角色。JFM7K325T作为一种先进的FPGA,提供了丰富的逻辑单元、存储块以及高速通信接口,使得它在复杂系统集成中得以广泛应用。

## 系统集成的重要性

系统集成不仅仅是指硬件和软件的物理连接,它还涵盖了不同系统组件之间的协同工作和数据交换,以实现预定功能。FPGA在其中承担了逻辑处理、信号转换和高速数据处理等关键任务。

## JFM7K325T的潜力

JFM7K325T FPGA因其高密度逻辑资源、多通道高速接口以及强大的时序约束支持,被广泛应用于高性能计算、通信基础设施和嵌入式系统中。通过系统集成,JFM7K325T能够提升整个系统的性能和响应速度。

在本章中,我们将对JFM7K325T FPGA在系统集成中的应用有一个整体认识,了解其在不同行业的应用案例及其优势所在。这将为后续章节中的接口连接、编程技巧、性能优化等深入分析打下坚实基础。

# 2. 硬件与FPGA的接口连接

### 2.1 JFM7K325T FPGA接口类型解析

FPGA与硬件之间的接口连接是实现高效系统集成的关键。JFM7K325T FPGA支持多种接口标准,它们的电气特性、连接方式和应用场景不尽相同。下面将逐一分析JFM7K325T FPGA的接口类型。

#### 2.1.1 接口标准与电气特性

JFM7K325T FPGA支持诸如LVTTL、LVCMOS、LVDS、HSTL等接口标准,它们各自的电气特性对系统设计至关重要。

- **LVTTL/LVCMOS**: 低电压晶体管-晶体管逻辑(LVTTL)和低电压互补金属氧化物半导体(LVCMOS)标准,适合TTL和CMOS兼容的应用。其典型供电电压为3.3V和1.8V。

- **LVDS**: 低压差分信号(LVDS)支持高速信号传输,并具备低功耗特性。常用在高性能通信系统中,工作电压一般为2.5V。

- **HSTL**: 高速晶体管-晶体管逻辑(HSTL)提供高带宽信号传输,适用于高性能存储器接口。工作电压多为1.5V和1.8V。

不同接口标准的电气特性直接影响到信号的传输质量与系统的整体性能。

#### 2.1.2 接口设计最佳实践

设计接口时需要考虑以下最佳实践,以确保可靠性和性能:

- **阻抗匹配**:为减少信号反射和电磁干扰,需要在PCB布线时考虑阻抗匹配。

- **信号完整性**:在高速信号路径中,应使用差分信号设计来提高信号的可靠性。

- **电源隔离**:对于模拟和数字电路混合的设计,应使用隔离电源来减少噪声。

- **布局布线**:根据信号的频率和重要性进行布局布线优化,尽可能缩短高速信号线的长度。

### 2.2 信号完整性与电源管理

#### 2.2.1 信号完整性问题与对策

信号完整性(SI)是指信号在传输过程中保持其质量的能力。差的信号完整性会导致信号失真、时序错误或系统不稳定。

- **串扰**:相邻信号线之间的电磁耦合会引起串扰。可以通过使用地平面隔离、调整走线间距来减少串扰。

- **反射**:由于阻抗不匹配导致信号反射。合理设计PCB布局和使用终端匹配电阻可以有效降低反射。

- **同步开关噪声(SSN)**:大电流开关会产生的噪声,需要通过优化布线和使用去耦电容来控制。

#### 2.2.2 电源设计要点和稳定性保障

电源设计对整个系统稳定性至关重要。在设计时,需要考虑以下要点:

- **供电噪声控制**:使用合适的去耦电容和稳压器,减少供电噪声。

- **电源平面和地平面**:PCB中的电源平面和地平面有助于降低电源阻抗并减少电磁干扰。

- **多电源域设计**:根据不同的模块需求设计多个电源域,确保电源的稳定供应。

### 2.3 硬件接口调试技巧

硬件接口调试是将FPGA与硬件正确连接的关键步骤。下面介绍调试过程中的关键技巧和工具。

#### 2.3.1 使用示波器和逻辑分析仪

调试过程中,示波器和逻辑分析仪是最常用的工具:

- **示波器**:用于测量和分析信号的时序。可以用来检查信号完整性,如上升/下降时间、过冲、下冲等。

- **逻辑分析仪**:能同时观察多个信号状态,特别适合调试时序敏感的信号。

#### 2.3.2 调试流程和常见问题排除

调试流程应包含以下步骤:

- **检查硬件连接**:确保所有接口连接正确无误。

- **初始化测试**:加载FPGA配置并进行基本功能测试。

- **信号跟踪**:使用示波器或逻辑分析仪追踪关键信号。

- **问题排除**:识别问题并进行修复。常见的问题包括信号不稳、时序问题、电源噪声等。

接下来,将对调试工具的使用提供具体操作指导和代码示例。

# 3. FPGA编程基础与高级技巧

## 3.1 HDL编程语言精讲

### 3.1.1 VHDL和Verilog基础语法

硬件描述语言(HDL)是用于描述数字逻辑系统的语言,FPGA开发主要使用VHDL和Verilog两种语言。VHDL是较早出现的语言,语法复杂,适合复杂系统的描述。Verilog语言简单易学,应用广泛。两者在使用上有许多相似之处,但各有特点。

VHDL的典型结构包括实体(entity)、架构(architecture)和配置(configuration)。实体定义接口,架构描述其行为或结构,配置用于实例化组件。

Verilog的模块是其基础构件,类似于VHDL中的实体和架构。它使用不同的关键字如`module`和`endmodule`来定义模块的开始和结束。

在编程时,应避免常见的陷阱,如逻辑门的生成不使用`for`循环、避免在`always`块内创建不必要的竞争条件等。

### 3.1.2 代码优化和模块化设计

编写高效的HDL代码是成功FPGA项目的基石。代码优化意味着减少资源的使用,提升运行速度,同时保证代码的可读性和可维护性。模块化设计是一种常用的方法,它涉及将复杂系统拆分成小型、独立

0

0