【内存控制器交互】:UDIMM设计中的芯片组协同工作原理

发布时间: 2025-01-08 16:15:33 阅读量: 8 订阅数: 15

UDIMM 原理图参考设计

# 摘要

本文详细探讨了UDIMM内存技术的交互概念、架构及优化策略。首先介绍了UDIMM的基本概念和设计原则,然后深入讲解其工作原理、电气特性,并与内存控制器的协同工作进行了分析。文章进一步讨论了提升UDIMM性能的策略,包括内存带宽和延迟的优化方法、兼容性和稳定性测试,以及在不同平台应用的案例分析。最后,展望了UDIMM设计的未来趋势和挑战,涵盖了技术发展方向、面临的挑战与机遇,以及对未来内存控制器设计的展望。

# 关键字

UDIMM内存技术;内存控制器;数据读写过程;信号完整性;内存带宽;芯片组交互协议

参考资源链接:[DDR5 UDIMM原理图详解与关键连接改动](https://wenku.csdn.net/doc/72bwgidq1y?spm=1055.2635.3001.10343)

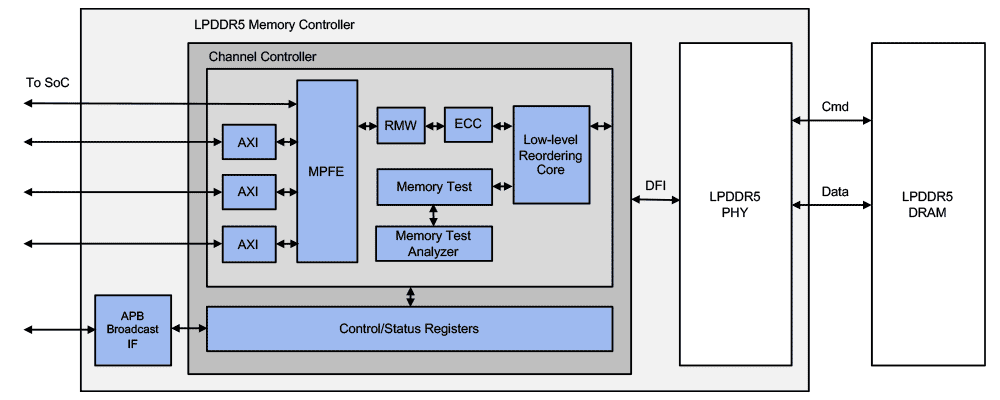

# 1. 内存控制器交互的基本概念与架构

在现代计算机系统中,内存控制器与内存之间的高效互动是确保系统性能的关键因素之一。本章将介绍内存控制器的基本概念,以及它与CPU及其他系统组件之间的交互架构。

## 1.1 内存控制器的角色和功能

内存控制器是负责管理计算机内存的硬件组件,主要负责数据的传输与存取控制。它是连接CPU和内存的桥梁,确保数据能够准确、高效地在两者之间传递。

## 1.2 内存控制器的工作原理

在内存控制器与内存模块之间,存在一整套精密的信号传输协议。这些协议定义了数据、地址和控制信号的传输方式,以及如何确保数据的完整性。

## 1.3 内存子系统架构

内存子系统不仅包括内存控制器和内存模块,还包括内存的物理排列、通道配置和内存的纠错技术。这些组件的交互设计,直接关系到系统的性能表现。

## 1.4 内存访问过程和优化

内存访问过程通常涉及地址解析、数据缓存和预取技术。对内存访问路径的优化是提升系统整体性能的有效手段。内存控制器的设计目标是最大限度地减少延迟并提高吞吐量。

接下来的章节将深入探讨内存技术的各个方面,为读者提供一个全面的内存控制器交互系统视角。

# 2. UDIMM内存技术详解

## 2.1 UDIMM的设计原则和特点

### 2.1.1 UDIMM技术的起源和发展

UDIMM(Unbuffered DIMM)技术是内存技术的一个重要分支,它诞生于上世纪九十年代,当时随着计算机性能的不断提高,传统的内存技术已无法满足高速发展的需求。UDIMM作为一种新型的内存条设计,它具有更高的数据传输速率和更优的数据处理能力,因此得到了快速的发展。

UDIMM的设计原则是简化内存子系统的结构,不使用缓冲器(Buffer),直接与内存控制器进行通信。这种设计使得内存条能够更直接、更快速地响应CPU的请求,从而提高了整体的系统性能。相较于带有缓冲器的内存模块(如RDIMM),UDIMM在设计上更为简洁,成本也相对较低。

随着技术的演进,UDIMM的设计也不断得到改进,从最初的支持DDR(双倍数据速率)内存到现在的DDR4甚至未来的DDR5,UDIMM都跟随时代的步伐进行着更新换代。此外,随着集成电路技术的发展,UDIMM的存储密度也得到了显著的提升,现在我们可以看到容量更大的UDIMM内存条,它们支持更多计算任务的运行。

### 2.1.2 UDIMM与其它内存技术的比较

UDIMM的设计虽然简单,但在与其它内存技术比较时也存在一些劣势。例如,由于没有使用缓冲器,UDIMM在数据传输过程中可能会出现信号衰减,尤其在数据传输距离较长或者内存条数量较多的情况下,这种信号完整性问题会变得更加明显。这就限制了UDIMM在大型服务器和工作站等需要大量内存条的场合的应用。

相对而言,使用缓冲器的RDIMM(Registered DIMM)虽然增加了成本,但它通过缓冲器提供的信号加强和时间延迟补偿,可以支持更多内存条的稳定运行,适合大规模的内存扩展。因此,在服务器环境中,RDIMM通常比UDIMM更受欢迎。

此外,LRDIMM(Load Reduced DIMM)是另一种内存技术,它结合了UDIMM和RDIMM的特点。LRDIMM使用了一个特殊的缓冲器来减少内存系统的负载,但不像RDIMM那样对数据进行完整记录,因此它可以在提高内存容量的同时,保持较低的延迟和较好的信号完整性。

## 2.2 UDIMM内存的工作原理

### 2.2.1 UDIMM的数据读写过程

UDIMM的数据读写过程是计算机内存系统中不可或缺的一环。当CPU需要读取或写入数据时,它会通过内存控制器发出相应的请求。UDIMM接收到这些请求后,会根据内存控制器的指令来访问相应的内存单元,执行读写操作。

读取数据时,数据会从内存单元通过数据总线传输到内存控制器,再由控制器转发至CPU。写入数据时,CPU会将数据发送给内存控制器,控制器将数据放置在数据总线上,数据随后被写入到指定的内存地址中。这一过程是由内存时序参数严格控制的,以保证数据的正确性和一致性。

由于UDIMM不使用缓冲器,其数据读写速度主要取决于内存条本身的电气特性,以及内存控制器的设计。随着技术的进步,UDIMM的设计也在不断优化,以提高数据传输速率和降低读写延迟。

### 2.2.2 UDIMM的信号完整性问题

在UDIMM的工作过程中,信号完整性问题是需要特别关注的。信号完整性是指信号在传输过程中保持其原始特性的能力,包括幅度、形状和同步性。由于UDIMM没有缓冲器来补偿信号衰减,因此在高速运行时信号完整性会受到更严峻的挑战。

信号完整性问题主要受到两个因素的影响:系统阻抗不匹配和串扰。系统阻抗不匹配可能导致信号反射,影响数据的准确性。串扰则是在高密度内存布局中信号之间的互相干扰,这在多通道内存系统中尤为突出。

为了缓解这些问题,UDIMM的设计中会包含一些特殊的设计,如终结电阻(Terminators)、差分信号传输(Differential Signaling)和材料的选择等。这些技术有助于减少反射、降低串扰并提高信号质量。

## 2.3 UDIMM内存的电气特性

### 2.3.1 电气规格参数解析

UDIMM内存条的电气规格参数是内存系统正常运行的基础,它规定了内存条工作时的电压、时序、电流等关键参数。最基础的电气特性参数包括VDD和VDDQ,分别表示内存核心电压和IO电压。例如,标准的DDR3 UDIMM通常使用1.5V的VDD和1.5V的VDDQ,而DDR4 UDIMM则降低至1.2V。

除了电压外,时序参数也是决定UDIMM性能的关键。时序参数包括CAS Latency(列地址选通延迟)、RAS to CAS Delay(行地址选通到列地址选通延迟)、RAS Precharge Delay(行地址预充电延迟)等。这些参数表示内存控制器在执行读写操作时,各操作之间的时间间隔。较小的时序数值意味着更快的内存响应速度。

电流参数则关系到内存的功耗,UDIMM的功耗通常较低,这是因为它没有缓冲器和终结器等额外组件。然而,较低的功耗也意味着UDIMM可能无法承受高密度内存配置的电气负载。

### 2.3.2 电源管理和热设计

电源管理在UDIMM内存的设计中占据了重要位置。由于计算机系统需要最小化能耗,同时确保性能的发挥,UDIMM采用了多种电源管理技术。比如,现代UDIMM支持多种电源状态,包括Active State Power Management (ASPM) 和 Latency Reduction Technology (LRT),以在空闲时降低内存子系统的功耗。

热设计同样至关重要,因为它关系到内存条在长时间运行下的稳定性。UDIMM的设计必须确保良好的散热能力,防止过热导致的性能下降或硬件损坏。这通常通过合理的布局、使用散热材料如铝质散热片、以及在

0

0