时序闭合策略与挑战: TimingDesign的全方位解读

发布时间: 2025-01-08 17:00:21 阅读量: 7 订阅数: 13

深度解读!时序数据库HiTSDB:分布式流式聚合引擎

# 摘要

本文全面介绍了时序闭合策略的基础概念、理论框架、实践应用、高级技巧及未来发展趋势。通过阐述时序闭合的目标与意义,分析了其在集成电路设计中的关键作用,并深入探讨了时序分析和时钟域交叉同步器设计的理论基础。文章详细介绍了时序闭合的工具和技术,并通过具体案例,展示了在设计和后端实现阶段成功应用时序闭合策略的实例。高级时序闭合技术、多时钟域设计分析以及与时序闭合相关的功耗优化方法也在文中得到讨论。最后,本文展望了时序闭合在物联网和人工智能领域的新需求,分析了未来工具的发展趋势,并强调了教育与培训在推动时序闭合技术进步中的重要性。

# 关键字

时序闭合策略;集成电路设计;时序分析;时钟域交叉;功耗优化;案例研究

参考资源链接:[TimingDesigner 9.0用户指南:静态时序分析工具](https://wenku.csdn.net/doc/2uqwto3z7j?spm=1055.2635.3001.10343)

# 1. 时序闭合策略的基础概念

时序闭合策略是集成电路设计中的一个关键概念,它涉及确保芯片内部所有信号路径的时间延迟符合设计规范的过程。这一策略对于防止数据丢失或损坏至关重要,因为电路中的信号必须在预定的时间内稳定下来,以确保系统的稳定运行。时序闭合策略的实施通常在芯片设计的后端阶段进行,涉及到时序分析、优化以及验证等步骤。在深入探讨之前,了解时序闭合的基础概念对于每个IT专业人员来说都是至关重要的。

# 2. 时序闭合的理论框架

## 2.1 时序闭合的目标与意义

### 2.1.1 时序闭合在集成电路设计中的作用

时序闭合是集成电路设计中的一项关键技术,它确保数据在各个时钟周期内正确地传输和处理,从而保障整个系统的稳定运行。在数字电路设计中,时序闭合的任务是调整电路元件的时序,以满足设计的时序要求,包括建立时间(setup time)和保持时间(hold time)的约束。

为了实现时序闭合,设计师需要使用各种时序优化技术,比如调整路径延迟、使用pipelining技术、或使用时钟域交叉技术。这些技术的关键是确保数据在时钟边沿到来之前稳定地到达寄存器,这样电路才能按预期正常工作。若未实现时序闭合,电路可能会出现时序错误,从而导致数据的错误或者系统崩溃。

### 2.1.2 时序闭合的目标定义

在定义时序闭合的目标时,需要考虑以下几个关键点:

- **满足时序约束**:时序闭合的首要目标是确保所有的时序路径都能满足预先设定的时序约束。

- **性能优化**:在满足时序要求的基础上,进一步优化电路性能,包括缩短路径延迟、减少功耗等。

- **资源平衡**:在资源有限的情况下,平衡时序优化与逻辑单元、存储单元等资源的使用,避免过度优化导致资源浪费。

- **功耗考量**:由于时序闭合可能涉及添加额外的逻辑,这会增加功耗。因此在设计时序闭合方案时,应考虑对功耗的影响。

实现时序闭合不仅需要考虑技术层面,还涉及到成本、资源、功耗等多方面的权衡,这就需要综合运用各种技术手段和优化策略。

## 2.2 时序闭合的理论基础

### 2.2.1 时序分析的基本原理

时序分析是时序闭合过程中的重要组成部分,它涉及到对电路中所有可能的数据路径进行检查,以确保数据在规定的时间内从一个寄存器传输到另一个寄存器。

在进行时序分析时,通常会使用静态时序分析(Static Timing Analysis, STA)工具,它能够自动识别电路中所有可能的数据传输路径,并对每条路径的时序性能进行评估。STA工具会计算出最坏情况下的时序数据,包括最迟到达时间(Late)和最早到达时间(Early),并分析数据是否能在时钟边沿之前稳定到达。

时序分析通常关注以下几个关键时序参数:

- **建立时间(setup time)**: 信号需要在触发器的时钟边沿之前稳定停留的最小时间。

- **保持时间(hold time)**: 信号在触发器的时钟边沿之后保持稳定状态的最小时间。

- **时钟到输出时间(clock-to-output time)**: 时钟边沿之后,数据输出端口上数据有效的延迟时间。

进行时序分析时,需要考虑实际电路中可能出现的各种延迟,例如门延迟(gate delay)、线延迟(interconnect delay)、以及由于工艺、电压和温度变化导致的延迟变化。

### 2.2.2 时钟域交叉与同步器设计

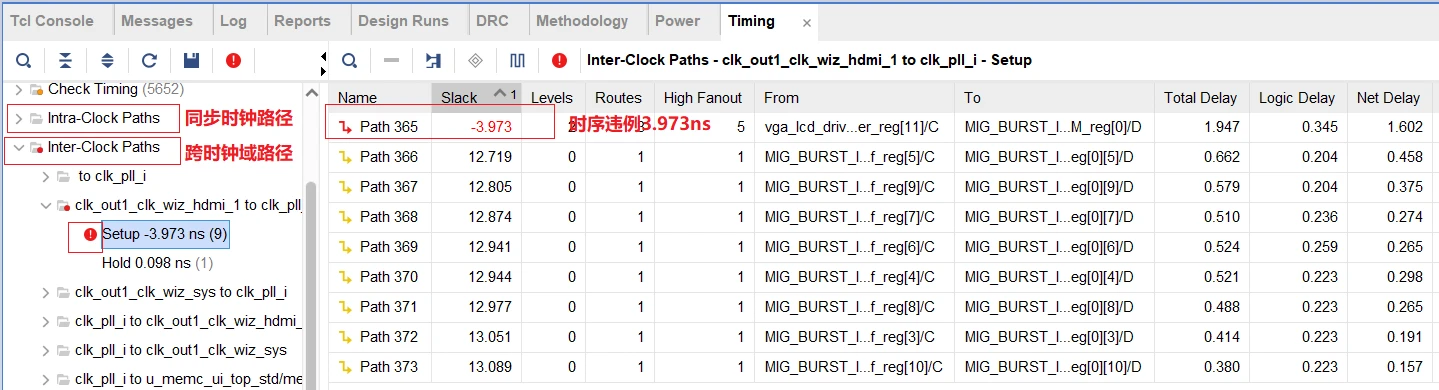

在现代集成电路设计中,由于功能的复杂性,往往会存在多个不同的时钟域。这些不同的时钟域之间的信号交互可能导致时序问题,特别是时钟域交叉(Clock Domain Crossing, CDC)问题。

时钟域交叉问题是指来自一个时钟域的信号在另一个时钟域的不适当时间点被采样,可能导致信号的不确定性,甚至引起电路的不稳定。因此,设计有效的同步器(synchronizer)至关重要,以确保信号在时钟域之间正确传递。

同步器设计中常用的结构包括:

- **两级触发器同步器**:是最基本的同步器设计,用于将信号从一个时钟域同步到另一个时钟域,但不能完全防止亚稳态问题。

- **异步FIFO**:对于高速、高带宽的数据传输,异步FIFO(First-In-First-Out)是常用的解决方案,它能够在不同的时钟域之间安全地传输数据。

- **握手协议**:当两个时钟域之间需要双向通信时,握手协议提供了有效的同步机制。

进行时钟域交叉分析时,需要识别所有潜在的时钟域交叉点,并应用适当的同步技术来避免可能出现的时序问题。

## 2.3 时序闭合的挑战与应对

### 2.3.1 理论上的挑战分析

时序闭合面临着许多理论上的挑战,这些挑战源自于设计的复杂性、时钟域的数量以及工作频率的提高。理论上,工程师需要面对以下挑战:

- **设计复杂性**:随着集成电路功能的增加,其结构变得更加复杂,时序闭合的难度也随之提高。

- **时钟域管理**:在多时钟域设计中,合理管理时钟域间同步变得尤为重要。

- **工艺变异性**:随着工艺节点的缩小,制造过程中的变异对时序闭合的影响越来越显著。

- **功耗与性能的权衡**:优化时序闭合时,必须考虑电路的功耗,避免因追求时序的极致优化而带来过高的功耗。

### 2.3.2 实际案例的挑战应对策略

在实际项目中,时序闭合的挑战可能包括时序违规、时钟域交叉问题、以及设计与实现之间的不匹配等。为了应对这些挑战,设计团队通常会采取以下策略:

- **早期时序验证**:在设计早期阶段就开始进行时序验证,可以及早发现潜在的时序问题。

- **使用高级工具**:使用先进的STA工具和时序优化工具,能够帮助设计师更加准确地识别和解决问题。

- **设计迭代**:在设计过程中不断迭代优化,确保时序闭合策略的有效性。

- **跨团队合作**:与设计、验证、实现等部门紧密合作,确保时序闭合策略得到全面考虑和实施。

通过这些策略,团队能够更高效地解决实际项目中遇到的时序闭合挑战,保证集成电路设计的成功交付。

# 3. 时序闭合策略的实践应用

## 3.1 时序闭合的工具和技术

在集成电路设计的实践中,时序闭合的实现依赖于一系列的工具和技术。有效的工具可以帮助设计者识别和解决时序问题,而技术则是实现时序闭合的途径。

### 3.1.1 时序分析工具介绍

时序分析工具是实现时序闭合的关键,它们在设计过程中扮演着重要角色。这些工具通过静态时序分析(STA)来检查设计中的时序路径是否满足时序要求。STA可以自动识别时序违规,并帮助设计者优化设计以满足时序约束。

常见的时序分析工具有:

- PrimeTime(PT):由Cadence提供,广泛应用于ASIC设计中。

- Tempus:由Synopsys提供,支持复杂的时序分析。

- ETS(Early Timing Signoff):为快速时序签收提供解决方案。

以PrimeTime为例,其使用通常包括以下步骤:

1. 读取设计的详细信息。

2. 应用时序约束,包括时钟定义、输入/输出延迟等。

3. 运行STA以分析时序。

4. 识别违反时序约束的路径。

5. 根据STA的结果进行优化。

```shell

# 示例命令:在PrimeTime中读取设计并应用时序约束

pt_shell> read_design - liberty my_design.lib

pt_shell> set_clock_transition -rise -max 0.2 [get_clocks clk]

pt_shell> set_in

```

0

0