【Vivado 2017硬件验证快车道】:加速产品上市时间的秘诀

发布时间: 2025-01-09 21:40:48 阅读量: 8 订阅数: 11

vivado 2017.4 下SRIO license,经验证真实有效

# 摘要

本文全面介绍了Vivado 2017在硬件验证领域的应用,从基础使用到高级技术,再到实践应用和优化技巧。首先概述了Vivado 2017的硬件验证概貌,然后详细探讨了其界面、基本操作、仿真环境的搭建以及仿真流程和调试方法。接着,深入讲解了SystemVerilog语言在Vivado中的应用、硬件加速仿真原理及实现、以及FPGA原型验证的流程和案例。第四章聚焦于Vivado在SoC验证和高性能计算中的具体应用和案例分析。第五章则分享了性能优化方法和设计重用及模块化设计的实践。最后,展望了Vivado 2017未来的发展趋势,特别是在AI、5G等新兴应用领域的应用前景。

# 关键字

Vivado 2017;硬件验证;仿真环境;SystemVerilog;FPGA原型验证;性能优化

参考资源链接:[Vivado 2017 FPGA程序固化全面指南](https://wenku.csdn.net/doc/6412b4afbe7fbd1778d4072d?spm=1055.2635.3001.10343)

# 1. Vivado 2017硬件验证概述

## 1.1 Vivado 2017的作用与重要性

Vivado 2017是Xilinx公司推出的集成设计环境(IDE),它革新了FPGA设计流程,提供了从逻辑设计到硬件实现的全流程解决方案。相比其前代产品ISE,Vivado带来了显著的性能提升,尤其在处理大规模设计时更加高效。本章旨在为读者提供Vivado 2017硬件验证的总体概念,以及它在现代数字设计中的关键作用。

## 1.2 硬件验证的必要性

硬件验证是确保设计符合规格要求的至关重要的步骤。Vivado 2017通过提供一套完整的仿真和调试工具,使得设计者能够在将设计烧录到FPGA之前验证其功能和性能。它支持多种验证方法,包括功能仿真、时序仿真和硬件加速仿真,从而允许设计者从多方面确保设计的正确性。

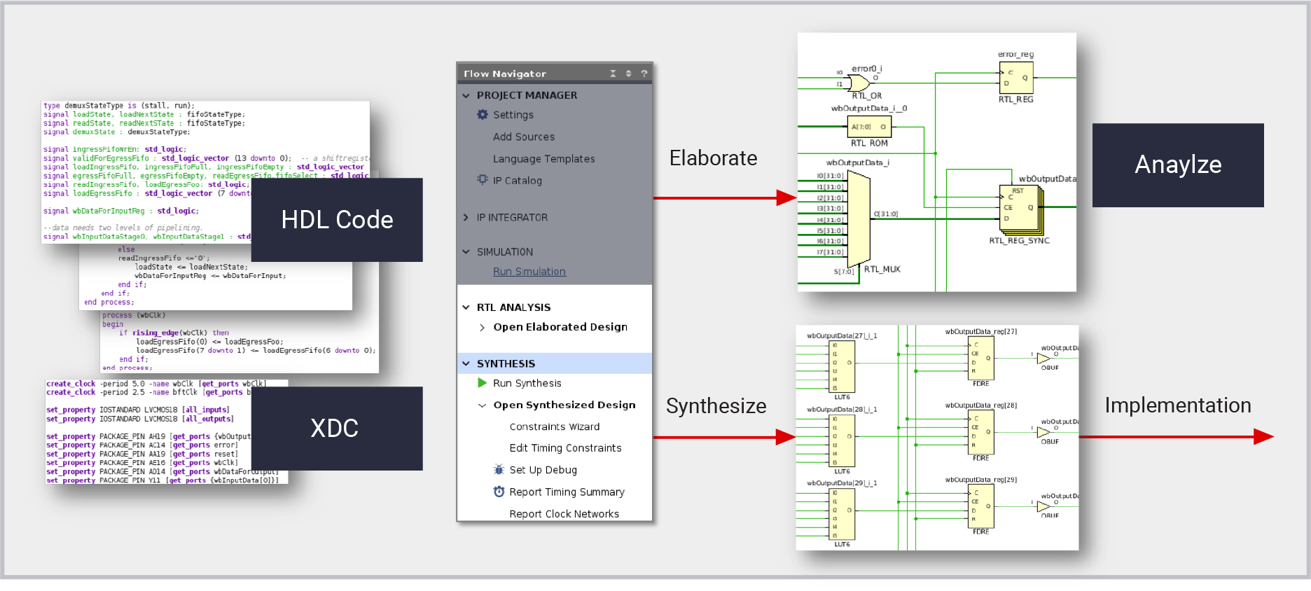

## 1.3 验证流程的基本步骤

在进行硬件验证时,设计师通常遵循以下基本步骤:首先,利用Vivado的HDL编写设计代码并进行初步仿真;其次,使用Vivado内置的综合工具进行设计综合;然后,通过实现工具将综合后的设计映射到目标FPGA器件;最后,利用Vivado提供的仿真环境进行全系统的仿真测试。通过这一流程,设计者可以确保设计在真实硬件上的表现与预期一致。

# 2. Vivado 2017的基础使用

## 2.1 Vivado 2017的界面介绍和基本操作

### 2.1.1 Vivado的用户界面布局和功能模块

Vivado是由Xilinx推出的全新一代FPGA设计套件,旨在提供更为高效、直观的设计流程。从版本2017开始,Vivado进一步完善了用户体验,并引入了一系列创新的功能。Vivado的用户界面(UI)是其用户友好型的一个重要体现。该界面布局清晰、模块功能明确,便于用户快速掌握和操作。

在UI的顶部,Vivado提供了一个强大的菜单栏,涵盖了设计流程中所需的所有功能,如File、Edit、Project、IP、Implementation等。这些菜单提供了对应的操作入口,可以快速调用各种设计、仿真、综合、布局布线等工具和功能。

界面的左侧是项目浏览器(Project Manager),在这里可以创建和管理项目、文件以及设计库等。用户可以直观地看到整个项目的层次结构,并能够进行各种项目相关的操作。

右侧是信息和日志窗口,这一部分主要包括console、message、report等标签页。console用于显示当前的命令行输出,message用于显示编译信息及错误信息,而report则提供了丰富的设计信息,包括但不限于时序分析、资源使用情况等。

界面的底部是Tcl控制台,用户可以通过Tcl语言来控制Vivado的运行,这一点对于高级用户来说非常有用,因为它允许通过脚本自动化设计流程。

在Vivado的右侧,还设置了部件(IP)库和仿真工具等,设计者可以在此进行IP核的生成与管理、仿真模型的创建等操作。

### 2.1.2 Vivado的基本操作和项目管理

在Vivado中,基本操作包括项目创建、文件添加、设计输入、仿真运行等。首先需要创建一个项目,Vivado的“Create Project”向导会引导用户完成项目配置,包括选择FPGA设备、设定项目名称和位置等。

接下来,设计者需要添加设计文件到项目中,这些文件可以是Verilog或VHDL等硬件描述语言编写的源代码。在项目中,可以对这些设计文件进行管理,包括查看、编辑、编译等操作。

仿真作为验证设计的关键步骤,Vivado提供了集成的仿真环境。设计者可以在这个环境中进行仿真测试、波形查看、信号调试等操作,保证设计的正确性。在进行仿真之前,通常需要编写测试平台(testbench),这是对设计进行仿真的基础。

项目管理则是Vivado中的另一项重要功能。设计者可以在项目管理器中查看项目的所有文件和资源,进行组织和管理。对于大型项目,合理的项目结构和资源管理可以提高开发效率。

为了在不同模块间高效共享设计,Vivado还支持IP重用。设计者可以生成自己的IP核,或者使用Xilinx提供的IP核库,这些IP核可以被集成到自己的设计中,加速开发过程。

以下是Vivado添加Verilog文件到项目的一个简单实例:

```verilog

// example.v file content

module example (

input wire clk,

input wire rst,

output reg [7:0] out_data

);

// 一个简单的计数器设计

always @(posedge clk or posedge rst) begin

if(rst) begin

out_data <= 8'b0;

end else begin

out_data <= out_data + 1;

end

end

endmodule

```

在Vivado中添加上述Verilog文件的步骤可以分为:

- 打开Vivado并创建一个新项目,选择合适的FPGA芯片型号。

- 在“Sources”窗口中,右键点击项目名称,选择“Add Sources”。

- 选择“Add or create design sources”,点击“Create File”。

- 在弹出的窗口中输入文件名`example.v`,点击“Finish”。

- 将上述Verilog代码粘贴到Vivado提供的代码编辑器中,并保存。

之后就可以对这个文件进行编译,检查语法错误,并进行后续的设计和仿真操作。

通过基本操作的步骤可以看出,Vivado的用户界面和项目管理方式设计得非常直观,便于用户上手和操作。而对于项目管理而言,一个清晰的管理界面可以帮助设计师维护和组织代码,这对于大型项目尤其重要。

## 2.2 Vivado 2017的仿真环境搭建

### 2.2.1 Vivado的仿真模型和测试平台

仿真环境是设计验证过程中的关键步骤之一,在Vivado中,仿真模型可以是实体(entity)和行为(behavior)的组合。在创建测试平台之前,需要理解设计的接口以及如何与设计中的实体进行交互。

Vivado提供了一个集成的仿真环境,允许用户直接在Vivado内部进行设计验证,无需第三方仿真工具。仿真环境支持多种仿真方法,包括功能仿真(Functional Simulation)、时序仿真(Timing Simulation)等,其中功能仿真验证逻辑功能的正确性,时序仿真则同时考虑了时序因素。

为了进行仿真,首先需要编写测试平台(Testbench)。测试平台是一个专门为了测试设计而设计的模块,它通常包含模拟信号源、驱动信号给被测试模块,并观察响应输出是否符合预期的逻辑行为。在Vivado中,测试平台可以使用Verilog或VHDL编写。

以下是使用Verilog编写的一个简单测试平台例子:

```verilog

`timescale 1ns / 1ps

module example_tb;

reg clk;

reg rst;

wire [7:0] out_data;

// 实例化待测试模块

example uut (

.clk(clk),

.rst(rst),

.out_data(out_data)

);

// 生成时钟信号

initial begin

clk = 0;

forever #5 clk = ~clk;

end

// 测试序列

initial begin

// 初始化

rst = 1; #10;

rst = 0;

// 等待一段时间观察输出

#100;

$finish;

end

// 观察输出

initial begin

$monitor("Time: %t, out_data = %d", $time, out_data);

end

endmodule

```

### 2.2.2 Vivado的仿真流程和调试方法

Vivado的仿真流程可以分为以下步骤:

1. 设计输入:首先需要在Vivado中创建设计文件,并输入相应

0

0