【双稳态触发器应用】:构建稳定十进制计数器的秘诀

发布时间: 2024-12-17 06:00:18 订阅数: 2

参考资源链接:[西南交通数电:十进制可逆计数器设计与实现](https://wenku.csdn.net/doc/4kw3ievq3g?spm=1055.2635.3001.10343)

# 1. 双稳态触发器基础介绍

## 1.1 双稳态触发器的定义

双稳态触发器,简称触发器,是数字电子技术中一种具有两个稳定状态的逻辑电路。这两个状态可以表示二进制的“0”和“1”,并且能够在外部信号的作用下从一个状态翻转到另一个状态。

## 1.2 触发器的历史与发展

触发器的历史可以追溯到20世纪40年代,它在现代电子计算机的发展中起到了基石的作用。早期的触发器多为机械或机电结构,但随着晶体管技术的发展,触发器实现了小型化和更高的运算速度,这极大推动了现代数字电路的进步。

## 1.3 常见双稳态触发器类型

常见的双稳态触发器类型包括RS触发器、JK触发器、D触发器和T触发器。每种触发器根据其逻辑结构和功能特点,在不同的应用场景中扮演着关键角色。例如,D触发器在数据锁存和时序控制中非常常用,而JK触发器则因为其通用性在复杂的逻辑设计中受到青睐。

# 2. 双稳态触发器在数字逻辑中的应用

## 2.1 双稳态触发器的工作原理

### 2.1.1 触发器的基本概念和类型

双稳态触发器(Bistable Multivibrator),也被称为双稳态电路或锁存器(Latch),是一种能够存储一位二进制信息(0或1)的数字逻辑电路。它具有两个稳定的状态,可以通过外部信号的控制在两个状态之间切换。双稳态触发器是数字系统中实现存储功能的基础组件。

触发器的类型通常分为两大类:

1. SR(Set-Reset)触发器:通过Set和Reset输入来控制输出的高低电平。

2. D(Data)触发器:通过一个数据输入(D)来控制输出(Q),在时钟信号边沿时捕捉输入状态。

3. JK触发器:为SR触发器的变种,可以解决SR触发器的不确定状态问题。

4. T(Toggle)触发器:每当输入信号边沿到来时,输出状态就会翻转。

### 2.1.2 触发器的电路模型和逻辑功能

在电路模型中,触发器由门电路、晶体管、电阻和电源等基本电子元件组成。触发器的逻辑功能依赖于这些元件如何组织和相互作用。例如,一个简单的D触发器可以使用两个NAND门或两个NOR门来构建。这些门电路的组合能够存储一个位的数据,并且可以响应时钟信号进行状态切换。

下面展示了一个基本的D触发器的电路模型图示:

```mermaid

graph TD

S1["S = 1 (Set)"] -->|AND| G1["G1"]

S0["S = 0 (Reset)"] -->|AND| G2["G2"]

D["D (Data Input)"] -->|AND| G1

D -->|AND| G2

clk["CLK (Clock)"] -->|AND| G1

clk -->|AND| G2

G1 -->|OR| Q["Q"]

G2 -->|OR| Q

G1 -->|OR| Qn["Q'"]

G2 -->|OR| Qn

```

在这个电路中,Q是输出,Q'是Q的反相信号。D触发器的输出Q会跟随输入D的变化,但是在时钟信号CLK上升沿或下降沿到来时,输出状态才会改变。如果D为高,那么在下一个时钟边沿到来时,Q也会变成高电平;如果D为低,则Q会在下一个时钟边沿到来时变为低电平。

双稳态触发器的逻辑功能是通过组合逻辑门实现的,不同的触发器类型将有各自的逻辑表征,例如JK触发器可以在任意状态通过输入J和K来决定下一个状态是保持当前状态还是翻转状态。触发器的这一特性使其在数字电路中充当了非常重要的角色。

## 2.2 触发器在计数器设计中的角色

### 2.2.1 计数器的基本概念和分类

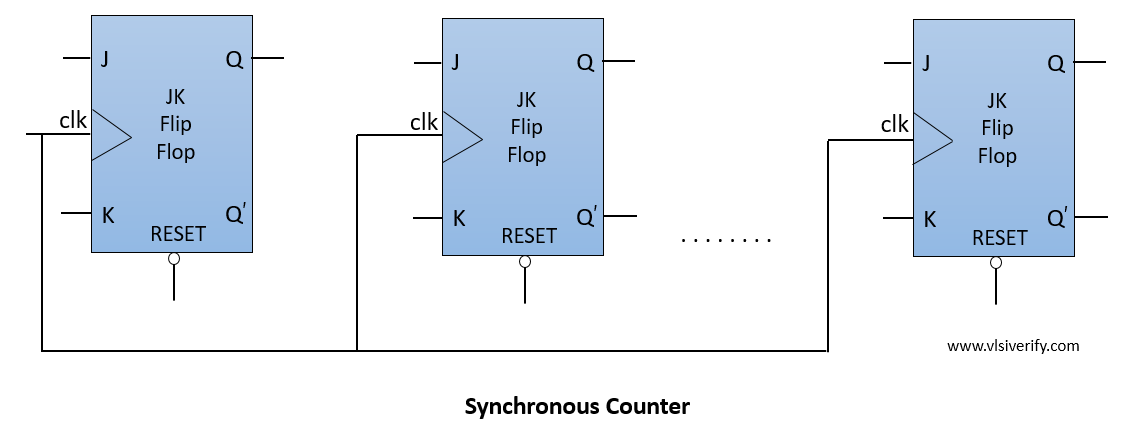

计数器是数字电路中重要的组成单元,它可以用来记录和累计事件发生的次数。根据不同的应用需求,计数器可以分为多种类型,大致可以分为同步计数器和异步计数器:

1. 同步计数器:所有的触发器同时接受来自同一个时钟信号,这使得它们的状态几乎同时发生变化。

2. 异步计数器:时钟信号逐级传递,各个触发器按照不同的时间间隔改变状态。

此外,计数器还按照计数的模式分为:

1. 二进制计数器:按照二进制规则进行计数。

2. 十进制计数器:计数0到9后回绕重新开始。

3. 可逆计数器:不仅可以向上计数,也可以向下计数。

### 2.2.2 触发器如何实现简单的二进制计数

实现一个简单的二进制计数器,最常用的是同步计数器设计。以一个4位二进制计数器为例,其核心是由四个D触发器构成,每个触发器的输出代表一个二进制位,从低位到高位排列。

下面是简化后的同步二进制计数器的逻辑功能描述表格:

| CLK (时钟信号) | Q3 | Q2 | Q1 | Q0 | 输出状态 |

|----------------|----|----|----|----|----------|

| 上升沿 | - | - | - | 0 | 0001 |

| 上升沿 | - | - | 0 | 1 | 0010 |

| 上升沿 | - 0 | 1 | 0 | 0011 |

| 上升沿 | - | 1 | 0 | 1 | 0100 |

| ... | ...|... |... |... | ... |

| 上升沿 | 1 | 0 | 0 | 0 | 1000 |

在此表格中,“-”表示该位的状态在前一个时钟上升沿之后未改变。每一个上升沿,二进制计数器中的Q0位翻转一次。当Q0翻转时,Q1将跟着翻转一次,同理Q2和Q3亦然。这样便实现了对时钟脉冲的计数。

### 2.2.3 计数器的同步与异步工作模式

在同步计数器设计中,所有的触发器同时获得相同的时钟信号,因此它们的动作几乎是同步的。这种设计的优势在于计数过程中非常稳定,且容易理解计数状态。

而在异步计数器设计中,每个触发器(或其他计数单元)仅在前一个触发器的输出变化时才得到时钟信号,从而在计数过程中产生一个较小的延迟。这种设计较同步计数器而言,在高速操作时可能会出现时序上的问题,因为延迟累加可能导致计数错误

0

0