【深入STM32H745ZI内核】:全面解析ARM Cortex-M7架构

摘要

ARM Cortex-M7作为一款高性能的嵌入式处理器,具有复杂的架构和丰富的核心特性,是现代嵌入式系统开发中的重要选择。本文深入介绍ARM Cortex-M7的架构概要、核心组件、中断系统、性能优化策略以及支持的操作系统。通过分析开发环境与工具链的配置,包括GCC编译器、集成开发环境和调试工具,本文为开发人员提供了一套完整的开发指南。此外,文章还探讨了高级编程技术和高级缓存控制方法,并通过实战案例分析,提出了性能优化的实践策略。最后,本文展望了ARM Cortex-M7在行业中的应用前景及未来技术融合的新方向。

关键字

ARM Cortex-M7;架构概要;性能优化;开发环境;RTOS移植;高级缓存控制;硬件加速器;调试技术;性能分析;行业应用前景

参考资源链接:STM32H745zi: 480MHz Cortex-M7 & M4 MCUs with 2MB Flash, 1MB RAM & 46 Interfaces

1. ARM Cortex-M7架构概述

ARM Cortex-M7作为ARM公司推出的高性能处理器,是嵌入式应用中广泛应用的处理器之一。作为本系列文章的第一章节,本部分将简要介绍Cortex-M7的架构,为后续章节中关于核心特性、开发环境、操作系统支持以及性能优化等更为深入的讨论打下基础。

1.1 Cortex-M7简介

Cortex-M7微处理器核心是基于ARMv7E-M架构,具有高性能和高效率的特点。其设计目标是提供一个可预测的指令执行,优化实时系统的响应时间。它具备了超过1.6 DMIPS/MHz的处理能力,并且在某些实现中可以达到高达456 CoreMark的性能。该核心还支持了广泛的内存访问和先进的系统级功能,如处理器间通信、高速缓存和内存保护单元等。

1.2 架构优势

Cortex-M7架构的优势主要体现在以下几个方面:

- **高效性能:**采用改进的流水线设计和高吞吐量,可以快速执行复杂的算法和数据密集型任务。

- **内存优化:**具有灵活的内存配置选项,包括支持的高速缓存和内存保护机制,能提升应用性能的同时保证系统稳定性。

- **实时性能:**内置的硬件加速器和丰富的中断处理机制,让Cortex-M7非常适合于实时操作系统(RTOS)的部署。

接下来的章节中,我们将详细探讨Cortex-M7的这些核心特性,并展示如何在实际的嵌入式项目中发挥这些特性来实现高效的应用开发。

2. ARM Cortex-M7核心特性

2.1 架构核心组件

2.1.1 CPU核心与流水线设计

ARM Cortex-M7作为ARMv7-M架构的高端产品,其CPU核心与流水线设计体现了极致的性能追求。Cortex-M7的CPU核心是32位的,拥有高度优化的五级流水线,可以实现高效的指令处理。其流水线设计对指令级并行处理(ILP)有着极佳的支持,这意味着在相同的时钟周期内,Cortex-M7能够处理更多的指令,从而显著提升性能。

此外,Cortex-M7支持分支预测技术,可以在执行前预测指令流的方向,减少分支导致的流水线空泡。在多任务环境中,这种能力尤为重要,它确保了系统能够平滑地进行上下文切换,同时也支持实时操作系统的高效任务调度。

代码块和逻辑分析:

- // 一个简单的ARM Cortex-M7指令流水线示例

- LDR R0, =0x20000000 // 加载地址到寄存器R0

- LDR R1, [R0] // 从R0指定的地址加载数据到R1

- ADD R2, R1, R1 // 将R1中的值加倍并存储到R2

该代码段展示了从内存加载数据并进行基本算术操作的过程。在Cortex-M7上,由于五级流水线的设计,这些操作可以同时进行,处理器能够在单个时钟周期内完成一个或多个流水线级的任务。每一个流水线阶段(如取指IF、译码ID、执行EX、访存MEM和回写WB)都根据指令的性质进行了优化,以确保高效的数据处理能力。

2.1.2 内存管理单元(MMU)

内存管理单元(MMU)在Cortex-M7中的应用主要体现在对内存访问的控制和保护。MMU在操作系统的支持下,可以提供虚拟内存管理功能,这意味着CPU可以使用大于物理内存大小的地址空间。这对于运行需要大内存支持的应用程序或操作系统来说是非常重要的。

MMU还支持内存保护机制,允许操作系统对不同的内存区域设置访问权限,包括可读、可写、可执行等。此外,MMU还能够对内存进行分页管理,每个页可以配置为不同的保护级别和大小,从而支持更细粒度的内存管理。

2.1.3 高速缓存技术

高速缓存技术对于提升ARM Cortex-M7的性能至关重要,尤其是在处理大量数据和对延迟敏感的应用中。Cortex-M7内置了独立的指令和数据缓存,支持多种缓存策略,包括回写(Write-back)和直写(Write-through)等。

通过高速缓存,处理器能够快速访问频繁使用的数据,减少访问外部存储器的次数,从而大幅度提升整体性能。高速缓存的大小和管理策略对于缓存命中率有着直接影响,合适的配置可以确保缓存效率最大化。

代码块和逻辑分析:

- // 配置Cortex-M7高速缓存的一个简化示例

- void Cache_Configuration(void) {

- // 启用高速缓存

- SCB_EnableICache();

- SCB_EnableDCache();

- // 配置高速缓存大小和策略等

- // 此处省略具体配置代码...

- }

在上述代码中,我们启用并配置了Cortex-M7的指令缓存和数据缓存。实际的高速缓存配置涉及复杂的参数和策略,包括缓存大小、替换策略、预取策略等,这些都需要根据应用场景进行优化。

2.2 中断系统和异常处理

2.2.1 向量中断控制器(NVIC)

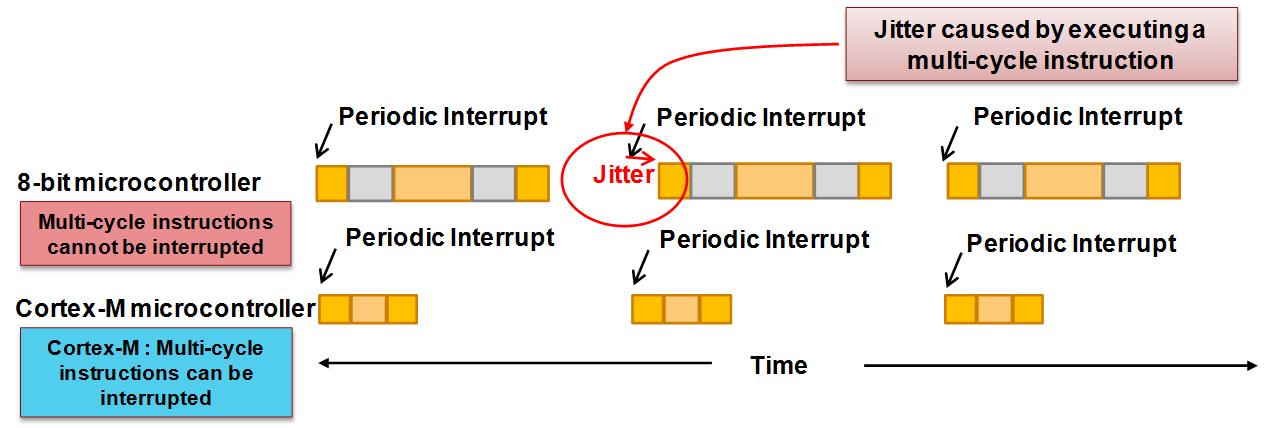

ARM Cortex-M7的向量中断控制器(NVIC)设计用于高效处理中断请求。NVIC具备快速中断响应和低延迟中断处理的能力,这对于实时系统尤为重要。它支持多达240个中断通道,每个通道都可以独立配置优先级,从而实现中断优先级的灵活管理。

NVIC还支持尾链技术(Tail-Chaining),这种机制能够在处理一个中断结束时立即切换到下一个最高优先级的中断,减少中断响应时间。此外,Cortex-M7的NVIC支持动态优先级,允许在运行时根据需要调整中断优先级。

2.2.2 中断优先级和嵌套

Cortex-M7的中断系统支持中断优先级的设置,这意味着可以在系统中实现多个中断同时发生时的优先级管理。通过为每个中断分配一个优先级,系统可以确定哪些中断需要被优先处理,从而保证了实时系统的响应性。

当中断发生时,NVIC负责根据中断优先级决定是否允许嵌套。允许中断嵌套可以进一步提升实时性能,因为它允许高优先级中断打断低优先级中断的处理。通过这种方式,Cortex-M7能够更有效地处理高优先级任务,同时管理低优先级任务的执行。

2.2.3 异常处理流程

ARM Cortex-M7的异常处理流程是高度优化的,设计用于最小化异常响应时间。异常处理包括中断、复位、系统错误等,并且Cortex-M7通过特定的异常向量表来管理这些异常。

当异常发生时,处理器将自动跳转到对应的异常向量地址,并执行预设的异常处理代码。异常处理流程包括保存当前状态、处理异常、恢复状态等步骤。通过精简的异常处理流程和快速的上下文切换,Cortex-M7能够高效地管理异常情况,确保系统的稳定运行。

2.3 性能优化与调试支持

2.3.1 性能基准测试

性能基准测试是评估和优化Cortex-M7性能的关键步骤。通过使用各种性能测试工具和基准测试套件,开发人员可以确定系统的性能瓶颈,并对代码进行优化。性能基准测试不仅关注处理器的处理速度,还包括内存访问效率、缓存利用率、外设性能等多个维度。

2.3.2 调试接口和调试策略

Cortex-M7支持多种调试接口,如JTAG和SWD(串行线调试),这为开发者提供了强大的调试能力。调试器可以访问处理器的寄存器、内存、缓存等核心资源,允许开发者实时监控和控制运行中的程序。

除了基本的断点、步进和内存查看功能外,Cortex-M7还支持更高级的调试策略,如数据断点、性能分析和实时跟踪。这些高级调试功能使得开发人员能够在不影响系统运行的情况下,深入分析程序行为和性能表现。

在实际应用中,开发者通常会结合使用各种调试工具和策略,以确保代码的稳定性和性能最大化。

在接下来的章节中,我们将深入探讨如何针对ARM Cortex-M7的特性和性能特点进行编程和优化,以及如何选择合适的工具进行软件开发和调试。

3. 开发环境与工具链

3.1 工具链安装与配置

3.1.1 GCC编译器与ARM交叉编译

ARM架构的处理器广泛应用于嵌入式系统开发中,因此一个针对ARM架构优化的交叉编译器是开发过程中的必备工具。GCC(GNU Compiler Collection)是自由软件基金会的编译器套件,提供了众多编程语言的支持。针对ARM架构,GCC可以被配置为一个交叉编译器,允许开发者在例如x86架构的机器上编译出适用于ARM处理器的程序。

交叉编译器的安装过程通常涉及以下步骤:

- 下载并安装适用于您的操作系统的基础GCC编译器。

- 下载ARM交叉编译工具链,例如

arm-none-eabi-gcc。 - 解压安装包并将其路径添加到系统的环境变量中,以便在任何目录下都能使用该交叉编译器。

以下是一个示例命令,展示如何在Linux环境下安装ARM交叉编译器:

- # 下载交叉编译器

- wget https://armkeil.blob.core.windows.net/developer/Files/downloads/gnu/10.2-2020.11/binrel/gcc-arm-none-eabi-10.2-2020.11-x86_64-linux.tar.bz2

- # 解压

- tar xjf gcc-arm-none-eabi-10.2-2020.11-x86_64-linux.tar.bz2

- # 添加路径到环境变量

- export PATH=$PATH:`pwd`/gcc-arm-none-eabi-10.2-2020.11/bin

安装完成后,可以通过执行arm-none-eabi-gcc --version命令验证交叉编译器是否安装成功。

3.1.2 链接器脚本和内存布局

链接器脚本是控制程序在内存中布局的重要工具,它定义了程序的各个段在内存中的位置。在嵌入式系统开发中,合理的内存布局设计对于提高程序的执行效率和稳定性至关重要。

在ARM Cortex-M7开发中,链接器脚本通常包含以下部分:

- 段定义:定义了不同类型的内存段,如

.text(代码段)、.data(已初始化的数据段)、.bss(未初始化的数据段)等。 - 内存区域:定义了程序可以使用的内存区域,比如内部RAM(IRAM)、闪存(Flash)等。

- 符号定义:定义了程序中的全局符号,用于地址解析。

创建一个简单的链接器脚本可以按照以下结构:

该链接器脚本定义了两个内存区域,一个用于Flash存储代码,另一个用于RAM存储数据。.text、.data、和.bss分别指向程序的代码段、已初始化数据段和未初始化数据段。

在实际开发中,链接器脚本需要根据目标硬件的具体参数进行调整,以保证程序可以正确地放置在指定的内存区域。对于ARM Cortex-M7这样的复杂系统,通常会使用专业的开发环境(如STM32CubeMX)生成链接器脚本,这可以大大简化配置过程。