U-Boot SPI性能优化:提升数据传输速率的秘诀

高薪程序员必备刷题软件-u-boot:来自git://git.denx.de/u-boot.git的U-boot引导加载程序的分支以支持我们的

摘要

U-Boot作为嵌入式系统中广泛使用的引导加载器,其在SPI(Serial Peripheral Interface)通信中的性能优化对系统启动时间和运行效率至关重要。本文首先概述了U-Boot与SPI接口的基本概念和性能分析的重要性。然后深入探讨了性能优化的理论基础和实际策略,包括代码层面和系统层面的优化方法。在代码层面,文章着重讨论了数据结构、算法以及缓冲管理和I/O操作的优化。系统层面则涉及驱动优化和U-Boot环境变量的调整。通过性能测试方法论和真实案例分析,本文展示了优化措施的实施效果,并对未来U-Boot在SPI接口性能优化的技术趋势和挑战进行了展望。

关键字

U-Boot;SPI接口;性能分析;性能优化;代码优化;系统配置

参考资源链接:瑞萨V3H2 U-Boot下SPI调试与问题解决

1. U-Boot与SPI接口概述

在嵌入式系统的启动和初始化过程中,U-Boot作为一个功能强大的引导加载器,扮演着至关重要的角色。通过与SPI(Serial Peripheral Interface,串行外设接口)的交互,U-Boot实现了对硬件设备的高效管理,比如引导操作系统、设置环境变量等任务。SPI作为常见的低速通信接口,因其简单、高速和低成本的特性,在嵌入式系统中得到了广泛的应用。在本章中,我们将介绍SPI的基本概念和其工作原理,同时分析U-Boot在SPI通信中的作用,为后续章节深入探讨U-Boot SPI性能分析和优化策略打下基础。

2. U-Boot SPI性能分析

2.1 SPI协议基础

2.1.1 SPI的工作原理

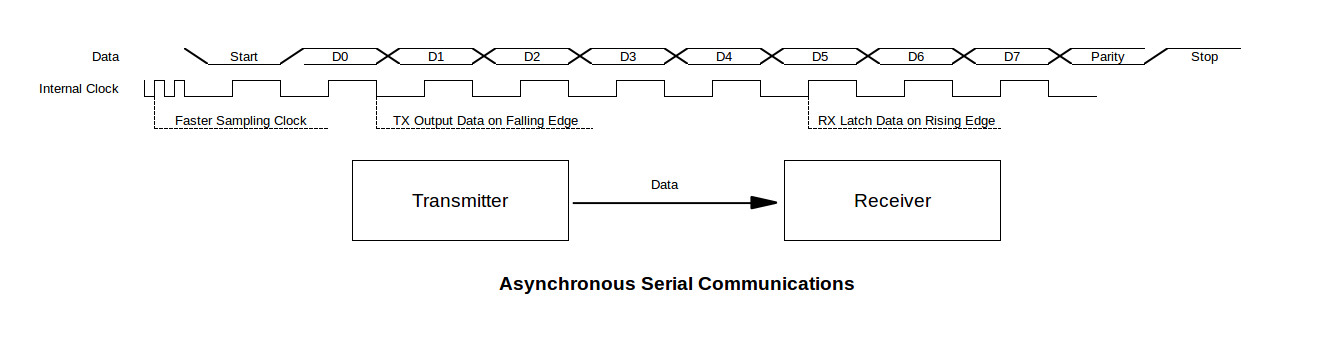

SPI(Serial Peripheral Interface)是一种常用的高速、全双工、同步串行通信接口。它广泛应用于微控制器和各种外围设备之间,如传感器、闪存、实时时钟等。SPI工作原理基于主从架构,包括一个主设备(Master)和一个或多个从设备(Slave)。

主设备负责生成时钟信号(SCLK)、主出从入(MOSI)信号和主入从出(MISO)信号,并且通常还负责从设备选择(SS)。在通信过程中,主设备通过SS线选择特定的从设备,并通过SCLK同步数据传输。数据在MOSI和MISO线上以位流的形式传输,通常主设备在MOSI线上发送数据到从设备,从设备则在MISO线上发送数据给主设备。数据位的传输是在时钟信号的上升沿或下降沿进行的,这取决于SPI的配置。

2.1.2 SPI通信模式及其特点

SPI通信模式根据时钟极性和相位的不同分为四种类型,即四种不同的时钟模式,如下所示:

- 模式0(CPOL=0, CPHA=0):时钟空闲时为低电平(CPOL=0),数据在时钟的第一个跳变沿采样(CPHA=0)。

- 模式1(CPOL=0, CPHA=1):时钟空闲时为低电平(CPOL=0),数据在时钟的第二个跳变沿采样(CPHA=1)。

- 模式2(CPOL=1, CPHA=0):时钟空闲时为高电平(CPOL=1),数据在时钟的第一个跳变沿采样(CPHA=0)。

- 模式3(CPOL=1, CPHA=1):时钟空闲时为高电平(CPOL=1),数据在时钟的第二个跳变沿采样(CPHA=1)。

不同设备可能支持不同的SPI模式,选择正确的模式对通信成功至关重要。模式0和模式1是最常见的,因为它们与大多数设备兼容。

2.2 U-Boot在SPI通信中的角色

2.2.1 U-Boot作为引导加载器的职责

U-Boot作为一款功能强大的引导加载器(Bootloader),通常在嵌入式设备的启动过程中担任重要角色。它的主要职责包括初始化硬件设备,建立内存空间映射,设置CPU和内存的参数,加载操作系统的映像到RAM中,并最终把控制权交给操作系统。

在SPI通信过程中,U-Boot通常用于初始化SPI接口,配置SPI控制器,并在启动阶段读取存储在SPI Flash中的数据,如引导代码、内核映像或文件系统。

2.2.2 U-Boot与SPI固件的交互

U-Boot与SPI固件的交互主要发生在系统启动阶段。首先,U-Boot初始化SPI总线和相关的硬件设备,然后通过SPI接口读取存储在SPI Flash中的初始引导代码。这个引导代码,也称作“二级引导器”(Secondary Program Loader, SPL),会被U-Boot加载到RAM中执行。SPL继续初始化更复杂的硬件设备,为最终加载操作系统做好准备。

2.3 性能瓶颈识别

2.3.1 常见性能问题及影响因素

在U-Boot与SPI通信中,性能瓶颈可能由多种因素引起。常见的性能问题及其影响因素包括:

- SPI速率配置不当:速率设置得太低会浪费带宽,设置得太高可能导致通信错误。

- 缓存未启用或配置不恰当:缓存可以提高读写速度,如果未启用或配置不当将影响性能。

- 总线拥挤:在有多个设备共享SPI总线的情况下,总线拥挤可能导致通信延迟。

- CPU与SPI控制器之间的数据传输效率:这涉及到内存操作和I/O操作的效率。

2.3.2 性能测试方法和工具

为了识别和分析性能瓶颈,可采取以下方法和工具:

- 使用逻辑分析仪捕捉SPI总线上的信号,进行时序分析。

- 利用示波器监测时钟信号和数据线上的信号,检查是否存在信号完整性问题。

- 利用专用软件工具,如Bus Pirate或Saleae Logic等,对SPI通信进行记录和分析。

- 在U-Boot环境中运行自定义的测试脚本,收集吞吐量和延迟等性能数据。

在进行性能测试时,需注意控制变量,如硬件环境和测试负载的一致性,以保证测试结果的准确性和可重复性。通过这些工具和技术手段,可以准确地诊断出系统中的性能瓶颈,并对症下药地进行优化。

3. 理论基础与优化策略

3.1 性能优化理论

3.1.1 理论模型的建立

在进行U-Boot SPI性能优化之前,建立一个正确的理论模型至关重要。理论模型可以帮助我们理解系统中各个组件是如何协同工作的,并且指导我们如何对它们进行调整和优化。在U-Boot SPI通信环境中,理论模型通常包括以下几个方面:

- 数据流模型:描述数据如何在SPI总线上传输,包括数据的发送方、接收方、传输媒介以及数据在传输过程中的格式变化。

- 时序模型:关注数据传输的时序关系,包括时钟频率、时钟极性和相位等因素。

- 性能瓶颈模型:分析影响系统性能的关键因素,如CPU处理速度、内存带宽、I/O延迟等。

理论模型的建立基于对U-Boot源码的深入理解和对SPI协议的全面把握。模型需要足够详细以指导实际的优化工作,同时又要保持一定的抽象性,以便适用于不同的硬件平台和使用场景。

3.1.2 性能优化的基本原则

性能优化的基本原则是提高系统资源的利用效率,减少不必要的开销,以及消除或减少性能瓶颈。具体来说,以下原则需要被遵循:

- 最小化I/O操作:I/O操作通常比内存操作要慢得多,因此优化应尽量减少不必要的I/O调用。

- 算法效率:选择时间复杂度和空间复杂度更优的算法来处理数据。

- 缓存友好:合理使用CPU缓存,避免缓存失效,利用缓存预取技术提升性能。

- 并行处理:针对可以并行执行的任务,通过多线程或异步I/O进行处理,从而充分利用CPU资源。

- 延迟隐藏:合理安排任务执行的顺序,以隐藏系统的延迟,例如在等待I/O操作完成时执行