S32K SPI时序控制与外围设备匹配:精确调整秘籍

发布时间: 2024-12-22 22:42:03 阅读量: 5 订阅数: 10

# 摘要

本文主要探讨了基于S32K平台的SPI时序控制技术,包括其基础理论、硬件连接、时序分析、问题诊断、高级匹配技巧以及性能优化等多个方面。通过对S32K SPI引脚功能与配置、外围设备的信号特点、初始化与配置、时序参数调整、故障诊断、高级匹配案例分析、软件层面的辅助匹配、时序优化原理、性能提升技术应用、性能测试与评估的深入研究,我们为设计和优化基于S32K的SPI通信提供了系统的理论指导和实践操作。同时,本文还对未来S32K SPI技术的发展趋势进行了展望,为S32K平台的持续创新和行业应用的新场景提供了新的思考。

# 关键字

S32K;SPI时序控制;硬件连接;时序分析;性能优化;技术发展

参考资源链接:[S32K系列SPI驱动开发实战:配置、测试与问题解析](https://wenku.csdn.net/doc/6412b54fbe7fbd1778d42b04?spm=1055.2635.3001.10343)

# 1. S32K SPI时序控制基础

在当今的嵌入式系统设计中,掌握SPI通信时序控制是实现高效数据传输的关键。本章节将为读者提供S32K SPI时序控制的基础知识,奠定深入理解和应用的基石。

首先,我们将从SPI通信的基本概念入手,介绍SPI(Serial Peripheral Interface)总线技术作为一种广泛使用的串行通信协议,在S32K系列微控制器中的应用。我们将详细讲解时钟极性和相位的配置,它们是如何影响数据传输的同步和效率的。

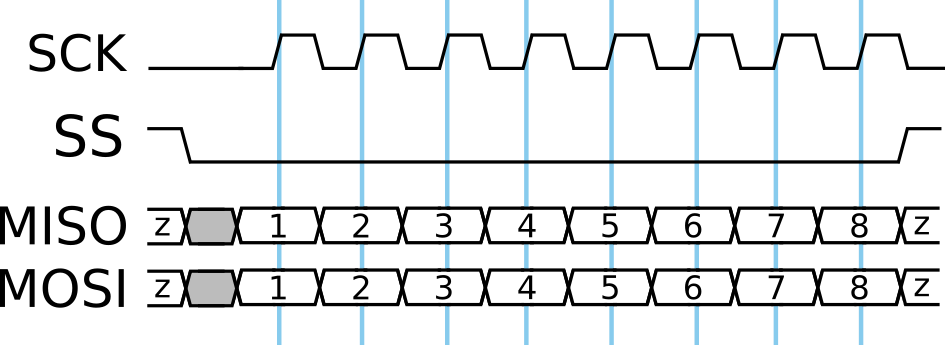

接下来,本章节还将深入探讨SPI时序图的构成要素,包括同步时钟(SCK)、主设备和从设备的选通信号(SS)、主从设备数据线(MOSI和MISO)等。通过对这些基本元素的理解,读者将能够更好地识别和控制数据交换过程中的关键时序点。

为了加深理解,我们将通过实例来演示如何在S32K平台上设置SPI模块的时钟速率、数据位宽和帧格式,这些是实现准确数据传输的重要步骤。通过本章节的学习,读者将获得S32K SPI时序控制的初步认识,为后续章节的深入探讨打下坚实基础。

# 2. S32K与外围设备的硬件连接

### 2.1 S32K SPI引脚功能与配置

#### 2.1.1 引脚定义及信号流向

S32K系列微控制器的SPI(Serial Peripheral Interface)是一种同步串行通信协议,用于微控制器与外围设备之间的高速数据交换。在了解如何配置这些引脚之前,我们需要先掌握引脚定义和信号流向。

S32K的SPI接口通常包含以下引脚:

- **SCK(Serial Clock)**: 时钟信号,由主设备提供,用于同步数据发送和接收。

- **MISO(Master In Slave Out)**: 主设备输入/从设备输出。在数据发送期间,从设备通过此引脚将数据发送到主设备。

- **MOSI(Master Out Slave In)**: 主设备输出/从设备输入。主设备通过此引脚向从设备发送数据。

- **SS(Slave Select)**: 片选信号,用于选择当前通信的从设备。

信号流向通常遵循以下规则:

- 当进行数据发送时,数据从主设备的MOSI引脚流向从设备的MISO引脚。

- 当进行数据接收时,数据从从设备的MISO引脚流向主设备的MOSI引脚。

- SCK负责提供时钟信号,以协调主从设备间的数据同步。

- SS信号用于多个从设备环境中的选择控制,确保主设备只与一个从设备通信。

#### 2.1.2 配置引脚的电气特性

在硬件连接阶段,除了了解引脚的逻辑功能,还需要对引脚的电气特性进行配置,以便与外围设备兼容。电气特性配置主要包括:

- **上下拉电阻**: 根据外围设备的要求配置引脚的上下拉电阻值,保证在无驱动信号时引脚电平是确定的。

- **驱动能力**: 调整引脚的驱动能力,以满足传输距离和负载的需要。

- **速率限制**: 在高速传输时,可能需要对信号的上升沿和下降沿进行限制,以减少电磁干扰。

引脚的电气特性可以通过特定的寄存器进行配置,通常是在S32K的初始化代码中完成:

```c

// 示例代码:配置SPI引脚的电气特性

void SPI_Pin_Config(void)

{

// 启用SPI模块的时钟

PCC->PCCn[PCC_SPI0_INDEX] |= PCC_PCCn_CGC_MASK;

// 配置SS引脚为GPIO输出,用于片选控制

PORTA->PCR[SS_PIN] &= ~PORT_PCR_PE_MASK;

PORTA->PCR[SS_PIN] |= PORT_PCR_ODE_MASK | PORT_PCR_DSE_MASK;

GPIOA->PDDR |= (1U << SS_PIN);

// 其他引脚配置...

}

```

在上述代码中,通过修改端口控制寄存器(PCR)和端口数据方向寄存器(PDDR),从而配置了SS引脚为输出模式,并设定了开漏输出和高驱动能力。

### 2.2 SPI外围设备的信号特点

#### 2.2.1 常见外围设备的SPI协议分析

不同外围设备对SPI通信的需求各不相同,但通常遵循以下基本协议特点:

- **设备地址**: 很多外围设备使用地址来区分不同的寄存器或者功能,设备需要识别主机发送的地址来确定是否响应。

- **读/写控制**: SPI协议通常需要一个或多个引脚来表示读写操作。

- **数据格式**: 外围设备可能对数据的格式有特定要求,例如8位或16位数据宽度。

- **时序要求**: 每个外围设备都有自己的时序要求,例如SCK的频率范围、时钟极性和相位等。

例如,一个典型的EEPROM设备可能具有以下SPI协议特点:

- **单字节地址**: EEPROM通常通过单字节地址来访问内部的存储单元。

- **写保护**: 一些EEPROM还支持写保护功能,通过特定的命令来控制。

#### 2.2.2 时序要求与匹配策略

时序要求是确保SPI通信正常工作的关键。匹配策略包括:

- **频率匹配**: 主从设备的SCK频率需要在可接受的范围内匹配。

- **相位和极性**: SPI通信的时钟极性和相位配置必须一致,否则可能导致数据接收错误。

一个匹配策略的代码示例:

```c

// 示例代码:配置SPI时序参数

void SPI_Timing_Config(void)

{

SPI0->CTAR[0] = SPI_CTAR_FMSZ(7) | SPI_CTAR_PBR(1) | SPI_CTAR_BR(1);

SPI0->CTAR[0] |= SPI_CTAR_CPHA_MASK | SPI_CTAR_CPOL_MASK;

// 设置SPI模块为主机模式,时钟极性和相位配置

// FMSZ: 帧大小,PBR: 预分频器比值,BR: 波特率系数

// CPHA: 相位控制,CPOL: 极性控制

}

```

在这个例子中,我们配置了SPI的帧大小为8位,预分频器比值为2,波特率为系统时钟的一半,并且设置了正确的时钟极性和相位。

### 2.3 S32K SPI初始化与配置

#### 2.3.1 SPI模块的初始化过程

初始化SPI模块包括时钟启用、引脚配置、时序参数设置等。以下是初始化的一般步骤:

1. 启用SPI模块的时钟。

2. 将SPI引脚配置为SPI功能。

3. 设置SPI的传输参数,如时钟速率、时钟极性、相位等。

4. 配置中断(如果需要)。

5. 将SPI模块置于主模式。

初始化代码示例:

```c

// 示例代码:初始化SPI模块

void SPI_Init(void)

{

// 启用SPI模块的时钟

PCC->PCCn[PCC_SPI0_INDEX] |= PCC_PCCn_CGC_MASK;

// 配置SPI引脚为SPI功能

// 配置SPI时序参数...

// 将SPI模块置于主模式

SPI0->MCR &= ~SPI_MCR_MDIS_MASK;

SPI0->MCR |= SPI_MCR_HALT_MASK | SPI_MCR克拉夫特_mask;

SPI0->MCR &= ~SPI_MCR_HALT_MASK;

}

```

#### 2.3.2 波特率、相位和极性的配置

波特率、相位和极性是SPI通信中的三个关键时序参数,需要根据外围设备的要求进行精确配置。以下是如何配置这些参数的详细说明:

- **波特率**: 通过修改SPI模块的波特率预分频器来设置。这个预分频器决定时钟频率,进而影响数据传输速率。

- **相位和极性**: 相位(CPHA)和极性(CPOL)的设置决定了时钟信号的逻辑电平。这必须与外围设备的时序图相匹配。

```c

// 示例代码:配置SPI的波特率、相位和极性

void SPI_Baud_Config(void)

{

// 设置波特率为系统时钟的1/4

SPI0->BR = SPI_BR_BR(3);

// 配置时钟极性和相位,假设使用的是模式3

SPI0->CTAR[0] |= SPI_CTAR_CPHA_MASK | SPI_CTAR_CPOL_MASK;

}

```

此代码段设置波特率为系统时钟的1/4,并配置时钟极性和相位为模式3,以便与符合该模式的外围设备进行通信。

# 3. S32K SPI时序分析与问题诊断

## 3.1 时序图的解读与分析

### 3.1.1 时序图的基本元素

在深入探讨S32K SPI时序分析之前,必须理解时序图的基本元素。时序图是用于展示SPI通信中各信号线变化的图形表示,它记录了时钟线(SCK)、主设备出从设备入的MOSI线、从设备出主设备入的MISO线以及片选(CS)线的状态变化。每一个信号线的上升沿和下降沿都具有特定的意义,它们定义了数据的采样时机和数据有效窗口。

时序图通常包括以下元素:

- **时钟线(SCK)**:控制数据传输的节奏。

- **主设备到从设备(MOSI)**:主设备发送到从设备的数据线。

- **从设备到主设备(MISO)**:从设备发送到主设备的数据线。

0

0