Zynq平台LWIP初始化的常见问题及其解决

zynq裸机lwip不插网线初始化lwip库添加配置项方法lwipopts

摘要

本文全面探讨了在Zynq平台上基于LWIP协议栈的初始化过程,包括必要的理论知识和实践操作。文章首先概述了LWIP协议栈的架构和核心组件,接着介绍了Zynq硬件平台的特性及其与LWIP的交互,包括PS和PL部分的交互。随后,文章详细分析了LWIP初始化代码的结构,包括关键数据结构和API的应用,以及实践中常见的问题及其解决方法。最后,本文针对高级配置与优化提出了策略,包括实现高级网络功能、故障诊断与调试技巧,并对未来系统的扩展性和模块化设计进行了考量。本文旨在为Zynq平台上的LWIP网络初始化提供详实的指导和优化建议。

关键字

LWIP;Zynq平台;协议栈架构;网络接口驱动;内存管理;故障诊断

参考资源链接:Zynq裸机LWIP无网线配置与热插拔初始化教程

1. Zynq平台LWIP初始化概述

在嵌入式系统开发中,网络通信已成为不可或缺的功能之一。Zynq平台,作为Xilinx推出的一种系统级芯片(SoC),将ARM处理器核心与FPGA逻辑紧密集成,为网络应用提供了强大的硬件支持。实现网络功能的第一步是初始化轻量级互联网协议栈(LWIP),它是专为嵌入式系统设计的一个开源TCP/IP协议栈。本章节将概述Zynq平台中LWIP初始化的基本概念、重要性以及如何在该平台进行初始化配置的基础。

在Zynq平台中成功初始化LWIP协议栈涉及以下几个关键方面:

- 硬件平台的网络接口配置,确保网络硬件资源就绪。

- LWIP核心组件和层次结构的搭建,包括内存管理、定时器和核心协议的实现。

- 网络接口驱动的编写,以便LWIP能够与Zynq的网络硬件有效通信。

2.1 LWIP协议栈架构理解

2.1.1 LWIP核心组件解析

LWIP的核心组件包括数据包处理接口、内存管理和定时器服务。每个组件都有特定的功能,共同确保数据包的正确传输和网络通信的顺畅进行。

2.1.2 协议栈层次结构和交互

LWIP的层次结构类似于标准TCP/IP模型,包括链路层、网络层、传输层和应用层。不同层次间通过API进行交互,确保了协议栈内部的高效运作。

2.2 Zynq硬件平台介绍

2.2.1 Zynq架构特点

Zynq架构融合了ARM处理器核心和FPGA逻辑,这种异质多处理特性为网络应用提供了高灵活性和性能优势。

2.2.2 Zynq中的PS和PL交互

在Zynq中,PS(Processing System)与PL(Programmable Logic)之间的高效交互是实现复杂网络应用的关键。PS负责运行操作系统和LWIP协议栈,而PL则可以用来实现定制化的硬件加速器或直接的硬件接口。

2.3 网络接口驱动的基础知识

2.3.1 网络接口驱动的作用与分类

网络接口驱动作为硬件与软件的桥梁,是实现LWIP正常工作的重要组成部分。驱动程序分为轮询和中断驱动两大类,各有优势和适用场景。

2.3.2 驱动与LWIP的接口定义

LWIP为驱动程序提供了清晰的接口定义,包括数据包的发送、接收、缓冲区管理等。这些接口的正确实现对保证网络通信的稳定性和效率至关重要。

在下一章中,我们将详细探讨LWIP初始化所需的基本理论,帮助读者更深入地理解LWIP协议栈的实现细节及其在Zynq平台的应用背景。

2. LWIP初始化所需基本理论

2.1 LWIP协议栈架构理解

2.1.1 LWIP核心组件解析

LWIP(Lightweight IP)是一个开源的TCP/IP协议栈,专为嵌入式系统设计,以实现一个功能丰富但资源消耗低的网络解决方案。理解其核心组件是实施初始化之前必须的步骤。

LWIP的核心组件主要包括:

- 内存管理: LWIP提供了多种内存管理策略以适应不同的硬件和应用需求。它允许应用在不使用操作系统的情况下静态分配内存,或者在有操作系统的环境中使用动态内存分配。

- 网络接口层: 这一层负责与底层硬件驱动的交互,发送和接收网络数据包。

- 核心层(Core): 包含了IP、ICMP、UDP和TCP等核心协议的实现。

- API层: 包含了为应用层提供的接口,允许应用层调用网络功能,如发送和接收数据。

2.1.2 协议栈层次结构和交互

LWIP的层次结构是分层的,每个层次都有特定的职责,并通过标准的协议栈接口与其他层次进行交互。

- 应用层:通过socket API与LWIP通信。

- 传输层:TCP和UDP提供端到端的连接。

- 网络层:IP协议负责数据包的路由与转发。

- 链路层:LWIP与网络接口层交互,通过驱动与物理网络硬件通信。

LWIP的各层组件之间通过回调函数和数据包队列进行通信,例如,当链路层接收到数据时,它通过注册的回调函数将数据包传递给网络层。

2.2 Zynq硬件平台介绍

2.2.1 Zynq架构特点

Zynq是一种可编程SoC(System on Chip),它将ARM处理器核心与可编程逻辑资源(FPGA)相结合,提供了处理与定制硬件逻辑的灵活性。

- 处理器子系统(PS):包含ARM Cortex-A9双核处理器,以及许多专用的硬件加速器。

- 可编程逻辑(PL):可以实现自定义硬件逻辑和接口。

这种架构特别适合那些需要实时处理和高带宽网络通信的嵌入式应用。

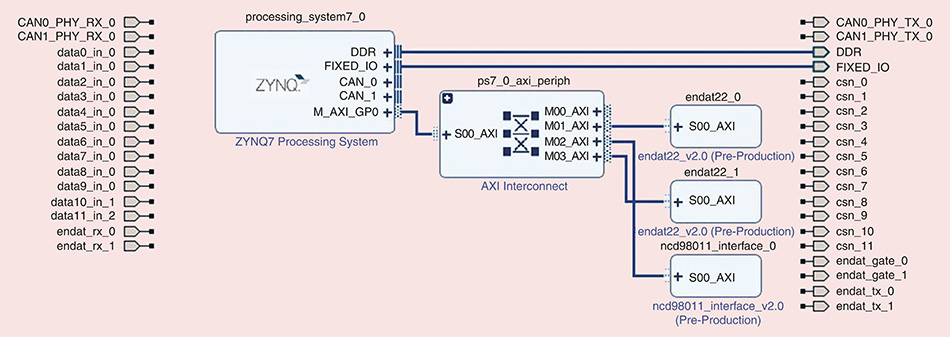

2.2.2 Zynq中的PS和PL交互

在Zynq中,PS和PL之间的交互是至关重要的。它们通过多个接口进行通信,包括AXI(Advanced eXtensible Interface),这是连接处理器和FPGA逻辑的桥梁。

- 处理器控制:PL中的FPGA逻辑可以执行特定的功能,然后将结果返回给PS进行进一步处理。

- 直接内存访问(DMA):对于高吞吐量的数据传输,DMA允许PL直接访问PS的内存空间,绕过处理器核心,提高效率。

- 中断系统:PL可以向PS发送中断信号,以通知处理器核心有特定事件发生。

2.3 网络接口驱动的基础知识

2.3.1 网络接口驱动的作用与分类

网络接口驱动是操作系统和网络接口卡(NIC)之间的桥梁。它的主要作用包括:

- 数据包的接收与发送:处理数据包在操作系统和网络硬件之间的移动。

- 中断处理:管理与数据包处理相关的中断。

- 设备控制:提供接口以控制和配置网络设备。

网络接口驱动通常分为两大类:

- 轮询模式:驱动不断轮询设备以检查是否有数据包需要处理。

- 中断驱动:当设备准备发送或接收数据包时,通过中断通知驱动。

2.3.2 驱动与LWIP的接口定义

驱动与LWIP的接口定义是确保两者能够顺畅通信的关键。接口定义通常包括:

- 发送接口:定义了LWIP调用驱动发送数据包的函数。

- 接收接口:定义了驱动如何通知LWIP