LEF_DEF文件编写技巧:最大化EDA工具性能的方法

发布时间: 2024-12-16 05:14:08 阅读量: 2 订阅数: 6

lef_layer_tf_number_mapper.pl

参考资源链接:[LEF/DEF 5.8语言参考手册:集成电路设计关键](https://wenku.csdn.net/doc/59k5wq5df5?spm=1055.2635.3001.10343)

# 1. LEF_DEF文件的基础知识与重要性

在现代集成电路设计流程中,LEF(Library Exchange Format)和DEF(Design Exchange Format)文件扮演着至关重要的角色。LEF文件是一种用于描述库单元和金属层信息的格式,而DEF文件则用于表示设计中的实际布局。这些文件为EDA(Electronic Design Automation)工具提供了设计的物理描述,是实现精确布局布线、时序分析、信号完整性分析以及最终的制造准备的关键。

LEF_DEF文件的重要性不仅在于它们是设计过程中的中间产物,更在于它们所承载的数据是确保集成电路设计符合预期功能和性能的核心。没有精确的LEF_DEF文件,设计验证和制造可能会遇到诸多障碍,例如布线错误、时序问题、不符合工艺要求的布局等,从而影响产品的质量和上市时间。

本章将深入探讨LEF_DEF文件的基本结构和内容,为读者提供一个扎实的起点,以理解这些文件在整个集成电路设计流程中的关键作用。我们将从LEF_DEF文件的基本概念开始,逐步深入到它们在实际应用中的重要性,为下一章深入分析EDA工具中LEF_DEF文件的作用打下坚实的基础。

# 2. 理解EDA工具中LEF_DEF文件的作用

## 2.1 LEF_DEF文件在集成电路设计中的角色

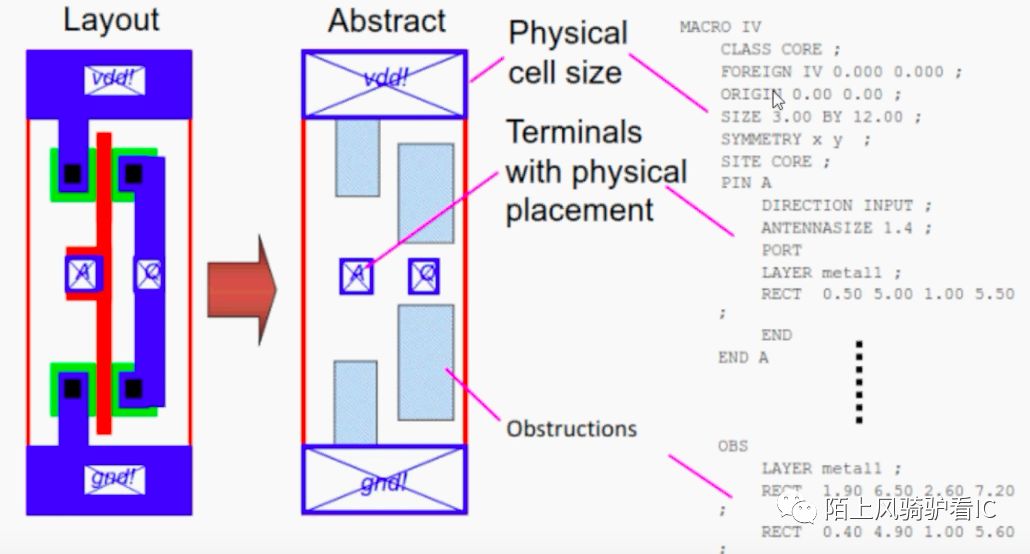

### 2.1.1 LEF_DEF文件的定义和结构

在现代集成电路设计流程中,LEF(Library Exchange Format)和DEF(Design Exchange Format)文件扮演着至关重要的角色。LEF文件提供了一种方式来描述设计中使用的库单元,包括标准单元和IP核,其几何形状、延时、功耗和连接信息。而DEF文件则是用来表示设计的物理布局,它包含了各个单元的放置位置、布线以及工艺层的定义。

LEF文件的结构主要包含以下几个部分:

1. 版本声明(VERSION):指定LEF文件使用的语法版本。

2. 库信息(Libraries):定义设计中使用的所有库的名称和属性。

3. 单元定义(Unit):列出库中定义的所有单元以及它们的尺寸、端口和图层信息。

4. 层描述(Layers):定义与设计相关的图层,例如金属层和通孔。

5. 技术文件(Techfile):包含与制造工艺相关的参数。

相对而言,DEF文件结构较为简单,主要分为:

1. 版本声明(VERSION):指定DEF文件使用的语法版本。

2. 设计声明(DESIGN):定义设计的名称和工艺节点。

3. 单元声明(CELL):定义设计中每个单元的名称、位置和方向。

4. 网络声明(NET):包含互连各个单元的导线信息,如连接点和路径。

5. 层定义(LAYER):指定设计中使用的层以及与之相关的参数。

### 2.1.2 LEF_DEF文件对布局和布线的影响

布局和布线(Place and Route,P&R)是集成电路设计的关键步骤,而LEF和DEF文件直接影响到这一过程的效率和质量。正确管理这些文件,能够确保设计满足时序、功耗和信号完整性等多方面的要求。

在布局阶段,EDA工具根据LEF文件中提供的单元信息,决定每个单元的最佳放置位置。单元的尺寸和形状,以及它们在图层上的约束,都直接影响到布局的密度和布线的复杂程度。而DEF文件则提供了单元放置的具体位置和方向,指导布线工具进行下一步操作。

布线阶段,DEF文件定义的网络(NET)信息告诉布线工具如何连接各个单元,以满足电气性能要求。同时,LEF文件中的图层信息用于确保布线遵循制造工艺的限制。例如,不同金属层的宽度和间距要求会影响布线的质量。

总之,LEF和DEF文件是EDA工具执行布局和布线操作的基础,它们不仅确保了设计的可制造性,而且直接影响到芯片性能和成本。因此,精确而高效地创建和管理这些文件是至关重要的。

## 2.2 EDA工具的基本工作原理

### 2.2.1 EDA工具的分类和功能

EDA工具是一类用于设计、分析和制造电子系统的计算机软件。根据设计流程的不同阶段,EDA工具可以分为几大类:

1. **前端设计工具**:这一类工具用于帮助工程师完成电路图的设计、电路模拟和逻辑验证。常见的前端设计工具有VHDL或Verilog HDL编译器、模拟器和逻辑综合工具。

2. **布局与布线工具**:负责把前端设计的逻辑图转换成物理版图。这一阶段的主要工具包括单元布局工具、布线工具以及整体的综合布局布线(Synthesis, Place & Route, P&R)工具。

3. **后端设计工具**:包括版图验证、时序分析、功耗分析、信号完整性分析和热分析等。这些工具确保版图设计满足所有物理和电气的约束条件。

4. **物理验证工具**:如DRC(Design Rule Check)、ERC(Electrical Rule Check)、LVS(Layout Versus Schematic)等,用于在设计完成后进行物理规则和电路规则的检查。

5. **制造准备工具**:用于准备最终设计数据以用于制造,包括生成用于光刻的掩模数据和生成GDSII文件等。

### 2.2.2 EDA工具中的LEF_DEF处理流程

在EDA工具中,LEF和DEF文件的处理流程通常涉及以下关键步骤:

1. **读入设计信息**:通过导入DEF文件开始,工具会加载设计版图的所有信息,包括放置和布线的数据。

2. **分析和优化**:EDA工具会分析版图的时序、信号完整性以及功耗等,并基于分析结果进行优化。对于LEF文件,工具会读取制造工艺的信息和库单元的定义,用于指导优化过程。

3. **物理验证**:通过DRC、ERC和LVS等物理验证工具确保设计满足工艺规则和电路规则,验证结果反馈到布局布线阶段,进行必要的调整。

4. **数据输出**:一旦设计通过了所有验证和优化步骤,EDA工具会输出最终的GDSII或OASIS文件,这些文件可以被直接用于制造。

在整个处理流程中,LEF和DEF文件作为连接前后端设计的关键纽带,它们的质量和精确度直接影响到最终芯片的性能。EDA工具处理这些文件的效率和准确性,是现代集成电路设计不可或缺的一部分。

## 2.3 LEF_DEF文件与工艺节点的关系

### 2.3.1 工艺节点对LEF_DEF文件的要求

随着集成电路制造工艺的进步,设计工程师面对的设计规则和工艺要求变得越来越复杂。每个工艺节点(如28nm、14nm、7nm等)都有其特定的设计规则,这些规则必须严格遵守以确保芯片的正常工作。

对于LEF文件,设计师需要为每个工艺节点提供精确的图层信息,包括不同金属层的宽度和间距规则、通孔大小及间隔、以及制造工艺中的其它限制。这些信息对于EDA工具来说至关重要,它们依赖这些信息来进行精确的布局布线。

DEF文件同样需要与特定工艺节点的要求相匹配,它必须准确反映物理版图上各个单元的位置和方向,以及它们之间的连接关系。此外,DEF文件还需要包含与工艺节点相关的制造参数,例如金属层的电阻率和介电常数等。

### 2.3.2 不同工艺节点下LEF_DEF文件的编写差异

随着制造技术的进步,新的工艺节点往往意味着更小的特征尺寸和更复杂的布线规则。因此,在编写LEF和DEF文件时,需要考虑以下差异:

1. **单元尺寸变化**:在更先进的工艺节点下,标准单元的尺寸更小,这导致版图更加密集,对布线的精确度要求更高。

2. **金属层与通孔**:随着工艺节点的缩小,可用的金属层可能增加,而相应的通孔也会更小且更密集,这需要在LEF文件中更新图层和通孔的定义。

3. **设计规则变化**:为了实现更好的性能,不同工艺节点下设计规则可能有所不同,如最小间距、最小宽度等。这些规则必须在LEF文件中进行相应的更新。

4. **功耗和信号完整性**:先进的工艺节点提供了更低的工作电压和更高的晶体管密度,但同时对信号完整性和功耗管理提出了更高要求。因此,DEF文件中必须准确反映这些要求。

不同工艺节点下LEF和DEF文件的编写差异,要求设计师保持对最新制造工艺的了解,不断更新和维护这些文件以满足新的设计挑战。通过不断优化这些文件,设计师可以确保他们的设计不仅满足技术要求,而且能够在制造过程中顺利生产。

在这一过程中,设计师和工程师需要掌握一系列复杂的技术参数和规范,并利用先进的EDA工具来准确编写和管理LEF_DEF文件。这些文件在集成电路设计中发挥着桥梁作用,连接着从设计到制造的整个流程。通过深入理解这些文件的作用和编写方法,可以大大提升集成电路设计的效率和芯片的质量。

# 3. LEF_DEF文件编写技巧

## 3.1 LEF文件的编写和优化

### 3.1.1 LEF文件的关键技术参数

在LEF(Library Exchange Format)文件中,包含了芯片制造工艺的基础信息,例如标准单元、宏单元的物理描述以及与布局相关的数据。LEF文件关键的技术参数可以分为两类

0

0