纳米挑战攻略:CMOS VLSI设计中的先进制造工艺探索

发布时间: 2024-12-25 10:51:29 阅读量: 7 订阅数: 15

CMOS VLSI Design - A Circuits and Systems Perspective

# 摘要

本文探讨了CMOS VLSI设计与纳米技术融合带来的挑战与机遇。在第二章中,从理论角度分析了纳米尺度CMOS工艺的发展,包括物理极限、量子效应挑战、先进制造工艺原理及设计优化。第三章则聚焦于纳米尺度CMOS制造工艺的实践挑战,涉及光刻技术、薄膜沉积与刻蚀技术以及热管理和可靠性问题。第四章讨论了性能优化和创新应用,重点是功耗管理技术、3D集成电路与封装技术以及新型器件架构。最后,在第五章展望了未来,包括新材料与器件结构研究进展、制造工艺的极限以及跨学科整合的长远影响。整体上,本文为CMOS VLSI设计与纳米技术的未来发展提供了深入的技术分析和趋势预测。

# 关键字

CMOS VLSI设计;纳米技术;物理极限;量子效应;制造工艺;性能优化

参考资源链接:[现代CMOS VLSI设计:电路与系统视角](https://wenku.csdn.net/doc/6412b4fdbe7fbd1778d418b2?spm=1055.2635.3001.10343)

# 1. CMOS VLSI设计与纳米技术的融合

随着集成电路的发展,CMOS VLSI设计与纳米技术的融合已成为半导体行业的一个重要趋势。本章将介绍这一融合的背景、意义及相关的基础概念。

## 1.1 CMOS技术的重要性

互补金属氧化物半导体(CMOS)技术是目前最主流的半导体技术之一,被广泛应用于制造各种集成电路。随着技术的进步,芯片上的晶体管数量不断增加,这得益于CMOS技术的低功耗和高性能特性。

## 1.2 纳米技术在CMOS中的应用

纳米技术指的是在纳米尺度(1-100纳米)上的操作和制造技术。在CMOS VLSI设计中,纳米技术的应用允许设计师进一步缩小晶体管尺寸,提高了芯片的集成度和性能。

## 1.3 融合的挑战与机遇

随着芯片尺寸逼近物理极限,设计者面临量子效应、功耗控制、材料选择等一系列挑战。同时,这种技术融合也开启了新的机遇,如提高芯片性能,降低功耗,实现更多创新性的应用。

```mermaid

graph LR

A[CMOS VLSI设计] -->|技术融合| B[纳米技术]

B --> C[提高集成度与性能]

B --> D[降低功耗]

C --> E[创新应用]

D --> E[创新应用]

```

通过上图我们可以直观看到CMOS VLSI设计与纳米技术融合的直接效益,同时也反映了这一技术融合的重要性。后续章节我们将深入探讨具体的理论基础、实践挑战和性能优化等方面的内容。

# 2. 纳米尺度CMOS工艺的理论基础

## 2.1 物理极限与CMOS尺寸缩小

### 2.1.1 晶体管尺寸缩小的历史回顾

晶体管尺寸的缩小是摩尔定律的核心,也是推动CMOS VLSI设计进步的关键因素之一。自1960年代晶体管首次被引入集成电路以来,集成电路的集成度呈指数级增长,随之而来的,晶体管的尺寸也在持续缩小。从最初的微米级别到今天的纳米甚至亚纳米级别,晶体管的尺寸缩小经历了从物理上简单地缩小晶体管的物理尺寸,到引入更复杂的制造技术以保持器件性能的转变。

尽管早期晶体管尺寸的缩小相对容易,因为摩尔定律预测的晶体管数量翻倍的时间大约是18个月,但随着尺寸接近物理极限,挑战日益增大。在微米尺度上,尺寸缩小意味着更快的开关速度、更低的功耗和更高的集成度。然而,当达到纳米尺度时,量子效应和电子迁移率的下降开始影响器件性能。

### 2.1.2 纳米尺度下的量子效应与挑战

进入纳米尺度后,CMOS晶体管的尺寸缩小遇到了前所未有的挑战。量子效应,如量子隧穿和量子限域效应,开始显著影响器件的行为。量子隧穿允许电子在理论上不可逾越的势垒中穿越,从而导致晶体管的截止电流增加。这导致了静态功耗的提升,并影响了晶体管的开关效率。

除了量子效应,随着晶体管尺寸的缩小,电子迁移率也出现下降。电子迁移率的下降意味着在给定的电场下,电子的迁移速度变慢,这直接导致晶体管的开关速度减慢。为了解决这些问题,器件设计师和制造工程师不得不寻找新的晶体管结构和新材料。

## 2.2 先进制造工艺的基本原理

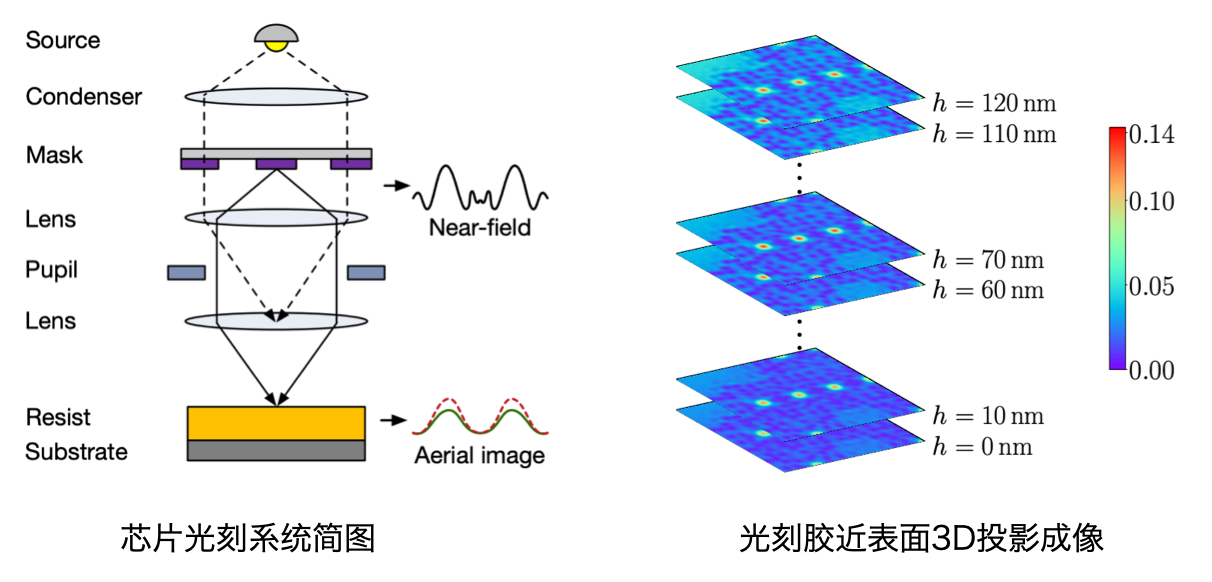

### 2.2.1 光刻技术的进步

光刻是半导体制造中至关重要的一步,它负责在硅片上创建出微小的电路图案。随着晶体管尺寸缩小到纳米级别,光刻技术必须不断进步以维持高精度和高分辨率。传统光源波长的局限性推动了向极紫外光(EUV)的转变。

极紫外光(EUV)光刻技术使用波长更短的13.5nm的光,相较于传统光刻技术使用的193nm波长的光,EUV技术显著提高了特征尺寸的分辨率。EUV技术的应用还面临着光刻机的成本和技术挑战,比如高功率光源的开发、光刻胶的敏感度以及反射镜的制造等。

### 2.2.2 离子注入与扩散的控制

随着特征尺寸的缩小,离子注入与扩散的精确控制变得越来越困难。离子注入是现代CMOS制造中引入掺杂元素到硅衬底以形成源极和漏极的标准过程。在纳米尺度,需要更精细地控制掺杂分布,以减少晶体管之间的差异并优化性能。

为了实现这一点,制造工艺中采用了诸如低能量注入和退火工艺等技术。低能量注入减少了掺杂元素在硅中的扩散,退火工艺则在注入后重新排列硅晶体的晶格,以修复注入过程可能导致的损伤。

### 2.2.3 金属互连和低-k介电材料的应用

随着特征尺寸缩小,传统铝金属互连的电阻和寄生电容成为影响芯片性能的主要因素。引入铜互连和低介电常数(k)材料是为了解决这一问题。铜取代了铝作为互连材料,因为它具有更低的电阻率和更好的抗电迁移性能。

同时,低-k介电材料用于减少互连层之间的寄生电容。这些材料具有比传统氧化硅更低的介电常数,从而减少了信号传输过程中的电容耦合效应,提高了芯片的性能。

## 2.3 设计优化与工艺协同

### 2.3.1 设计规则的演化

设计规则是芯片设计和制造的基础,它们定义了最小特征尺寸、最小间距以及各种制造容差。随着技术的进步,设计规则也在不断进化,以适应纳米尺度下晶体管的物理特性和制造工艺的限制。

设计师必须在晶体管尺寸、功耗、性能和可靠性之间找到新的平衡点。新型设计规则考虑了多阈值电压晶体管、功耗门控技术以及器件隔离的要求。设计规则的变化要求设计师和制造工程师之间进行密切合作,以确保从设计到制造的过渡平滑,并且最终产品满足性能和可靠性要求。

### 2.3.2

0

0