【信号完整性分析】:上下拉电阻对USB传输速率的影响揭秘

发布时间: 2024-12-13 23:52:46 阅读量: 11 订阅数: 12

信号完整性的概念:差分对

参考资源链接:[USB DM-DP ID上下拉电阻详解:高速低速设备与OTG功能辨析](https://wenku.csdn.net/doc/6412b485be7fbd1778d3fde5?spm=1055.2635.3001.10343)

# 1. 信号完整性基础与USB传输概述

## 1.1 信号完整性的重要性

在高速数字电路设计中,信号完整性(Signal Integrity, SI)是一个关键的考量因素。良好的信号完整性意味着电路在规定的工作条件下,信号能正确地传输。随着电路工作频率的不断提高,信号完整性问题也愈发突出,这些问题包括信号反射、串扰、时序偏移和电磁干扰等,它们都可能导致设备性能下降或完全失效。

## 1.2 USB传输技术的发展历程

通用串行总线(USB)是一种广泛应用于计算机和各类电子设备的接口标准。自1996年第一代USB 1.0推出以来,经历了USB 2.0、USB 3.0、USB 3.1和最新的USB 4.0等多个版本的升级。每一版本都显著提升了数据传输速率和供电能力,逐步满足了市场对高速数据传输和设备快速充电的需求。

## 1.3 USB标准与传输速率分类

USB标准定义了不同版本的数据传输速率。USB 2.0的最大传输速率为480 Mbps,而USB 3.0引入了SuperSpeed技术,将速率提升至5 Gbps。后续版本如USB 3.1和USB 4.0进一步提升了传输速度,例如USB 4.0支持高达40 Gbps的数据传输速率,并且向下兼容USB 3.x。了解这些分类对于设计合适的接口连接和确保数据传输效率至关重要。

# 2. ```

# 第二章:上下拉电阻的工作原理

## 2.1 上下拉电阻的定义和功能

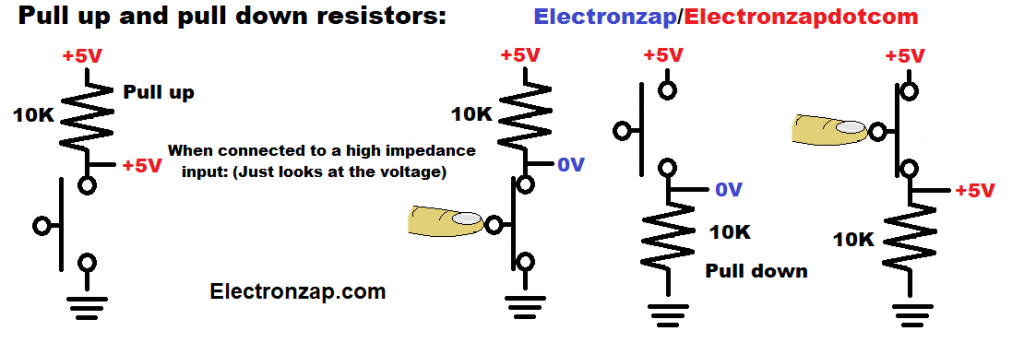

上下拉电阻是电子电路中常见的组件,其主要作用是确保输入引脚在未被明确驱动时有一个确定的逻辑电平。根据电路设计的需要,上拉电阻将未连接到电源的引脚拉至高电平(VDD),而下拉电阻则将引脚拉至低电平(GND)。

### 2.1.1 上拉电阻的作用

上拉电阻连接在输出引脚与正电源之间,当输出引脚处于高阻态(高阻抗,Hi-Z)时,上拉电阻将输出端拉至高电平,保证了输出端有一个稳定的逻辑状态。

### 2.1.2 下拉电阻的作用

与上拉电阻相对应的是下拉电阻,它连接在输出引脚与地线之间,当输出引脚处于高阻态时,下拉电阻会将输出端拉至低电平,同样保证了输出端有一个稳定的逻辑状态。

### 2.1.3 逻辑电平的维持

在数字电路中,上下拉电阻用于维持逻辑电平状态,确保在输入未被外部设备驱动时,电路不会出现浮空或不确定状态,从而避免产生逻辑错误。

## 2.2 上下拉电阻在电路中的作用机制

### 2.2.1 上拉电阻的工作过程

当一个数字电路的输出引脚为逻辑高电平时,上拉电阻限制电流流向输出引脚。当输出为低电平时,电流通过上拉电阻流出。

### 2.2.2 下拉电阻的工作过程

与上拉电阻相反,下拉电阻在输出引脚为低电平时限制电流从输出引脚流出;在高电平时,电流通过下拉电阻流入。

### 2.2.3 上下拉电阻的控制电路

在一些电路设计中,上拉或下拉电阻与其他控制逻辑配合,可以实现更复杂的电路功能。例如,上拉电阻可能与开关、晶体管等配合,用作使能控制。

## 2.3 上下拉电阻的规格选择与计算

### 2.3.1 选择合适的电阻值

选择上下拉电阻值时,通常需要平衡电阻值大小和引脚的电气特性。电阻值过小可能导致电流过大,损坏驱动电路;电阻值过大则可能无法提供足够的维持电平的能力。

### 2.3.2 计算上拉电阻值

上拉电阻的计算通常基于输出驱动电路的输出高电平最小电流(IOH)和输入端要求的最小高电平电压(Vih)。

```

\[ R_{up} = \frac{V_{DD} - V_{ih}}{I_{OH}} \]

```

### 2.3.3 计算下拉电阻值

下拉电阻的计算基于输出驱动电路的输出低电平最大电流(IOL)和输入端要求的最小低电平电压(Vil)。

```

\[ R_{down} = \frac{V_{il}}{I_{OL}} \]

```

### 2.3.4 实际应用中电阻值的确定

在实际应用中,还需要考虑电路板的布线、温度变化、湿度等因素对电阻的影响,电阻值的确定应留有适当的余量。

```

# 表格:典型上下拉电阻值的选取

| 应用场景 | 上拉电阻范围 (KΩ) | 下拉电阻范围 (KΩ) |

|----------|--------------------|--------------------|

| 微控制器 | 10 - 100 | 10 - 100 |

| 总线驱动 | 1 - 10 | 1 - 10 |

| 高速信号 | 1 - 5 | 1 - 5 |

```

通过上述的讨论和计算,我们对上下拉电阻的工作原理有了一个基础的理解。在下一章节中,我们将探讨上下拉电阻如何影响信号的完整性,特别是在USB传输环境中信号完整性的关键性因素。

# 3. 上下拉电阻对信号完整性的影响

在第二章中,我们已经了解了上下拉电阻的基础知识和它们在电路设计中的作用。在本章中,我们将深入探讨上下拉电阻如何影响信号完整性,这是电子工程中一个至关重要的概念。信号完整性涉及信号在传输过程中保持其质量和准确性的能力,包括信号的反射、串扰和抖动等问题。我们将从这些方面逐步剖析上下拉电阻的影响,为读者提供全面的认识。

## 3.1 上下拉电阻对信号反射的影响

信号反射是指信号在传输路径上由于阻抗不匹配而产生的一部分信号能量返回到源端的现象。这种现象会降低信号的完整性,导致接收端的信号失真。上下拉电阻能够在

```

0

0