【信号完整性分析】:分析并优化信号传输路径,提升系统性能的关键一步!

发布时间: 2024-12-17 03:39:15 阅读量: 32 订阅数: 27

参考资源链接:[STM32 ADC应用:太阳能电池板电压电流监测与数码管显示](https://wenku.csdn.net/doc/6412b75abe7fbd1778d49fed?spm=1055.2635.3001.10343)

# 1. 信号完整性基础概念

## 1.1 什么是信号完整性

信号完整性(Signal Integrity, SI)是电子工程领域内一个至关重要的概念,它涉及到电路设计中信号质量的保持。良好的信号完整性意味着信号在传输过程中可以保持其原有的时序和幅度特征,不会由于电路板设计不良而导致信号失真。

## 1.2 为何关注信号完整性

随着数字电子设备的运行速度不断加快,信号频率的提高使得原本可以忽略的小问题如反射、串扰、同步开关噪声等,开始显著地影响系统性能。因此,为确保高速数字电路的稳定性和可靠性,工程师必须关注并理解信号完整性。

## 1.3 信号完整性的关键参数

信号完整性主要关注的参数包括信号的上升/下降时间、传输延迟、阻抗匹配、反射系数、串扰水平等。通过对这些参数的仔细监控与控制,可以有效减小信号失真,提升电路性能。

在接下来的章节中,我们将深入了解不同信号完整性问题的具体类型及影响,探讨理论模型的构建,并将这些理论与实践中的测量、测试技巧相结合,最终提供信号完整性问题的优化解决方案,并展望未来技术发展的新趋势。

# 2. ```

# 第二章:信号完整性的理论分析

## 2.1 信号完整性问题的类型与影响

### 2.1.1 反射问题及其成因

信号反射是高速数字电路设计中的常见问题,它通常发生在传输线的终端或不连续处。当信号传输路径发生阻抗变化时,部分信号能量会被反射回信号源,导致信号波形失真。信号的反射可以是正反射或负反射,具体取决于阻抗的变化是增加还是减少。

阻抗不匹配是引起反射的主要原因。例如,当一个50Ω的信号线连接到一个100Ω的负载时,由于阻抗不匹配,会在负载处发生反射。为了减少这种反射,设计者会使用端接技术,如串联端接、并联端接、戴维宁端接或AC端接等方法,调整传输线和负载之间的阻抗匹配。

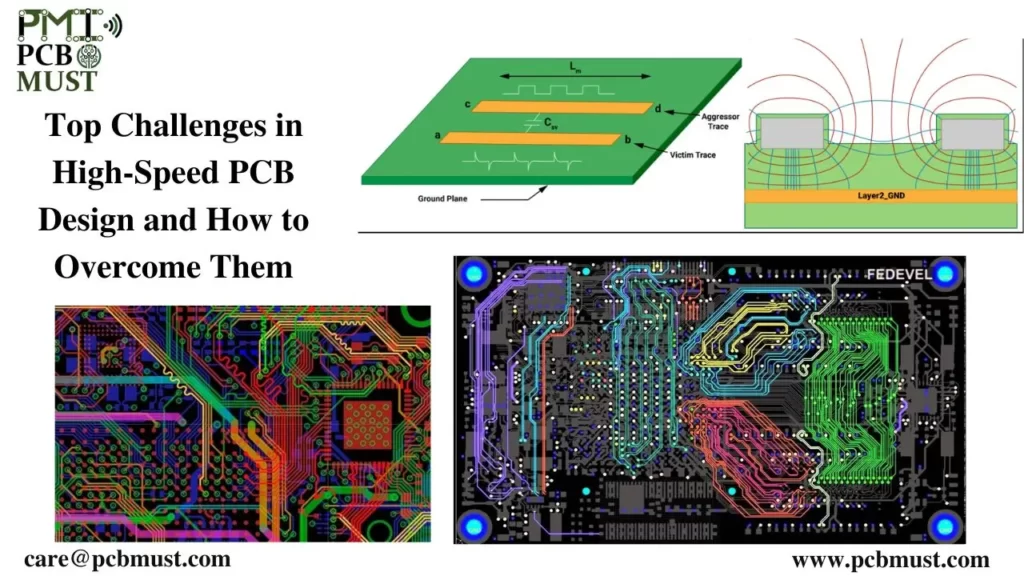

### 2.1.2 串扰问题及其影响

串扰是指在高密度互连的PCB板上,由于信号线间的电磁场耦合,一个信号线上的信号干扰了相邻信号线上的信号。串扰分为容性串扰和感性串扰,分别由于电容耦合和电感耦合而产生。

串扰的影响主要体现在信号质量的下降和误码率的增加上。在高速设计中,串扰可能会造成信号的眼图闭合,从而降低系统的可靠性。为了减少串扰,设计时应避免平行布线过长,尽可能使用地平面隔离,以及采用差分信号设计,因为差分信号在一定程度上可以抑制偶次谐波的串扰。

### 2.1.3 同步开关噪声和地弹噪声

同步开关噪声(SSN)和地弹噪声是与芯片封装相关的信号完整性问题,它们通常在IC芯片输出端发生快速切换时出现。SSN是由于IC封装内芯片和引线框架之间的寄生电感和封装引线电感导致的,而地弹噪声则是由于封装内部芯片和地之间的瞬间电流引起电压波动。

SSN和地弹噪声会导致芯片的供电电压暂时偏离正常值,从而影响芯片的正常工作。为了减少这些噪声,可以在设计中使用去耦合电容、电源平面分割和信号回流路径优化等技术。

## 2.2 信号完整性理论模型构建

### 2.2.1 传输线模型与IBIS模型

传输线模型是描述信号在传输线上传播的物理模型,它考虑了传输线的电阻、电感、电容和导纳参数。传输线模型对于理解信号如何在电路板上传播至关重要。常用的传输线模型有集总参数模型和分布参数模型。

IBIS(I/O Buffer Information Specification)模型是一种用于描述数字电路IC引脚的电气特性的模型,它包含了驱动器和接收器的行为特性。IBIS模型使用实际测量数据来描述IC引脚的电压-电流(V-I)曲线和电流-时间(I-T)曲线。这样,设计者就可以在不暴露核心芯片设计细节的情况下,进行信号完整性和电磁兼容性(EMC)的仿真分析。

### 2.2.2 信号完整性仿真工具与方法

信号完整性仿真工具能够在实际电路制造之前,对电路板上的信号完整性问题进行预测和评估。常见的仿真工具有HyperLynx、Ansoft Designer、Cadence Sigrity等。这些工具可以模拟传输线效应、端接效果、串扰、电源完整性以及电磁干扰(EMI)等问题。

信号完整性仿真通常遵循以下步骤:定义设计规范、建立电路模型、设置仿真参数、执行仿真、分析结果。设计者需要根据仿真结果调整设计,直到达到所要求的信号完整性指标。

## 2.3 高速信号的传输理论

### 2.3.1 高速信号的传播时延与阻抗

高速信号在传输介质中的传播时延是信号完整性设计中的一个关键因素。时延不仅取决于信号频率,还与传输介质的介电常数(εr)有关。在PCB中,FR4材料的介电常数大约是4.5左右,这意味着信号的传播速度大约是光速的1/√εr。

传输阻抗是信号完整性分析中的另一个重要因素。在理想情况下,传输线阻抗是均匀的,但实际上由于PCB的制造公差和信号路径上的不同材料,会产生阻抗不连续性。阻抗不连续会导致信号反射,影响信号的完整性。因此,设计者需要控制PCB生产过程,确保阻抗的一致性。

### 2.3.2 差分信号与单端信号的特性分析

差分信号传输是利用一对线来传输一个信号,它们以相反的相位和相同幅度进行传输。差分信号的一个主要优势是具有更好的噪声抑制能力,特别是在抑制共模噪声方面。差分信号对串扰也有很强的免疫能力,因为串扰通常会影响两个线的信号相同相位。

单端信号是指一个信号通过一个信号线和地线来传输。单端信号设计简单,但容易受到串扰和地线噪声的影响。在低频或对信号完整性和噪声免疫要求不高的应用中,单端信

```

0

0