音频信号处理的变革:I2S接口时钟管理与同步的终极教程

发布时间: 2024-12-29 08:27:35 阅读量: 11 订阅数: 19

数字音频接口(I2S,PCM,TDM,PDM).docx

# 摘要

I2S接口技术是一种广泛应用于数字音频设备中的标准接口协议,用于实现高质量音频信号的传输。本文首先概述了I2S接口技术的基本概念和重要性,随后深入探讨了其时钟管理的基础知识,包括时钟信号的理论、分类、同步机制、频率配置以及校准技术。文章进一步通过案例分析,详细说明了I2S同步实践中的具体步骤和评估优化方法。最后,本文探讨了I2S同步的高级技术、软件开发相关问题和音频信号处理中的应用,以及技术创新和未来发展趋势。

# 关键字

I2S接口;时钟管理;同步技术;频率配置;音频信号处理;技术创新

参考资源链接:[数字音频接口详解:I2S、PCM与PDM](https://wenku.csdn.net/doc/548i28kryz?spm=1055.2635.3001.10343)

# 1. I2S接口技术概述

## 1.1 I2S接口的定义与作用

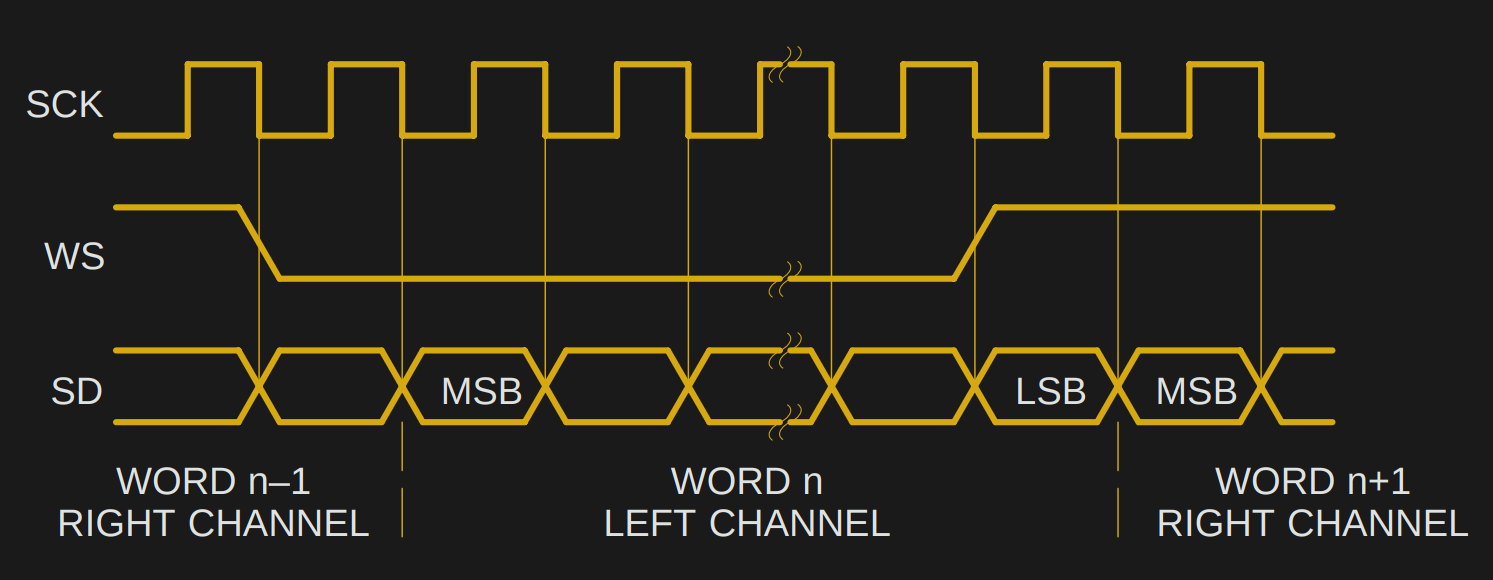

I2S(Inter-IC Sound)是一种音频通信协议,用于在数字音频设备之间传输音频数据。它由飞利浦公司在1980年代提出,主要用于解决数字音频的串行传输问题。I2S接口通过三个独立的信号线——时钟线(SCK)、字选择线(WS)和串行数据线(SD)——实现高保真的音频信号传输,广泛应用于专业音频设备、消费电子和车载娱乐系统中。I2S接口不仅简化了设备间的连接,还因为其高稳定性和低噪声性能,成为音频处理领域的重要技术标准之一。

## 1.2 I2S接口的工作原理

I2S接口的工作原理基于一系列的时序控制信号,以确保音频数据在源设备和目的地设备之间正确传输。它采用主从架构,其中主设备负责生成时钟信号,而从设备则根据这个时钟信号同步接收数据。I2S协议定义了数据传输的格式,规定了在时钟信号的驱动下,数据的传输顺序和位对齐方式。具体来说,字选择线(WS)用于区分左右声道数据,而串行数据线(SD)用于传输音频数据位流。这种精确的信号控制保证了音频数据的准确性和完整性,是高质量音频输出不可或缺的技术支撑。

## 1.3 I2S接口的应用领域与未来趋势

随着数字音频技术的不断进步,I2S接口的应用领域也在持续扩展。它不仅仅局限于传统的音频设备,还被集成到智能家居、便携式音频播放器、VR设备以及汽车音响系统中。随着技术的发展,未来的I2S接口将进一步提升数据传输速率,支持更多的音频通道,并且在保持低延迟的同时减少功耗。同时,随着新的音频技术如3D音频、高分辨率音频的发展,I2S接口也面临着技术升级的需求,以满足未来音频领域对于高保真音质和复杂音频处理的更高要求。

# 2. I2S时钟管理基础

在数字音频系统中,I2S时钟管理是一个核心话题,它是确保音频信号准确同步与传输的关键。为了深入理解I2S时钟管理的基础知识,本章将先从时钟信号的理论知识开始,然后探讨I2S时钟同步机制,并在最后介绍如何配置和校准I2S时钟频率。

## 2.1 I2S时钟信号的理论知识

### 2.1.1 时钟信号的作用与重要性

在数字音频信号处理中,时钟信号的作用至关重要。它为数据的采样和传输提供了一个统一的时间基准,确保数字信号可以准确无误地在不同的设备之间传输。没有一个稳定的时钟信号,数字音频系统将无法有效地同步,从而导致音频质量的劣化,例如出现杂音、断音或者频率失真等问题。

### 2.1.2 I2S时钟信号的分类与特点

I2S(Inter-IC Sound)接口使用两种时钟信号:位时钟(Bit Clock,BCLK)和左/右声道时钟(Word Select,LRCLK)。位时钟负责同步每一位数字音频信号的传输,其频率取决于音频数据的位深度和采样率。而声道时钟则用于指示当前是左声道数据还是右声道数据,其频率通常等于采样率。

不同设备对时钟信号的精确度和稳定性有不同的要求。例如,高性能的数字信号处理器可能需要更稳定的时钟源以保持最佳的音频输出质量。

## 2.2 I2S时钟同步机制

### 2.2.1 同步时钟信号的生成

实现I2S时钟同步的核心在于生成稳定的时钟信号。通常情况下,可以使用专门的时钟发生器芯片来产生所需的位时钟和声道时钟。时钟发生器的输出频率必须精确,以避免采样率的微小变化对音频质量产生不良影响。

### 2.2.2 同步过程中的常见问题及解决方案

在同步过程中,常见的问题包括时钟漂移、时钟抖动和频率失配等。这些问题可能会导致音频信号的同步失效。为解决这些问题,设计者通常会在系统中加入锁相环(PLL)电路,以维持时钟信号的稳定。此外,通过软件校准来动态调整时钟频率,也是一个有效的解决策略。

## 2.3 I2S时钟频率的配置与校准

### 2.3.1 频率配置的基本原理

I2S时钟频率的配置需要依据音频信号的采样率和位深度来设置。通常,音频设备会根据采样率确定位时钟频率。例如,一个CD质量的音频信号采样率为44.1kHz,位深度为16位,则位时钟频率应为44.1kHz × 16 = 705.6kHz。

### 2.3.2 校准技术的实际应用

校准技术是确保音频设备之间完美同步的关键。在实际应用中,校准通常需要软件和硬件的协同工作。硬件层面上,校准可以使用外部时钟源或者高精度晶振来提高时钟信号的稳定性。在软件层面上,则通过分析音频信号的时序来动态调整时钟频率,确保各个通道之间的同步。

## 实践案例

接下来,我们将通过一个实际案例来演示如何配置和校准I2S时钟频率。

### 2.3.1 频率配置基本原理的实际应用

我们假设需要配置一个具有48kHz采样率和24位深度音频设备的I2S时钟频率。

首先,我们需要计算出该设备的位时钟频率:

\[ 48 \text{kHz} \times 24 = 1152 \text{kHz} \]

接下来,我们使用一个可编程的时钟发生器来生成这个频率。如果硬件条件允许,我们也可以使用一个固定频率的晶振。

```c

// 伪代码示例

// 配置时钟发生器产生1152kHz的位时钟频率

configure_clock_generator(1152000);

```

### 2.3.2 校准技术的实际应用

校准过程通常发生在音频设备启动时,可能需要根据设备的反馈信号动态调整时钟频率。

```c

// 伪代码示例

// 校准函数,动态调整位时钟频率以匹配接收端设备

calibrate_clock_to_device(target_device);

```

在这个过程中,发送端设备会通过监听接收端的反馈,动态地调整自身的位时钟频率,直到两个设备的同步误差降到最小。

## 小结

本章节对I2S时钟管理的基础知识进行了深入讲解,涵盖了时钟信号的理论知识、同步机制以及配置与校准技术。我们通过实际案例演示了如何将理论知识应用于实践中,为读者提供了一种可行的实践方法。在下一章中,我们将进一步深入,探讨I2S同步实践案例分析。

# 3. I2S同步实践案例分析

## 3.1 案例选择与同步前的准备

### 3.1.1 选择适合实践的音频设备

在开始I2S同步实践之前,选择合适的音频设备是至关重要的。音频设备的选择基于多个因素,包括所需的信号质量、设备的兼容性以及预期的应用场景。例如,在专业录音和回放应用中,可能需要选择具有高动态范围和低噪声水平的高性能转换器。而对于消费级音频设备,成本效益和易用性可能成为更重要的考量因素。

为了确保设备支持I2S协议,需要检查设备的技术规格,确认其是否支持I2S接口以及具体的时钟和数据引脚配置。此外,确认设备的时钟频率范围是否符合预期应用的要求,以及设备是否支持所需的采样率和采样深度。

### 3.1.2 同步前的系统配置与检查

在进行同步操作之前,需要对系统进行全面的配置和检查,确保硬件和软件的兼容性。首先,确保所有连接的音频设备都已正确连接,并且所有的I2S引脚(如BCLK、LRCLK、DATA)都正确对齐。还需要检查电源和接地连接,以确保没有接地环路,这可能会引入额外的噪声或干扰。

在软件层面,需要设置或更新音频驱动程序以确保它们与硬件设备兼容,并且可以支持I2S协议。对于嵌入式系统,可能需要编写或修改设备树(Device Tree)配置文件以反映I2S硬件的具体细节。此外,可能还需要配置音频子系统以处理I2S数据流,包括确定正确的采样率和格式。

## 3.2 I2S同步流程的实现步骤

### 3.2.1 硬件连接与初始化设置

在硬件层面,实现I2S同步的第一步是正确连接音频设备的引脚。以典型的I2S设

0

0