【DDR5内存SPD管理工具】:提升JEDEC JESD400-5标准下的工作效率

发布时间: 2024-12-17 16:35:06 阅读量: 1 订阅数: 4

JEDEC JESD400-5 DDR5 SPD Contents

参考资源链接:[DDR5 SPD规格:JEDEC JESD400-5详解](https://wenku.csdn.net/doc/6r5mbz0dzf?spm=1055.2635.3001.10343)

# 1. DDR5内存技术概述

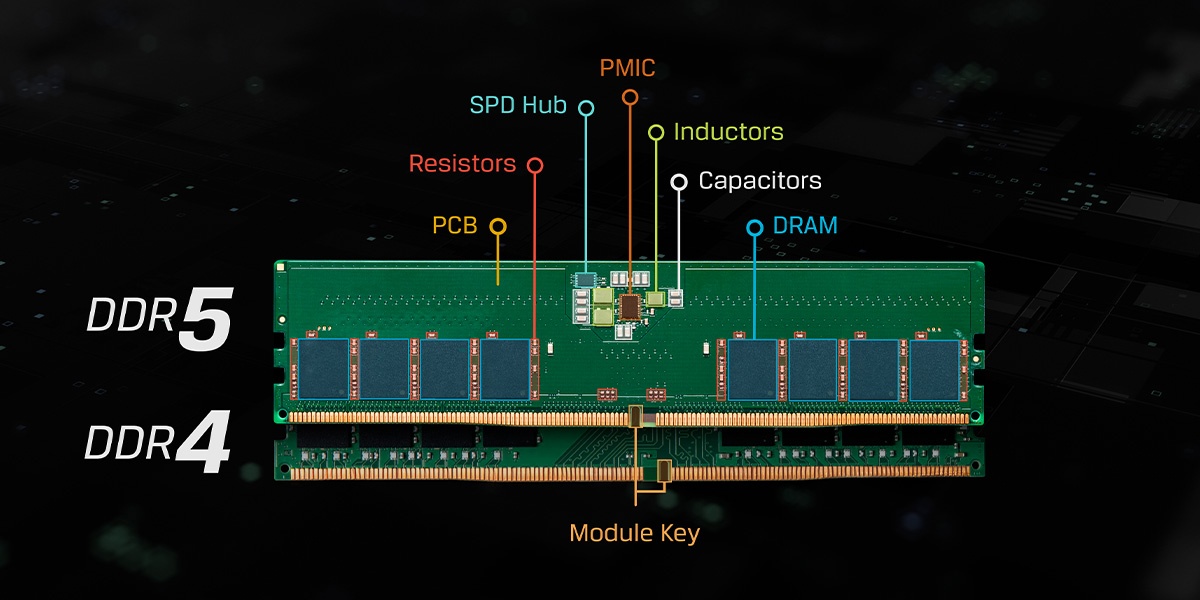

## 1.1 内存技术的进展

随着科技的发展,硬件需求不断提升,内存技术也在不断地进步。DDR5作为最新的内存技术标准,延续了前代DDR4的高带宽与低功耗特点,同时在性能和效率上实现了显著的飞跃。DDR5为内存行业带来了更高的速度、更大的容量以及更智能的电源管理功能,以满足日益增长的高性能计算需求。

## 1.2 DDR5的关键创新

DDR5内存技术的核心创新包括更高的数据传输速率、增加的Bank Group数量、以及电源管理的优化。DDR5的起始频率在4800MT/s以上,相比DDR4有大幅度提高。此外,它采用了一种新的数据纠错机制,提高了数据传输的准确性与可靠性。

## 1.3 DDR5的市场影响

对于服务器、工作站和高性能计算平台,DDR5提供了更高的性能,预计将迅速成为这些领域的主流内存技术。随着制造成本的下降和生产规模的扩大,我们可以预见DDR5将在未来的几年内逐渐取代DDR4,成为新计算机系统的标配内存。

# 2. JEDEC JESD400-5标准解析

## 2.1 标准的历史背景和演进

### 2.1.1 DDR技术的发展历程

DDR(Double Data Rate)技术自推出以来,一直扮演着内存行业中的重要角色。其演进史几乎等同于现代计算机处理能力提升的历程。DDR技术首次被引入时,它以相对传统SDRAM(Synchronous Dynamic Random Access Memory)两倍的数据传输速率,为个人电脑和服务器带来了显著的性能提升。

随着技术的不断进步,JEDEC(Joint Electron Device Engineering Council,电子设备工程联合委员会)逐步推出了后续的标准,如DDR2、DDR3和现在的DDR4,每个新标准都通过增加更高的时钟频率、更宽的数据通道、更低的电压和更先进的架构来提升性能。DDR4的出现让内存的频率进一步提高,能耗降低,为高端设备的运行效率和能效比提供了新的标准。

DDR5作为最新一代的技术标准,正开始进入市场。DDR5通过采用更高的时钟频率和更优化的通道架构,在继续保持能耗效率的基础上,提供了比以往任何一代DDR技术都要高的数据传输速度,这对于未来高性能计算、数据中心和人工智能应用来说,意味着新的性能标准。

### 2.1.2 JEDEC标准的形成与影响

JEDEC标准的形成是一个多方参与、共同协作的过程。JEDEC负责制定存储器相关的技术标准,其标准的影响力覆盖了全球,成为电子行业内存技术的基准。每一个新版本的内存技术标准的发布,都意味着设备制造商、软件开发者和最终用户将面临新的技术规范和性能提升。

JEDEC标准的形成历经多年研究,从内存制造商、处理器设计者到系统集成商,每个成员都在标准的制定中贡献了自己的知识和经验。JEDEC通过开放的讨论和标准化过程,确保了标准的普遍性和适用性,这使得它成为了行业内被广泛接受和遵循的规范。

JEDEC标准对行业的影响不仅仅局限于技术层面,它还指导了整个产业的发展方向。新标准的发布促进了新一代内存技术的开发,同时也推动了与之配套的硬件和软件工具的创新。这些变化不仅提升了现有系统的性能和效率,也为新兴应用打开了大门,例如AI和高性能计算等。

## 2.2 JESD400-5标准核心内容

### 2.2.1 内存规格与性能参数

DDR5内存规范在技术参数上有显著的跃进,这一跃进主要体现在其性能参数上。相比于DDR4,DDR5实现了更高的起始频率,并且内存制造商能够生产出更高速率的内存模块。

具体来说,DDR5的起始数据传输速率达到了4.8Gbps,是DDR4的两倍。它支持高达6400MHz的数据传输速率,这样的速度可以显著提升内存带宽,优化数据密集型应用的性能,如高分辨率图像处理、视频编辑和高性能计算等。

除了速度的提升,DDR5还引入了新的节能特性,如电源管理集成电路(PMIC)集成到内存模块内部,以实现更精准的电源管理。这不仅降低了系统整体的功耗,还有助于延长电池寿命,特别是在移动设备中。

### 2.2.2 SPD编程与管理要求

SPD(Serial Presence Detect)作为内存条中用于存储内存参数和特性信息的芯片,对内存的正确配置至关重要。DDR5沿袭并提升了SPD的标准化和编程要求,以确保在不同系统和应用场景下内存模块能被正确识别和管理。

在JESD400-5标准中,SPD包含了更多关于内存规格和性能的信息,如电压、时序参数、工作频率等,来支持系统硬件自动配置内存。这意味着内存管理工具需要能够读取和解释SPD信息,以完成诸如错误检测、性能优化和故障排除等工作。

SPD编程与管理要求的提升,带来了内存模块与系统之间更复杂的交互过程,为了适应这一变化,相关软件和硬件工具都必须进行相应的更新和优化。这既是对内存制造商的一种挑战,也是对内存管理工具开发者的一种机遇。

## 2.3 标准对内存管理工具的影响

### 2.3.1 硬件兼容性与测试标准

DDR5内存的推出不仅带来了内存本身的性能跃进,也对内存管理工具的兼容性和测试标准提出了新的要求。为了确保内存模块在不同的硬件平台上能够无缝工作,内存管理工具必须能够识别并支持新的SPD规格。

硬件兼容性方面的测试标准在DDR5时代变得更加严格,这是因为DDR5内存提供了更多定制化的性能参数。测试工具需要在硬件层面进行详细的兼容性验证,确保内存可以和主板、CPU等其他组件协同工作。这一过程不仅涉及到基本的性能测试,还包括了稳定性、发热、功耗等多方面的综合评估。

在这一部分,内存工具开发者需要密切关注DDR5内存的发布动态和内存制造商的技术文档,确保其工具能够及时适应新的内存规格变化。这样,用户在升级内存或是配置新系统时,才能获得最佳的性能和稳定性。

### 2.3.2 软件工具的开发趋势

随着DDR5内存技术的发展和JEDEC标准的不断更新,软件工具的开发趋势也在相应地发生变化。对于内存管理工具来说,性能监控、故障诊断、自动化配置等方面的需求日益增长。

开发趋势之一是工具的智能化,这意味着内存管理软件能够基于内存模块提供的SPD信息进行自我调整,以达到最优的内存配置。智能化工具能够减轻用户在内存优化方面的负担,为用户节省时间并提供稳定可靠的系统性能。

另一个开发趋势是用户界面的简化和用户体验的提升。现代内存管理工具不仅需要拥有强大的内核功能,还需要友好的用户界面,以降低用户操作的复杂性。这涉及到用户交互设计(UI/UX)的优化,包括图形化界面、步骤提示、反馈系统等。

## 2.3.3 具体操作步骤和代码实现

在本章的剩余部分,我们将通过具体的操作步骤和代码实现来讨论如何实现DDR5内存SPD管理工具的开发。

### 操作步骤概述

为了有效管理DDR5内存,内存管理工具必须能够执行以下基本操作:

1. **读取SPD信息**:工具首先需要能够从DDR5内存条上的SPD芯片读取信息。

2. **解析SPD数据**:获取SPD数据之后,工具需要正确解析这些数据以了解内存的性能参数和规格。

3. **性能测试和校验**:进行内存性能测试以确保内存条的性能符合规格要求。

4. **故障诊断**:工具还需要提供故障诊断功能,以便用户能够检测和解决内存问题。

### 代码实现

以下是一段简单的示例代码,用于读取DDR5内存条上的SPD信息:

```python

import smbus

# 初始化SPD的I2C地址和所需寄存器地址

SPD_I2C_ADDRESS = 0x50

SPD_REG_ADDRESS = 0x00

# 打开I2C总线

bus = smbus.SMBus(1)

def read_spd_data(address, register):

"""

从指定的SPD I2C地址和寄存器地址读取数据。

"""

# 读取SPD数据的字节

data = bus.read_i2c_block_data(address, register, 128)

return data

# 从SPD芯片读取数据

spd_data = read_spd_data(SPD_I2C_ADDRESS, SPD_REG_ADDRESS)

# 这里可以根据需要对spd_data进行进一步的处理和解析

```

**代码逻辑分析:**

1. 我们使用了Python的`smbus`库来与I2C总线通信,因为SPD芯片可以通过I2C接口进行通信。

2. `SPD_I2C_ADDRESS`和`SPD_REG_ADDRESS`是SPD芯片的标准地址和寄存器地址。

3. `read_spd_data`函数负责从SPD芯

0

0