【高级设计技术】:全加器在VLSI数字电路中的应用实例:电路设计的高级技巧

摘要

本文深入探讨了全加器在数字逻辑和VLSI设计中的应用及其优化技术。首先介绍了全加器的基本原理及其在数字电路设计中的基础应用,然后通过具体的应用实例展示了全加器在组合逻辑和时序逻辑电路中的关键作用。接着,文章分析了全加器在现代芯片设计中所面临的功耗、性能和面积优化挑战,并探讨了应对设计新挑战的策略。最后,文中展望了全加器设计的未来趋势,包括与新兴计算范式的集成以及可重构硬件和可持续性设计的方向。本文还包含了基于实际案例的研究和分析,为全加器设计的优化提供了实用的建议和资源分享。

关键字

全加器;数字逻辑;VLSI设计;优化技术;功耗管理;可持续性设计

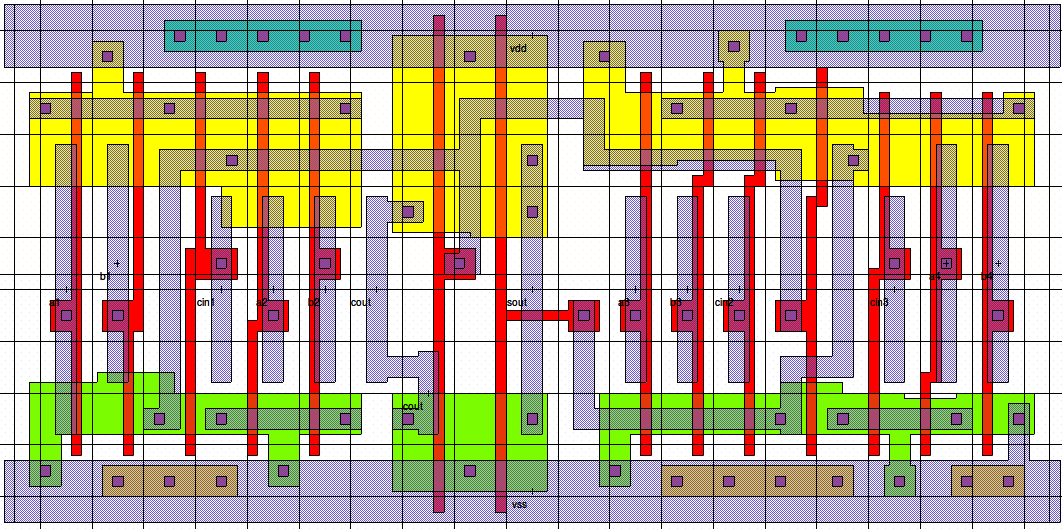

参考资源链接:0.18um工艺镜像全加器设计与仿真:VLSI电路实现

1. 全加器在数字逻辑中的基本原理

全加器是数字逻辑设计中的基础构建模块,它能够实现两个二进制位以及一个进位输入的加法运算,并输出和位以及进位位。全加器的核心在于处理输入的每一位加法以及进位的逻辑运算。其基本原理基于布尔代数,通过逻辑门电路实现加法和进位的功能。一个标准的全加器通常由两个半加器(实现不考虑进位的加法)和一个或门(实现进位的传递)构成。

在设计全加器时,首先要考虑的是其逻辑功能。全加器有两个输入位(记为A和B)和一个进位输入(记为Cin),输出有两个:和位(记为Sum)和进位输出(记为Cout)。其逻辑表达式可以表示为:

- Sum = A ⊕ B ⊕ Cin

- Cout = (A ∧ B) ∨ (B ∧ Cin) ∨ (A ∧ Cin)

其中,“⊕”表示异或运算,“∧”表示与运算,“∨”表示或运算。接下来的章节,我们将详细探讨VLSI数字电路设计的基础,以及全加器如何在更复杂的电路设计中应用。

2. ```

第二章:VLSI数字电路设计基础

2.1 VLSI设计流程概述

2.1.1 设计阶段与方法论

在设计极大规模集成电路(VLSI)时,通常遵循一系列设计流程,这有助于确保最终产品的可靠性和性能。VLSI设计流程大致可以分为几个阶段:系统级设计、寄存器传输级(RTL)设计、逻辑综合、物理设计、验证和制造。在每个阶段,工程师需要根据设计目标和约束条件选择适当的方法论和工具。

系统级设计是定义整个电路功能特性和性能指标的阶段。在这个阶段,工程师使用系统描述语言如SystemC来模拟和验证高层次的系统行为。紧接着的RTL设计阶段,设计师将系统行为细化为可由硬件描述语言(HDLs)如VHDL或Verilog表达的详细逻辑。然后,逻辑综合阶段将RTL代码转换为逻辑门级的网表,该网表反映出了所需逻辑功能与实际可用逻辑门之间的对应关系。

物理设计阶段,也称为布局与布线,涉及将逻辑门映射到物理芯片上,并确保它们之间的电气连接。验证是贯穿于整个设计过程的重要部分,确保设计符合规格并且没有任何错误。最后,在所有设计阶段完成后,产品将送至制造阶段。

2.1.2 硬件描述语言在VLSI中的应用

硬件描述语言(HDL)是VLSI设计中不可或缺的一部分,它们使设计师能够以文本形式描述硬件的结构和行为。VHDL和Verilog是最广泛使用的HDLs,它们为设计复杂的数字电路提供了结构化和模块化的语言。

设计者使用HDL编写代码来表达电路的逻辑和时序特性,之后通过仿真工具进行测试和验证。HDL代码经过逻辑综合之后,生成可以在实际硬件中实现的门级描述。例如,一个全加器可以用以下Verilog代码描述:

- module full_adder (

- input a,

- input b,

- input cin,

- output sum,

- output cout

- );

- assign sum = a ^ b ^ cin; // 异或操作实现求和

- assign cout = (a & b) | (b & cin) | (a & cin); // 与和或操作实现进位

- endmodule

上述代码中,^是按位异或操作符,&是按位与操作符,而|是按位或操作符。这种模块化的描述方式便于仿真与测试,并且能够被逻辑综合工具处理转换为门级网表。

2.2 全加器的功能与设计

2.2.1 全加器逻辑电路的理论基础

全加器是数字电路中的基础构建块,它能够实现两个一位二进制数以及一个进位输入的相加,并输出和与进位。全加器由两个部分组成:求和逻辑和进位逻辑。

求和逻辑由一个异或门实现,因为异或操作的输出会在输入不同时为1,在输入相同时为0。对于进位逻辑,必须考虑三个输入中任意两个输入同时为1时的情况,这将产生一个进位输出。因此,进位逻辑通常由与门和或门组合实现。

理论基础之外,全加器的设计还需要考虑实际应用中的延迟、功耗和面积等因素。为了设计一个高效的全加器,设计师需要对基本的逻辑门进行优化,有时甚至需要设计自定义的门电路来满足特定的需求。

2.2.2 高级全加器设计技术

高级全加器设计技术关注于优化全加器在速度、功耗和面积等关键参数。例如,通过逻辑优化技术可以降低全加器的延迟,这包括使用逻辑简化技术来减少逻辑门数量,以及使用更快的逻辑门替代标准的逻辑门。

卡诺图是一种常用的逻辑简化工具,它可以帮助设计师通过图形化方式来最小化布尔逻辑表达式。例如,一个全加器的和输出可以被简化为:

- sum = a ⊕ b ⊕ cin

其中 ⊕ 表示异或操作。类似地,进位输出可以简化为:

- carry = (a ∧ b) ∨ (b ∧ cin) ∨ (a ∧ cin)

其中 ∧ 表示与操作,∨ 表示或操作。通过这种方式,设计师可以进一步提升全加器的性能。

除了优化延迟外,功耗的优化也非常重要,特别是对于便携式设备或高集成度芯片。全加器的设计可以采用低功耗门,如CMOS技术,它通过控制nMOS和pMOS晶体管的导通和截止来减少静态功耗。在面积方面,设计者可以采用多路复用技术来减少晶体管数量,进一步减小电路占用的芯片面积。

2.3 电路设计的仿真与验证

2.3.1 仿真工具的选择与应用

为了确保全加器和更复杂的数字电路设计符合功能规格,仿真工具的使用是不可或缺的一步。选择合适的仿真工具对于验证阶段的成功至关重要。常见的仿真工具有ModelSim、VCS和Icarus Verilog等。

这些工具允许设计师在实际制造芯片之前测试和验证电路设计的功能正确性。以ModelSim为例,设计师可以使用它来进行Verilog或VHDL代码的仿真。设计者可以通过编写测试平台(testbench)来生成输入信号,并观察输出信号以验证电路的功能。

使用仿真工具进行全加器设计的验证示例代码:

- // 测试平台代码

- module full_adder_tb;

- reg a, b, cin;

- wire sum, cout;

- // 实例化全加器模块

- full_adder fa1 (

- .a(a),

- .b(b),

- .cin(cin),

- .sum(sum),

- .cout(cout)

- );

- // 测试过程

- initial begin

- // 初始化输入

- a = 0; b = 0; cin = 0;

- #10; // 等待10个时间单位

- a = 0; b = 0; cin = 1;

- #10;

- a = 0; b = 1; cin = 0;

- #10;

- a = 0; b = 1; cin = 1;

- #10;

- a = 1; b = 0; cin = 0;

- #10;

- a = 1; b = 0; cin = 1;

- #10;

- a = 1; b = 1; cin = 0;