VHDL万年历设计:代码优化与性能提升

发布时间: 2024-12-16 22:30:15 阅读量: 1 订阅数: 3

参考资源链接:[VHDL课程设计--万年历,课程设计报告。包括各个模块的代码及仿真图](https://wenku.csdn.net/doc/6412b6debe7fbd1778d4843b?spm=1055.2635.3001.10343)

# 1. VHDL万年历设计的理论基础

在探讨VHDL万年历设计的理论基础之前,我们首先需要理解什么是VHDL。VHDL,全称为VHSIC Hardware Description Language(超高速集成电路硬件描述语言),是一种用于描述电子系统硬件功能、行为和结构的计算机语言。它广泛应用于数字电路设计与系统级芯片(SoC)的设计中,非常适合于实现复杂的时序逻辑和并发控制。

万年历作为一种需要精确日期计算和时间管理的工具,其设计的复杂性在于它需要处理不同历法之间的转换、闰年规则、以及不同文化中节假日的变动。在硬件层面,这就需要一个既能够处理这些复杂逻辑,又能保证时间精确的解决方案。

VHDL提供了一套完整的工具来实现这一目标。首先,VHDL的并发性允许设计者同时处理多个事件和逻辑,这对于并行处理各种时间计算非常有用。其次,VHDL中的状态机设计可以帮助我们管理和控制各种状态,这对于实现复杂的逻辑和时序要求至关重要。接下来,我们将深入探讨VHDL代码的结构和优化方法,以及如何将这些理论应用到万年历的设计中。

# 2. VHDL代码的结构与优化

### 2.1 VHDL代码的基础结构

#### 2.1.1 实体和架构的定义

VHDL代码的基础结构主要由“实体”(entity)和“架构”(architecture)两部分组成。实体部分描述了硬件模块的接口,而架构部分则具体实现了这些接口的内部逻辑。

```vhdl

entity Calendar is

port (

clk : in std_logic; -- 时钟信号

reset : in std_logic; -- 复位信号

date_output : out std_logic_vector(11 downto 0) -- 输出日期信号

);

end Calendar;

```

上述代码中的实体`Calendar`定义了三个端口:`clk`是时钟输入端口,`reset`是复位信号,`date_output`用于输出当前日期。

架构部分使用实体中定义的端口并描述内部的行为。

```vhdl

architecture Behavioral of Calendar is

-- 在这里实现内部逻辑

begin

-- 行为描述

end Behavioral;

```

在这个架构的实现中,我们可以进一步定义信号和进程来描述硬件的行为。

#### 2.1.2 信号和数据类型的应用

VHDL中的信号用于在实体和架构之间以及架构内部的不同进程之间传递信息。数据类型则定义了信号可以持有的值的类型。

```vhdl

signal current_date : std_logic_vector(11 downto 0); -- 内部信号定义

```

在这个例子中,`current_date`是一个信号,它被用来存储和传递日期信息。使用`std_logic_vector`数据类型允许我们在数字逻辑中表示二进制值。

### 2.2 VHDL代码的重用与模块化

#### 2.2.1 组件的封装和实例化

组件封装和实例化是模块化设计的关键步骤,它允许设计者创建可重用的硬件模块。

```vhdl

component DateCalculator

port (

clk : in std_logic;

reset : in std_logic;

date : out std_logic_vector(11 downto 0)

);

end component;

-- 实例化组件

uut : DateCalculator

port map (

clk => clk,

reset => reset,

date => date_output

);

```

这段代码展示了如何定义一个名为`DateCalculator`的组件,并在更高的架构中实例化它。通过`port map`语句将外部端口映射到组件的端口上。

#### 2.2.2 库和包的管理

库和包为VHDL代码提供了一种组织方式,使得代码的管理更为高效和模块化。

```vhdl

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

-- 使用自定义包

use work.CalendarPack.all;

```

在这里,`IEEE`库提供了标准的逻辑和数值类型,`work`库则引用了当前工作空间中的`CalendarPack`包。这些库和包的使用使得代码更加清晰和易于维护。

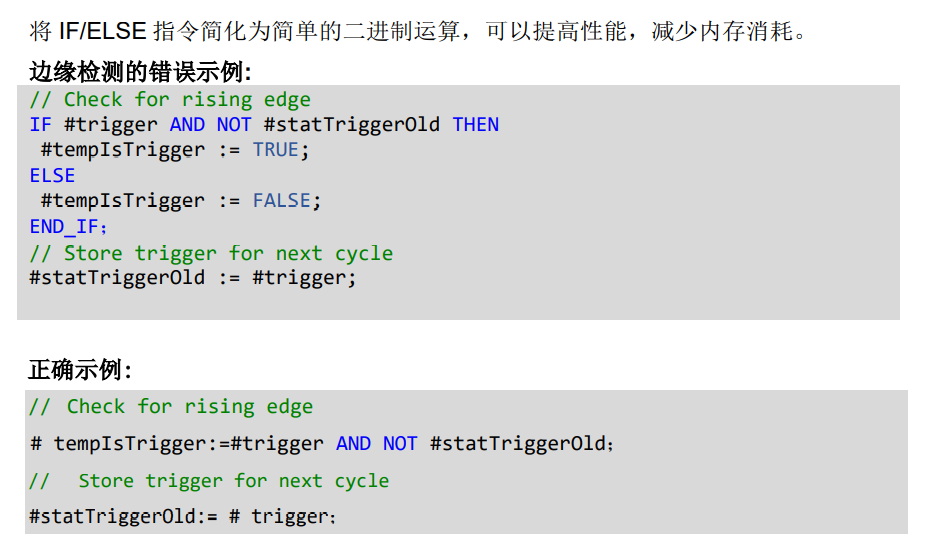

### 2.3 VHDL代码性能优化策略

#### 2.3.1 逻辑优化与资源分配

在VHDL中进行逻辑优化通常涉及减少逻辑门的数量,或者更高效地使用硬件资源。

```vhdl

-- 一个简单的优化示例:使用二进制运算代替条件逻辑

current_date <= std_logic_vector(unsigned(current_date) + 1);

```

在这个例子中,使用了无符号加法`+`替代了条件运算,从而减少了组合逻辑的复杂度。

#### 2.3.2 时序分析与约束

为了确保VHDL设计在实际硬件上按照预期工作,必须进行时序分析和施加相应的时序约束。

```vhdl

attribute max_delay : integer;

attribute max_delay of clk : signal is 10; -- 时钟信号的最大延迟为10纳秒

```

在这个例子中,通过在代码中设置`max_delay`属性来施加时序约束,确保设计在FPGA中运行时满足时序要求。

这种性能优化不仅提高了硬件效率,同时也保证了设计的可靠性。在实际的硬件设计过程中,时序分析是至关重要的一步,它确保了设计在不同的工作条件下都能正常工作。

通过综合以上讨论的VHDL代码基础结构、重用与模块化以及性能优化策略,设计者可以创建出既可靠又高效的硬件设计。这些技术的结合使用使得设计者能够在编码阶段就预见并解决潜在的硬件设计问题,从而在硬件实现阶段减少调试时间,提高设计质量。

# 3. 万年历算法实现与优化

## 3.1 万年历算法逻辑设计

### 3.1.1 日期计算和验证

在设计万年历算法时,日期的计算和验证是核心。日期计算涉及到日历的常规运算,比如判断某一天是星期几、计算两个日期之间的天数差、确定某个月有多少天等。VHDL在实现这些功能时需要考虑日期的边界条件,如闰年和不同月份的天数变化。

为了实现这样的算法,我们通常使用Zeller公式或基姆拉尔森计算公式。以下是使用Zeller公式在VHDL中计算星期的代码片段:

```vhdl

function get_weekday(day, month, year : integer) return integer is

variable K, M : integer;

begin

if month < 3 then

K := year - 1;

M := month + 12;

else

K := year;

M := m

```

0

0