【FPGA性能优化布线】:提升性能的布线与布局策略

发布时间: 2024-12-25 14:07:12 阅读量: 7 订阅数: 12

基于C++的nextpnr便携式FPGA布局布线工具源码分析

# 摘要

本文综合探讨了FPGA布线与布局的基础理论、优化实践、策略及其在性能提升中的应用。首先介绍了FPGA布线与布局的基础知识,然后深入分析了布线长度控制、信号完整性、逻辑资源与布线资源之间的关系。接着,文章详细讨论了时序闭合与布线策略的重要性,并提供了实际布线优化的案例分析。在布局优化方面,文章探讨了模块化布局方法、多时钟域布局技术以及自动化布局工具的应用。最后,通过综合案例展示了优化实施过程和效果分析,并对未来FPGA性能优化的趋势与展望进行了讨论。本文旨在为FPGA设计人员提供全面的性能优化指南,并对新技术在FPGA领域的应用提出前瞻性分析。

# 关键字

FPGA;布线与布局;信号完整性;时序闭合;性能优化;自动化布局工具

参考资源链接:[FPGA在图像处理中的角色:3A算法与ISP](https://wenku.csdn.net/doc/6mxnq5r65p?spm=1055.2635.3001.10343)

# 1. FPGA布线与布局基础

## FPGA简介

FPGA(现场可编程门阵列)是一种可以通过编程来配置其硬件功能的半导体器件,广泛应用于数字信号处理、通信、网络等领域。FPGA的布线与布局设计直接影响到电路性能和系统稳定性。

## 布线与布局的重要性

布线和布局是FPGA设计的关键阶段,它们决定了信号路径、时序闭合和热管理等关键因素。良好的布局可以使FPGA的逻辑资源得到最优化利用,而精确的布线可以降低延迟,减少信号干扰,从而提升整体性能。

## 布线与布局的基本步骤

- 确定核心模块和接口位置:根据电路的逻辑功能和信号流向确定各个模块的位置。

- 布线:根据信号路径的优先级进行布线,关键信号优先处理。

- 优化:通过仿真和实际测试结果,对布局和布线进行调整,以满足时序和热设计要求。

在后续的章节中,我们将深入探讨FPGA布线与布局的理论基础和优化策略,以及如何通过实践案例来提升FPGA的性能表现。

# 2. FPGA布线与布局理论

## 2.1 信号完整性与布线长度控制

### 2.1.1 信号完整性的概念与影响

信号完整性(Signal Integrity,SI)是指在高速电路设计中,电路的信号保持其原始特性和准确传输的能力。在FPGA设计中,信号完整性是确保设计功能正确性和性能稳定性的关键因素。信号完整性问题通常包括反射、串扰、电源噪声和地线干扰等。

影响信号完整性的因素包括但不限于:

- 信号的上升/下降时间

- 布线的特性阻抗

- 信号路径的阻抗匹配

- 布线长度与传输线的类型

- 电源和地线的设计质量

- 元件的布局与布线

当FPGA中的高速信号在传输路径中遇到阻抗不连续点时,会发生反射,这会降低信号的质量并可能导致错误。因此,信号完整性分析和优化是FPGA布线设计的一个重要方面。

### 2.1.2 布线长度对性能的影响分析

在FPGA布线设计中,信号路径的长度直接影响信号的传输时间,从而影响到整个系统的性能和时序。对于高速信号来说,保持信号路径长度的一致性可以减小时钟偏斜(Clock Skew),这对于同步系统尤为重要。

布线长度控制的原则包括:

- 对于时钟信号,应使用专用的全局或半全局时钟网络来实现低偏斜的布局。

- 高速信号布线应尽量短,避免不必要的长线。

- 使用蛇形布线(Serpentine Routing)时,需要考虑信号的最小脉冲宽度以避免信号失真。

- 长布线应尽量采用阻抗匹配的方法来减小反射。

信号路径的长度和布局还受到FPGA芯片的物理限制,例如芯片内部资源的分布和可用的布线通道。设计者必须仔细规划,以确保信号路径满足时间要求,并实现良好的信号完整性。

## 2.2 FPGA的逻辑资源与布线资源

### 2.2.1 FPGA内部逻辑资源的分布

FPGA内部的逻辑资源主要包括查找表(LUTs)、寄存器、专用乘法器、块RAM和DSP等。这些资源的高度集成使得FPGA在实现复杂算法和灵活的信号处理方面非常有优势。

FPGA内部逻辑资源的分布情况如下:

- 查找表是FPGA实现逻辑功能的基本单元。

- 寄存器通常与查找表配合使用,用于存储中间结果。

- 专用乘法器常用于数字信号处理(DSP)等需要大量乘加运算的应用。

- 块RAM和DSP则为存储和运算提供高速的本地资源。

设计者在布局布线时需要考虑这些资源的分布特点,合理安排逻辑模块的位置,以便减少布线长度和延迟,提高整体性能。

### 2.2.2 布线资源的特点及分类

FPGA的布线资源非常丰富,可以根据设计的需要灵活配置。这些布线资源主要分为三种类型:

- 直接布线资源:连接逻辑块和I/O单元之间,传输速度最快,但使用最灵活。

- 互连布线资源:连接不同逻辑块或不同区域的逻辑块,是实现逻辑功能的主要途径。

- 全局布线资源:主要用于时钟、复位和其他全局信号的传输,具有最小的时钟偏斜和延迟。

布线资源的设计和选择对设计的性能有着直接的影响。合理利用FPGA的布线资源,可以显著提高信号传输的速度和稳定性。

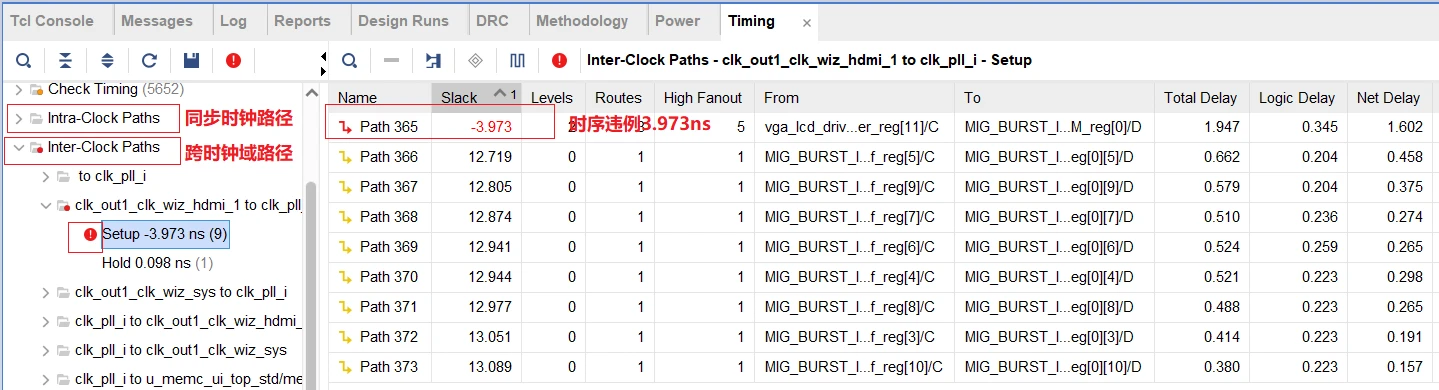

## 2.3 时序闭合与布线策略

### 2.3.1 时序闭合的重要性

时序闭合(Timing Closure)是FPGA设计中的一个关键阶段,指的是在设计中实现所有时序要求的过程。它包括了建立时间(setup time)和保持时间(hold time)的要求,以及针对特定的时钟域所设定的最大延迟时间(Maximum Delay Time)和最小延迟时间(Minimum Delay Time)。

在时序闭合的过程中,设计者需要关注以下几点:

- 确保所有的时序路径满足时序要求。

- 处理好时钟域交叉问题,避免因时钟偏斜造成的数据丢失或读取错误。

- 在布线阶段优化关键信号的路径,达到最小的延迟和波动。

### 2.3.2 实现时序闭合的布线策略

为了实现时序闭合,设计师需要采取一系列的布线策略来优化信号的传输。这些策略包括:

- **优先级布线**:对于关键时序路径优先布线,确保其满足严格的时序要求。

- **全局布线调整**:使用全局布线资源调整时钟和复位信号,确保它们具有最小的偏斜和延迟。

- **利用专用布线**:对于高速或宽总线信号,采用专用布线资源以减少干扰并提高传输效率。

- **优化布线长度**:通过调整逻辑资源布局或布线长度,减少信号的传播延迟。

- **迭代优化**:通过迭代地分析时序报告并修改设计来不断优化时序性能。

布线策略的选择和实施对于达成时序闭合至关重要,正确的布线策略可以显著减少设计的迭代次数,并最终达到预期的性能标准。

以上是对FPGA布线与布局理论部分的深入解析,从信号完整性到时序闭合的多维度展开分析,为后续的布线优化实践和布局优化策略提

0

0