STM32 I2C时钟拉伸应对法

发布时间: 2025-01-05 20:30:02 阅读量: 6 订阅数: 11

# 摘要

本文深入探讨了STM32微控制器中I2C通讯的时钟拉伸机制,包括其理论基础、应用场景、与STM32硬件的交互特性,以及在实际应用中出现的问题、诊断与解决策略。文章详细分析了时钟拉伸如何提高数据传输的可靠性和系统兼容性,同时涵盖了如何配置和编程实现时钟拉伸,以及如何进行测试与优化。此外,本文还探讨了高级I2C通信技术和创新应用场景,展望了STM32 I2C技术的发展趋势及其在低功耗设计和多主通信中的潜在应用。通过本研究,读者可以获得对STM32 I2C通讯深入的了解,并掌握在不同应用场合中时钟拉伸技术的实用知识。

# 关键字

STM32;I2C通讯;时钟拉伸;数据传输可靠性;硬件特性;创新应用

参考资源链接:[总结stm32 的 i2c的缺陷与使用](https://wenku.csdn.net/doc/6401acb8cce7214c316ece30?spm=1055.2635.3001.10343)

# 1. STM32 I2C通讯基础

## STM32 I2C通讯简介

STM32微控制器系列广泛应用于嵌入式系统设计中,而I2C是一种常见的串行通信协议,非常适合于微控制器与各种外围设备之间的连接。STM3C通过其丰富的I2C硬件接口支持这一协议,为开发者提供了高效、低成本的通信方案。

## I2C通讯协议基础

在深入探索I2C通讯细节前,需了解其协议基础。I2C(Inter-Integrated Circuit)是一种多主机的串行总线,支持多设备在同一总线上进行数据传输。它只需要两条线路:一条串行数据线(SDA)和一条串行时钟线(SCL)。I2C的地址机制支持多个从设备连接在同一总线上,而主设备控制数据的传输。

## STM32 I2C硬件接口

STM32的I2C接口支持主设备和从设备模式,能够进行地址识别、数据缓冲、中断和DMA传输等多种功能。通过这些硬件接口,STM32微控制器可以灵活地与外部I2C设备通信,满足各种应用场景的需求。下一章节将详细介绍STM32 I2C接口的时钟拉伸机制,这是确保I2C通信稳定性的关键技术之一。

# 2. I2C时钟拉伸机制

## 2.1 时钟拉伸的理论基础

### 2.1.1 I2C协议时钟拉伸定义

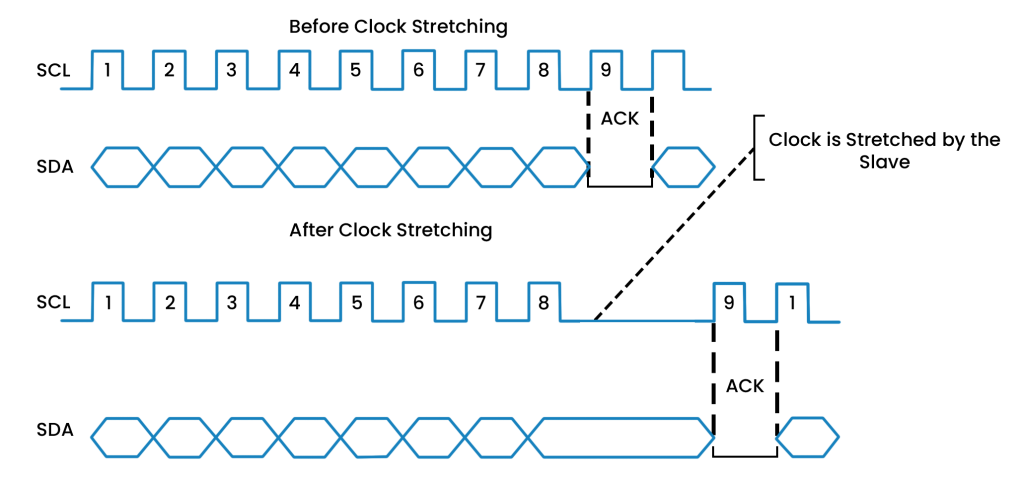

I2C协议中的时钟拉伸(Clock Stretching)是一个重要特性,它允许接收设备通过延长时钟线(SCL)的低电平状态,来控制数据的传输速率。在I2C通信中,主机设备负责产生时钟信号,并使用SCL线来同步数据传输。当从设备无法处理更多的数据或者需要更多时间来处理接收的数据时,它可以拉伸SCL线,暂停数据的传输,直到它准备好继续进行通信。

### 2.1.2 时钟拉伸的工作原理

时钟拉伸的工作原理如下:

1. **从设备检测**: 当从设备检测到主机发送的数据过快,或者它需要更多时间来处理接收到的数据时,从设备将在SCL线上的下一个低电平周期拉伸时钟。

2. **延长低电平**: 在正常的I2C通信中,SCL线会在每个数据字节传输后被释放,从设备在检测到SCL变高后,有机会拉伸时钟。从设备延长SCL线的低电平周期,从而强迫主机等待。

3. **数据处理**: 在从设备拉伸时钟期间,主机被迫等待,直到从设备完成数据处理。

4. **恢复通信**: 一旦从设备准备就绪,它会释放SCL线,允许时钟回到正常状态,主机可以继续发送下一个数据字节。

### 2.2 时钟拉伸的应用场景

#### 2.2.1 提高数据传输可靠性

在高速I2C通信中,从设备处理数据的能力可能成为系统的瓶颈。通过时钟拉伸,从设备可以确保不会因为来不及处理数据而丢失信息。这一机制对于防止数据缓冲区溢出,以及确保数据完整性是非常关键的。

#### 2.2.2 降速处理与系统兼容性

在混合系统中,尤其是不同制造商的设备混合使用时,可能存在时钟频率的差异。时钟拉伸机制可以作为一种降速处理手段,确保所有设备在相同的速率下进行有效通信,增强系统的兼容性。

## 2.3 时钟拉伸与STM32的硬件特性

### 2.3.1 STM32 I2C硬件特性概述

STM32微控制器对I2C协议提供了硬件层面的支持,包括时钟拉伸机制。STM32的I2C硬件模块能够在检测到从设备拉伸时钟时自动暂停数据传输,这允许微控制器与其他设备进行更可靠和高效的数据交互。

### 2.3.2 硬件与时钟拉伸的交互

在硬件层面,STM32的I2C接口在执行数据传输时会持续监视SCL线的状态。一旦检测到SCL线被拉伸,硬件会停止时钟,直到SCL线恢复到未拉伸的状态。这种硬件层面的交互,极大地简化了软件的开发复杂性,使得开发者可以更加专注于应用逻辑的实现。

### 2.3.3 STM32 I2C模块的时钟拉伸配置

STM32 I2C模块的时钟拉伸功能可以在初始化时通过配置相应的寄存器来启用。在配置过程中,开发者需要指定使能时钟拉伸的条件和行为,确保模块能够正确响应从设备的拉伸动作。配置流程通常包括选择适当的时钟速率、设置时钟拉伸的敏感度以及确定时钟释放的条件等。

### 2.3.4 实现软件控制与硬件监测的协同

为了充分实现时钟拉伸的功能,软件控制逻辑必须与硬件监测协同工作。软件需要在数据传输过程中及时检查I2C状态寄存器,判断是否发生了时钟拉伸事件。一旦发现时钟被拉伸,软件逻辑应当采取适当的措施,比如停止当前的传输流程,或者处理其他并行任务,直到硬件信号表明可以恢复数据通信。

## 2.4 时钟拉伸的调试与测试

### 2.4.1 利用硬件调试工具观察时钟拉伸

调试I2C通信时,特别是涉及到时钟拉伸机制时,硬件调试工具如逻辑分析仪和示波器是非常有用的。通过观察SCL和SDA线的状态,可以直观地看到时钟拉伸事件的发生以及其对数据传输的影响。

### 2.4.2 软件工具与调试寄存器的结合使用

除了硬件工具之外,软件开发工具提供的调试寄存器也可以用来监测时钟拉伸事件。开发者可以设置断点,在特定的时钟拉伸事件发生时暂停程序执行,从而分析软件和硬件之间的交互情况。

### 2.4.3 代码逻辑分析与时钟拉伸的关联

代码逻辑分析是调试时钟拉伸机制不可或缺的一部分。开发者需要确保代码逻辑能够正确处理时钟拉伸事件,并且在软件层面上做出适当的响应。这通常涉及到对I2C通信事件的回调函数进行细致的代码审查和测试,以确保没有遗漏任何可能的异常情况。

### 2.4.4 测试案例研究

通过对特定测试案例的研究,开发者可以更好地了解时钟拉伸在不同通信环境下的表现。测试案例可以包括各种数据传输速度、不同长度的数据包、以及不同的I2C设备组合。在每一个测试案例中,时钟拉伸事件的处理情况都应该被记录和分析。

### 2.4.5 性能评估与优化建议

性能评估是确保I2C通信稳定运行的关键步骤。开发者应当使用性能分析工具来量化时钟拉伸对通信性能的影响。基于性能评估的结果,可以提出针对性的优化建议,比如调整时钟速率、优化软件逻辑处理时钟拉伸事件等。

### 2.4.6 解决方案的实施与验证

在分析了时钟拉伸事件并提出优化建议后,开发者需要实施这些解决方案,并进行严格的验证。验证的目的是确保提出的优化措施能够有效地解决时钟拉伸带来的问题,从而提高系统的稳定性和可靠性。

通过上述的分析、测试和验证,开发者可以深入理解I2C时钟拉伸机制,并在实际项目中有效地应用该技术。这不仅提升了系统性能,也为解决复杂通信问题提供了新的思路和手段。

# 3. 时钟拉伸问题诊断与分析

## 3.1 时钟拉伸的常见问题

### 3.1.1 时钟拉伸导致的通信错误

在I2C通讯过程中,时钟拉伸是一种可选的机制,它允许主设备或从设备在数据传输过程中延长时钟信号,从而控制数据传输速率。然而,时钟拉伸的不当使用可能会导致通信错误。这些错误通常表现为总线挂起、数据传输中断或者通信双方的

0

0