深入分析FPGA与QSPI Flash的时序挑战及解决方案:专家级攻略

发布时间: 2025-01-04 15:16:34 阅读量: 9 订阅数: 19

FPGA控制QSPI Flash及Verilog程序.docx

# 摘要

本文深入探讨了FPGA与QSPI Flash的时序挑战和优化设计实践。首先介绍了FPGA与QSPI Flash的基础知识,包括时序理论和基本操作。随后,详细分析了FPGA和QSPI Flash在时序特性方面的差异,探讨了高速接口下的时序挑战和信号完整性问题。文中还提供了一系列优化设计的理论、方法和工具应用,以及硬件设计中的具体时序解决方案。最后,展望了FPGA与QSPI Flash技术的未来发展趋势和应用趋势,为相关领域的研究和实践提供了参考和指导。

# 关键字

FPGA;QSPI Flash;时序分析;时序约束;信号完整性;优化设计

参考资源链接:[Xilinx FPGA控制QSPI Flash读写操作及Verilog程序](https://wenku.csdn.net/doc/460ocxfmhe?spm=1055.2635.3001.10343)

# 1. FPGA与QSPI Flash概述

## 1.1 FPGA简介

现场可编程门阵列(FPGA)是一种用户可编程的集成电子电路,以其可重构性、高性能和灵活性在现代电子系统设计中占据重要地位。FPGA可以实现在硬件层面上编程和配置,这对于快速原型设计和小批量生产具有重大优势。

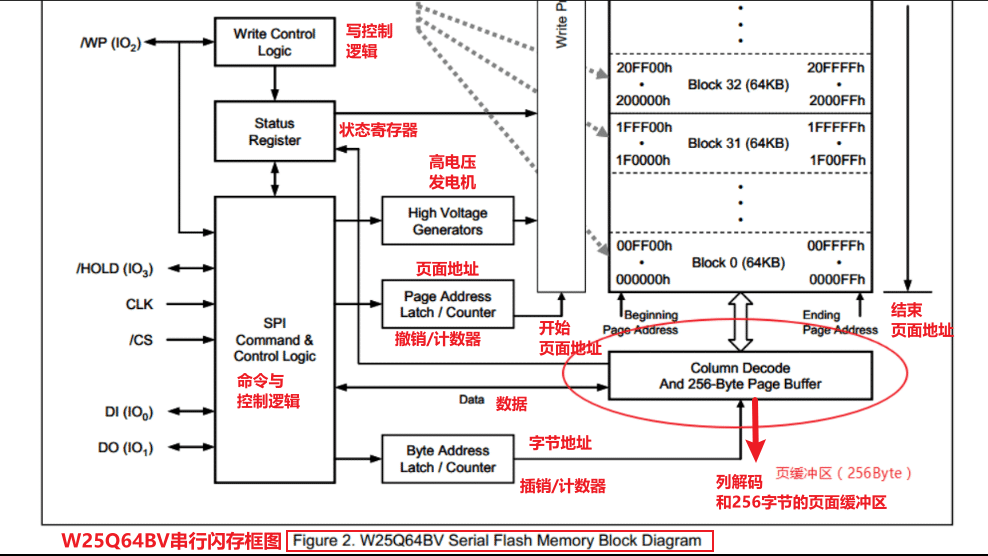

## 1.2 QSPI Flash简介

四次串行外设接口(QSPI)Flash是一种非易失性存储器,广泛用于存储FPGA配置数据。它支持4位宽度的数据传输,比传统的串行外设接口(SPI)在数据传输速率上显著提高,适用于需要高速启动和大数据量存储的应用场景。

## 1.3 FPGA与QSPI Flash的结合

FPGA与QSPI Flash的结合使系统能够快速启动,并在运行时实现动态配置,极大地扩展了FPGA的应用范围。理解二者之间的通信和时序关系,是确保系统稳定性和性能的关键。在接下来的章节中,我们将深入探讨FPGA与QSPI Flash的时序特性、挑战和优化方法。

# 2. FPGA时序基础理论

## 2.1 时序分析的重要性

### 2.1.1 时序的概念与定义

在数字电路设计中,时序(Timing)是指数据和控制信号在集成电路中传播所需要的时间。时序分析是确保数据在正确的时间到达正确的位置的过程,对于FPGA这样的同步数字电路而言,时序是保证系统稳定运行的基础。时序包括了信号的设置时间(setup time)、保持时间(hold time)、时钟到输出时间(clock-to-output time)和传播延迟(propagation delay)等参数。

在FPGA设计中,正确理解时序概念可以预防许多常见的设计问题,如数据竞争(race condition)、时钟偏斜(clock skew)、数据延迟(data delay)等。理解时序也直接影响着最终设计的性能,决定着FPGA能够达到的最大工作频率。

### 2.1.2 FPGA中的时钟域和时钟管理

时钟域是指在数字系统中由同一个时钟信号或相位相差固定的时钟信号控制的电路区域。在FPGA中,不同部分可能运行在不同的时钟域中,这就要求设计者必须正确管理这些时钟域之间的交互。时钟域交叉(CDC)是一个常见的时序问题来源,如果处理不当,很容易导致数据丢失或者数据采样错误。

时钟管理是FPGA设计中的一项关键技术,它涵盖了时钟产生、分配、控制等多个方面。正确的时钟管理策略包括使用全局时钟网络、配置时钟缓冲器(如MMCM和PLL),以及使用时钟门控技术来减少不必要的功耗。时钟管理技术的优劣直接关系到系统的性能、功耗和可靠性。

## 2.2 FPGA时序约束

### 2.2.1 时序约束的基本原则

时序约束是在FPGA设计流程中对时序进行控制和指导的一系列规则,它们定义了设计中数据和时钟信号的路径要求。基本的时序约束包括定义时钟周期、设置输入输出延迟、指定期望的时钟频率等。通过时序约束,可以指导EDA(电子设计自动化)工具进行正确的时序分析和优化,确保在FPGA运行时满足所有的时序要求。

在进行时序约束时,工程师需要根据设计需求和硬件特性来确定约束参数,这是确保设计可靠性和性能的关键步骤。一个合理的时序约束不仅能提升设计的成功率,还能为后期的设计迭代和优化留下足够的空间。

### 2.2.2 SDC约束命令详解

SDC(Synopsys Design Constraints)是一种广泛使用的时序约束文件格式,它被多数EDA工具支持,用来描述设计的时序要求。SDC文件包含了多种命令,如create_clock、set_input_delay、set_output_delay、set_max_delay、set_min_delay等,用来定义时钟、设置输入输出延迟、限定路径的最大最小延迟等。

一个典型的SDC约束文件可能包含以下内容:

```tcl

# 定义时钟信号

create_clock -name {clk} -period 10.000 -waveform { 0.000 5.000 } [get_ports {clk}]

# 设置输入延迟约束

set_input_delay -clock clk -max 2.0 [get_ports {data_in}]

# 设置输出延迟约束

set_output_delay -clock clk -max 3.0 [get_ports {data_out}]

# 限定路径的最小延迟

set_min_delay -from [get_ports {data_in}] -to [get_ports {data_out}] 1.0

```

在应用上述命令时,工程师需要确保这些约束符合硬件的实际性能和设计的时序要求。SDC约束文件是后期时序分析和验证的重要参考,因此其准确性和完整性对整个设计至关重要。

## 2.3 时序仿真与分析工具

### 2.3.1 静态时序分析工具介绍

静态时序分析(Static Timing Analysis,STA)是一种用于验证电路时序的方法,不需要实际运行电路就可以分析电路的时序性能。STA工具可以在设计的早期发现潜在的时序问题,并在设计阶段进行时序优化。常用的STA工具有Synopsys的PrimeTime、Cadence的Tempus等。

STA工具的优势在于它能够快速检查电路中所有可能的时序路径,包括最差情况下的路径,以确保设计能够在最坏的条件(如温度变化、电压波动等)下正常工作。STA工具分析出来的结果通常以报告的形式展现,其中包含了详细的数据路径信息、时序违规的摘要和修复建议。

### 2.3.2 动态时序仿真的重要性及实践

与静态时序分析不同,动态时序仿真(Dynamic Timing Simulation)是在实际的激励下对电路进行的仿真,它可以提供更加详细和精确的时序信息。通过动态时序仿真,可以在仿真环境中模拟FPGA内部的逻辑操作和数据流,从而验证设计的功能和性能。

动态时序仿真通常需要使用到特定的仿真软件,例如ModelSim或Vivado Simulator。工程师需要编写测试平台(testbench),提供输入信号激励,并观察输出信号的响应。相比于静态时序分析,动态时序仿真虽然耗时较长,但可以复现真实场景下可能出现的问题,尤其是那些在STA中难以发现的问题。

实现动态时序仿真,需要遵循以下步骤:

1. 准备设计的源代码和测试平台。

2. 将设计加载到仿真环境中。

3. 编译设计和测试平台,确保没有编译错误。

4. 运行仿真,提供时钟和输入信号激励。

5. 监测输出信号,记录仿真结果。

6. 分析数据,检查是否存在时序错误或功能异常。

下表展示了动态时序仿真在测试阶段所起到的关键作用:

| 动态时序仿真作用 | 描述 |

| --- | --- |

| 功能验证 | 确保设计按预期工作 |

| 时序验证 | 检测时序违规和数据丢失问题 |

| 性能评估 | 评估在不同条件下的性能表现 |

| 调试 | 辅助定位和修正设计错误 |

通过上述的分析和步骤说明,我们可以了解到时序分析和仿真在FPGA设计中的重要性和实施方法。后续章节将继续深入探讨时序问题的解决策略和优化设计实践。

# 3. QSPI Flash时序原理

## 3.1 QSPI Flash的基本操作

### 3.1.1 QSPI接口标准与工作模式

在FPGA系统中,QSPI(Quad SPI)Flash是一种常用的非易失性存储器,它支持四路数据线进行并行读写操作,从而提高数据传输速率。理解QSPI接口的标准和工作模式对于设计高性能的FPGA系统至关重要。

QSPI接口支持四种工作模式:单线(Single I/O)、双线(Dual I/O)、四线(Quad I/O)和命令模式。这些模式在不同的操作中发挥作用,为系统提供灵活的数据传输方式。例如,在读取操作中,通常使用四线模式以达到最快的数据传输速率;而在擦除和写入操作中,可能使用单线模式以减少功耗。

**代码块 3.1.1-1:查看QSPI Flash的模式信息**

```shell

# 以Spansion QSPI Flash为例,使用命令来查询其工作模式

flashrom -p buspirate_spi:dev=/dev/ttyUSB0 --read-eeprom dump.eeprom

```

0

0