【APB I2C编程实战指南】:代码解析与调试技术大公开

发布时间: 2024-12-26 23:35:41 阅读量: 9 订阅数: 19

dw_apb_i2c_databook_dw_apb_dw_apb_i2c_databook_DW_apb_i2c代码_i2cd

# 摘要

APB I2C协议作为嵌入式系统中广泛使用的一种串行通信协议,因其简单、高效的特点,已成为系统中组件互连的关键技术。本文从APB I2C协议的基础概念开始,深入探讨了其硬件接口配置、基本通信流程、高级通信技术,并通过编程实践及调试故障排除,为开发者提供了全面的指导。通过对APB I2C协议的细致分析,本文旨在帮助工程师更好地理解并应用该技术,确保在设计、编程和维护嵌入式系统时能有效利用I2C通信功能,同时解决实际开发中可能遇到的问题。

# 关键字

APB I2C协议;硬件接口;通信流程;高级技术;编程实践;故障排除

参考资源链接:[DesignWare DW_APB_I2C 数据手册 v1.15a](https://wenku.csdn.net/doc/110ntotora?spm=1055.2635.3001.10343)

# 1. APB I2C协议概述

## 1.1 I2C技术起源和发展

I2C(Inter-Integrated Circuit)总线技术最初由荷兰半导体公司 Philips(现在是 NXP Semiconductors 的一部分)在1980年代开发。作为一种串行通信协议,I2C主要设计用于连接低速外围设备到主板芯片组、嵌入式系统或者手机内的集成电路。由于其简单性和扩展性,I2C已被广泛应用于各种电子设备中,成为一种被广泛认可的行业标准。

## 1.2 APB I2C在系统中的作用

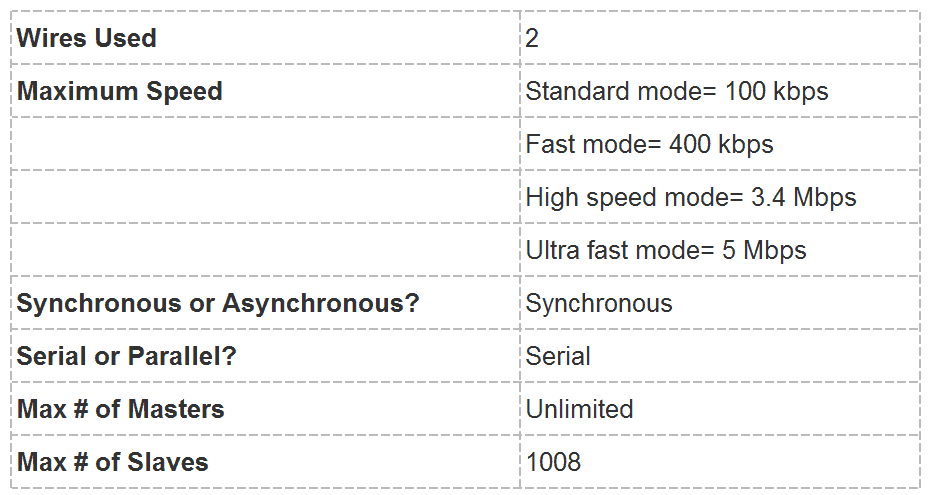

在高级性能总线(Advanced Peripheral Bus,APB)环境中,I2C是一种双线串行通信协议,允许通过两条线(一条数据线SDA,一条时钟线SCL)实现多主机和多从机设备之间的通信。APB I2C特别适用于微控制器和外围设备之间的低速数据交换,如温度传感器、EEPROM、ADC、DAC、LCD显示屏等。

## 1.3 APB I2C协议的特点和优势

APB I2C协议的主要特点包括多主机能力、设备地址识别、广播和多主机广播功能、随机数据读取以及握手和时钟伸缩机制等。其优势在于硬件实现简单,通信线路少,成本低,以及可以支持多设备连接。这样的特性使得APB I2C非常适应于SoC(System on Chip)内部的通信和一些外围设备之间的连接,大大简化了硬件设计的复杂性。

# 2. APB I2C硬件接口和配置

## 2.1 APB I2C硬件连接方式

APB (Advanced Peripheral Bus) I2C 是一种串行通信接口,广泛用于微控制器和各种外围设备之间的低速通信。为了实现I2C通信,需要在硬件上设置一套特定的连接方式。硬件连接包括以下几个关键部分:

- **主机(Master)**:通常情况下,一个I2C系统中有一个主机,负责发起通信并控制数据流。

- **从机(Slave)**:一个或多个从机可以响应主机的请求,进行数据交换。

- **SCL (Serial Clock Line)**:时钟线,用于同步主机和从机之间数据的传输。

- **SDA (Serial Data Line)**:数据线,用于传输实际数据。

在进行硬件连接时,SDA和SCL线需要通过上拉电阻连接到正电源。在系统中,每个从机都会有一个唯一的地址,用于主机识别和通信。APB I2C通信中,通常还会包括一个总线仲裁机制,以解决多个主机同时尝试通信时的冲突问题。

硬件连接方式直接影响通信的稳定性和速度。在设计电路时,应考虑以下因素:

- **线路长度**:过长的线路可能导致信号失真,增加噪声敏感度。

- **信号完整性**:确保所有的连接没有异常的电容和电感负载,这可能影响信号的质量。

- **上拉电阻的选择**:太大的上拉电阻可能导致信号上升沿变慢,而太小的电阻可能会导致功耗增加。

## 2.2 APB I2C接口的电气特性

APB I2C接口具有以下电气特性,这些特性对于接口的可靠性和兼容性至关重要:

- **逻辑电平**:I2C的逻辑电平通常为TTL电平。高电平电压通常在0.7 x VDD以上,而低电平电压则在0.3 x VDD以下。

- **输入电平**:输入电平可以兼容TTL和CMOS电平,这允许不同类型的逻辑电路可以轻松地互相连接。

- **时钟频率**:I2C标准支持最高100kHz(标准模式)和400kHz(快速模式)的数据传输率,更高级的版本支持高达3.4MHz的速率。

- **上拉电阻**:为了保证SDA和SCL线路在空闲状态时为高电平,需要外接适当的上拉电阻。

在设计时,需要确保电路板布局充分考虑了信号完整性,避免高速信号传输中的干扰。例如,避免在SCL和SDA线路上布设高速信号线、强噪声源和敏感器件,从而避免潜在的交叉干扰。

## 2.3 APB I2C配置参数详解

在配置APB I2C硬件接口时,需要详细设置一系列参数来确保设备按照预期工作。以下是配置过程中的一些关键参数:

- **时钟频率**:I2C设备支持的时钟频率可以是标准模式(100kHz),快速模式(400kHz)或高速模式(3.4MHz)。必须选择合适的频率以符合系统需求。

- **地址模式**:I2C设备可以配置为7位地址模式或10位地址模式。根据所连接的外围设备的不同,选择合适的地址模式。

- **时钟极性和相位**:I2C总线允许设置时钟信号的极性和相位,以适应不同厂商的I2C设备。

- **总线仲裁和时钟伸缩**:为了支持多主机配置,需要启用总线仲裁功能,并配置时钟伸缩选项以同步不同速度的主机。

```mermaid

flowchart LR

A[选择时钟频率] --> B[设置地址模式]

B --> C[配置时钟极性和相位]

C --> D[启用总线仲裁]

D --> E[设置时钟伸缩]

```

配置参数时,通常需要操作一组寄存器来实现。例如,在某些微控制器中,可以通过设置I2C 控制寄存器(I2Cx_CR1)来配置这些参数。下面是一个示例代码块,展示了如何设置时钟频率为400kHz的快速模式:

```c

I2C1->CR1 |= I2C_CR1_PE; // 使能I2C

I2C1->CR1 |= I2C_CR1_ACK; // 启用应答

I2C1->CCR = 0x03; // 设置时钟控制寄存器为快速模式

I2C1->TRISE = 0x03; // 设置I2C预增时钟频率

```

以上代码中,`I2C1->CR1`访问了I2C控制寄存器,`PE`位用来开启I2C设备,`ACK`位用来启用应答信号。`CCR`寄存器用来设置时钟频率,而`TRISE`寄存器设置预增时钟以满足快速模式下的时序要求。每个参数的具体设置需要根据I2C设备的数据手册来确定,以确保设备能够正常工作。

在配置完这些参数后,还需要确保I2C总线上的所有设备都兼容这些设置,以避免通信失败。最终,通过仔细配置I2C接口,可以确保设备以最优化的方式工作,实现高速且稳定的通信。

# 3. APB I2C基本通信流程

在APB I2C协议中,基本通信流程是确保设备间有效数据交换的关键。为了深入理解,我们将详细探讨I2C设备地址和数据传输规则、主机发送和接收数据的基本流程、以及从机响应机制和时序要求。

## 3.1 I2C设备地址和数据传输规则

### 3.1.1 设备地址格式

I2C设备地址通常是7位的,有些设备还支持10位的扩展地址格式。地址的选择和分配对于避免地址冲突至关重要。

### 3.1.2 数据传输规则

数据传输规则遵循特定的起始条件、地址发送、读/写位设置、应答位的检查等。这些规则保证了数据在主机和从机之间能够可靠地传输。

### 3.1.3 数据包的组成

一个数据包通常包含起始条件、设备地址、读/写位、数据字节和停止条件。理解每个部分的功能对于设计稳定的通信协议至关重要。

## 3.2 主机发送和接收数据的基本流程

### 3.2.1 主机发送数据流程

以下是主机发送数据时遵循的步骤:

1. 生成起始条件。

2. 发送设备地址和写位。

3. 等待从机的应答信号。

4. 发送数据字节。

5. 检查应答信号,确认数据成功传输。

6. 生成停止条件。

### 3.2.2 主机接收数据流程

主机接收数据的流程稍微复杂一些,包括:

1. 生成起始条件。

2. 发送设备地址和读位。

3. 等待从机的应答信号。

4. 从从机接收数据字节。

5. 发送应答位或非应答位。

6. 重复步骤4和5,直到数据接收完毕。

7. 生成停止条件。

## 3.3 从机响应机制和时序要求

### 3.3.1 从机响应机制

从机通过发送应答信号来确认接收到主机的信息。如果从机检测到自己的地址,它将拉低数据线以发送应答。

### 3.3.2 时序要求

I2C通信中的时序要求非常严格,包括时钟周期(SCL频率)、数据稳定时间(tsuDAT)、数据建立时间(thDAT)等参数。这些时序要求确保了数据的准确性和协议的兼容性。

### 3.3.3 时序分析实例

假设一个典型的I2C总线配置是:

- SCL频率:100 kHz

- tsuDAT最小值:250 ns

- thDAT最小值:0 ns

```markdown

| Parameter | Min | Max | Unit |

|-----------|-----|-----|------|

| tsuDAT | 250 | - | ns |

| thDAT | 0 | - | ns |

```

从机必须在SCL的高电平周期内保持数据稳定,以确保主机能够正确读取数据。

### 3.3.4 从机时序的mermaid流程图

```mermaid

graph LR

A[Start Condition] --> B[Send Address + R/W]

B --> C[Check ACK]

C -->|ACK| D[Send Data]

D --> E[Check ACK]

E -->|ACK| F[Stop Condition]

C -->|NACK| G[Resend Address + R/W]

E -->|NACK| H[Resend Data]

```

在上述流程中,如果从机没有检测到应答信号,它将认为传输失败,并且需要重新开始流程。

### 3.3.5 主机控制逻辑代码示例

```c

void I2C_MasterSendData(uint8_t deviceAddress, uint8_t *data, uint8_t numBytes) {

// S

```

0

0