【硬件加速库详解】:Orin平台CUDA与cuDNN实战应用

发布时间: 2024-12-15 08:25:31 阅读量: 10 订阅数: 9

参考资源链接:[英伟达Jetson AGX Orin系列手册与性能详解](https://wenku.csdn.net/doc/2sn46a60ug?spm=1055.2635.3001.10343)

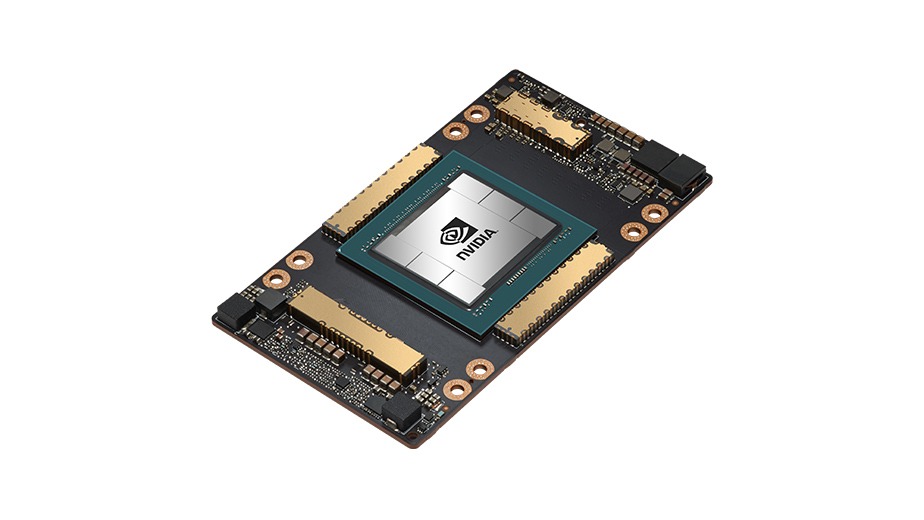

# 1. 硬件加速库与Orin平台概述

在人工智能领域,硬件加速技术是实现快速计算的核心。随着深度学习模型的复杂度增加,高效处理海量数据的需求促使硬件加速库成为技术发展的热点。NVIDIA的Orin平台,搭载了先进的CUDA和cuDNN加速库,为开发者提供了在边缘计算设备上部署深度学习应用的强大支持。

Orin平台整合了CPU、GPU、AI处理器等多种计算资源,使其能够有效处理复杂的并行计算任务。在本章,我们将简要探讨硬件加速库的基本概念,以及Orin平台的基础架构,为进一步深入CUDA和cuDNN的细节打下坚实的基础。随后的章节会详细解析CUDA的基础理论、cuDNN的高级功能,以及Orin平台在实际应用中的优化策略和案例分析。通过这些内容,我们可以理解如何利用硬件加速库来提高深度学习模型的效率和性能。

# 2. ```

# 第二章:CUDA基础理论与实践

在当今的高性能计算领域,使用图形处理单元(GPU)进行通用计算已成为加速应用程序的首选方法。NVIDIA的CUDA(Compute Unified Device Architecture)是一种并行计算平台和编程模型,它允许开发者利用NVIDIA的GPU进行计算任务。本章将探讨CUDA的基础理论,并介绍其在实践中的应用。

## 2.1 CUDA架构概述

### 2.1.1 CUDA的计算模型

CUDA提供了直接控制GPU硬件的接口,其核心是通过大规模并行处理来解决复杂的计算问题。CUDA计算模型将任务分解为多个线程(thread),这些线程会被进一步组织成块(block),然后这些块被分配到GPU的多个流处理器(streaming multiprocessors, SMs)上执行。

每块中的线程可以进行同步,而不同块之间则无法直接同步。这是因为在GPU内部,每个SM可以运行多个线程块,但块内的线程可以共享资源,如共享内存和同步原语(如barrier),块间则不能。

### 2.1.2 GPU与CPU的协同工作原理

在CUDA的架构中,CPU依然作为主机(host)执行程序的主线程,并控制与管理设备(device),即GPU。CPU与GPU之间的数据传输是通过PCI Express总线进行的,而GPU完成计算任务后,CPU负责收集结果。

在实际应用中,CPU会将需要大规模并行计算的数据发送到GPU的全局内存,然后启动核函数(kernel)在GPU上执行。核函数在GPU执行完毕后,CPU会将结果从GPU内存中取回,以进行下一步处理。

## 2.2 CUDA编程模型

### 2.2.1 核函数(Kernels)和线程层次结构

核函数是CUDA中执行并行计算的基本单位。开发者编写核函数,然后由主机端代码通过CUDA运行时API启动,指定网格(grid)和块(block)的大小。

CUDA中的线程层次结构如下所示:

- 线程(Thread):执行核函数的最基本单位。

- 块(Block):一组线程的集合,共享内存和执行配置。

- 网格(Grid):一个或多个块的集合,整个核函数在执行时被组织为一个网格。

每个线程都有一个唯一的索引,它可以在核函数内部通过内置变量`threadIdx`、`blockIdx`和`blockDim`来获得。

### 2.2.2 内存模型和数据传输

CUDA提供了多种内存类型,包括全局内存、常量内存、共享内存、纹理内存和本地内存。这些内存类型具有不同的访问速度和用途,开发者需要根据计算需要选择合适的内存类型。

- 全局内存:在所有线程之间共享,容量最大,但访问速度较慢。

- 常量内存:由所有线程读取,读取速度快,常用于存储只读数据。

- 共享内存:块内的线程可读写共享内存,访问速度很快,但空间有限。

- 纹理内存:用于读取纹理数据,适用于图像处理中的缓存。

- 本地内存:每个线程私有的,用于存储局部变量,访问速度慢于共享内存。

核函数中的数据传输需要通过主机内存和设备内存进行。开发者需要使用CUDA API显式地进行内存分配、复制和释放操作。

## 2.3 CUDA性能优化技巧

### 2.3.1 并行计算的最佳实践

要优化CUDA程序的性能,首先需要保证充分的并行度。这意味着核函数中尽可能多的线程能够同时运行,而不是闲置等待。此外,通过最小化全局内存访问以及使用高速内存(如共享内存)来减少延迟,可以提升性能。

- 并行度:确保每个SM上尽可能有多个活动线程块。

- 内存访问:优化内存访问模式,避免内存访问冲突。

- 指令并行:利用GPU的指令级并行性,避免执行单元的空闲。

### 2.3.2 内存访问模式和带宽优化

CUDA内存优化的关键在于减少全局内存的访问次数以及访问对齐。全局内存访问的优化策略包括合并内存访问(coalesced memory accesses),这是指尽量让一个线程块内的线程连续地访问内存。

带宽优化需注意以下几点:

- 减少全局内存访问的次数,优化算法减少不必要的数据读取。

- 利用共享内存作为线程块内的缓存,减少对全局内存的访问。

- 使用异步内存传输函数(如`cudaMemcpyAsync`),将内存传输和计算重叠执行,以隐藏内存传输的延迟。

最佳实践包括:

- 使用常量内存和纹理内存代替全局内存,以提升缓存命中率。

- 利用并发内核执行和流来重叠计算和内存传输。

下面的代码块展示了如何在CUDA中声明核函数以及优化内存访问:

```c

// CUDA核函数示例

__global__ void vectorAdd(float *A, float *B, float *C, int numElements)

{

int i = blockDim.x * blockIdx.x + threadIdx.x;

if (i < numElements)

{

C[i] = A[i] + B[i];

}

}

// CUDA内存传输和核函数调用

float *A, *B, *C;

size_t size = numElements * sizeof(float);

// 分配主机内存并初始化数据

A = (float *)malloc(size);

B = (float *)malloc(size);

C = (float *)malloc(size);

// 分配设备内存

float *d_A, *d_B, *d_C;

cudaMalloc((void **)&d_A, size);

cudaMalloc((void **)&d_B, size);

cudaMalloc((void **)&d_C, size);

// 将数据从主机复制到设备

cudaMemcpy(d_A, A, size, cudaMemcpyHostToDevice);

cudaMemcpy(d_B, B, size, cudaMemcpyHostToDevice);

// 设置执行配置,并启动核函数

dim3 blockSize(256);

dim3 gridSize((numElements + blockSize.x - 1) / blockSize.x);

vectorAdd<<<gridSize, blockSize>>>(d_A, d_B, d_C, numElements);

// 将结果从设备复制回主机

cudaMemcpy(C, d_C, size, cudaMemcpyDeviceToHost);

// 释放设备和主机内存

cudaFree(d_A);

cudaFree(d_B);

cudaFree(d_C);

free(A);

free(B);

free(C);

```

在上述代码中,`vectorAdd`是一个简单的向量加法核函数。通过核函数的声明,指明了其在GPU上执行的并行计算过程。在实际调用过程中,我们设置了执行配置(即block和grid的大小),然后启动核函数。此外,注意到了主机和设备内存之间的数据传输,以及如何在执行完核函数之后将结果传回主机内存。这个简单的例子体现了CUDA编程模型中的核心概念,为理解更复杂的CUDA应用打下了基础。

# 3. cuDNN深度学习加速库详解

## 3.1 cuDNN库概述

### 3.1.1 cuDNN的功能和优势

cuDNN(CUDA Deep Neural Network library)是NVIDIA推出的用于深度神经网络计算的加速库,它以CUDA为基础,为深度学习框架提供了核心的优化算法。cuDNN的设计目的是为了提供高性能的深度学习操作,包括卷积、池化、归一化和激活函数等。cuDNN通过利用GPU的高吞吐量和并行处理能力,显著加快了神经网络的训练和推理速度。

cuDNN的优势在于其高性能和易用性。库内的算法经过优化,能够实现比纯CUDA代码更高效的运行。cuDNN通过提供低级别的API来优化各种深度学习任务,同时又足够抽象,使得开发者可以专注于网络结构的设计,而不必从头开始实现复杂的算法。这大大降低了深度学习框架的开发难度,并加速了框架的开发进程。

### 3.1.2 cuDNN与CUDA的关系

cuDNN可以被视为CUDA的补充,专门为深度学习工作负载提供支持。虽然CUDA提供了底层的硬件抽象和执行模型,但cuDNN提供了更高层次的、深度优化的神经网络操作。cuDNN在CUDA的基础上构建,利用CUDA提供的硬件资源和底层API,实现了高效的深度学习计算。

具体来说,cuDNN利用CUDA的线程管理、内存管理等机制,针对性地对深度学习中的常见操作进行优化,比如高效的数据传输、张量运算等。此外,cuDNN还针对不同版本的GPU进行了针对性优化,这意味着开发者可以根据自己的GPU型号选择最合适的cuDNN版本,以达到最佳性能。

## 3.2 cuDNN的核心API与实践

### 3.2.1 Tensor核心操作API

cuDNN的Tensor核心操作API是围绕着神经网络中基础数据结构——张量的操作。张量操作API允许开发者进行高效的张量转换、张量数据填充、以及高效的张量数学运算等。这些操作是深度学习计算中的基础,而cuDNN通过底层优化,使得这些操作在GPU上运行得更加快速和高效。

在cuDNN中,张量操作通常会涉及到`cudnnTensorDescriptor_t`类型的定义,该类型描述了一个张量的属性,包括数据类型、形状和内存布局。例如,定义一个4维张量描述符的代码如下:

```c

cudnnTensorDescriptor_t tensorDesc;

cudnnCreateTensorDescriptor(&tensorDesc);

cudnnSetTensor4dDescriptor(tensorDesc,

CUDNN_TENSOR_NCHW, // 数据布局为NCHW

CUDNN_DATA_FLOAT, // 数据类型为float

n, // 批次大小

c, // 通道数

h, // 高度

w); // 宽度

```

这段代码定义了一个描述符,指定了张量的布局为NCHW(批次、通道、高度、宽度),数据类型为单精度浮点数(float)。这种描述符在后续的API调用中用于描述操作所涉及的张量。

### 3.2.2 卷积核心操作API

卷积操作是深度学习中最为核心和计算密集的操作之一。cuDNN提供了专门的API来优化卷积操作,包括了各种不同类型的卷积(例如标准卷积、分组卷积和深度可分离卷积)以及不同的前向和后向传播算法。

cuDNN的卷积核心操作API需要设置多个描述符来精确定义卷积计算的细节。例如,使用cuDNN进行前向卷积操作通常需要设置卷积描述符`cudnnConvolutionDescriptor_t`、算法描述符`cudnnConvolutionFwdAlgo_t`和工作空间`void* workSpace`。以下是一个卷积前向传播的代码示例:

```c

cudnnConvolutionDescriptor_t convDesc;

cudnnCreateConvolutionDescriptor(&convDesc);

cudnnSetConvolution2dDescriptor(convDesc,

padding, // 上下填充

padding, // 左右填充

stride, // 步长

stride, // 步长

dilation, // 扩张

0

0