CMOS放大器设计从概念到产品的全攻略:Cadence实战技巧大公开

发布时间: 2025-01-10 10:13:57 阅读量: 5 订阅数: 9

利用Cadence工具设计COMS低噪声放大器

# 摘要

本文详细介绍了CMOS放大器的设计过程,涵盖了从理论基础到实践技巧的各个方面。首先概述了CMOS放大器的设计概念,随后深入探讨了放大器的基本工作原理、分类和特性。文章重点论述了CMOS技术在放大器设计中的应用,包括电路模型和噪声分析及其优化策略。此外,还提供了在Cadence环境中进行电路设计、仿真分析、版图设计和信号完整性分析的实战技巧。最后,本文讨论了CMOS放大器测试与验证的方法,以及设计中可能遇到的挑战和未来的发展趋势。

# 关键字

CMOS放大器;电路仿真;版图设计;信号完整性;噪声分析;性能测试

参考资源链接:[Cadence助力2.4GHz CMOS低噪放大器设计:实战教程与3dB噪声优化](https://wenku.csdn.net/doc/6401ac15cce7214c316ea915?spm=1055.2635.3001.10343)

# 1. CMOS放大器设计概述

CMOS放大器是集成电路设计中的核心组件之一,广泛应用于各类电子设备中,从便携式音乐播放器到高性能计算机。设计CMOS放大器不仅需要深厚的理论基础,还需要实践中的丰富经验。本章将概述CMOS放大器设计的整体流程,为读者提供一个清晰的设计路线图,并为后续章节深入讨论CMOS放大器的理论基础、设计实践、仿真技巧以及测试与验证等方面奠定基础。

在开始设计之前,我们首先需要了解CMOS放大器的基本功能和它在电子系统中的作用。CMOS放大器能够根据输入信号的幅度,输出相应比例放大的信号。这种能力使它成为信号处理中不可或缺的部分。随后,我们将讨论CMOS技术的优势,如低功耗、高集成度等,这些特性使得CMOS放大器在现代电子设计中占据主导地位。此外,本章还将简要介绍放大器设计的复杂性和挑战,为后续章节做好铺垫。

# 2. CMOS放大器理论基础

## 2.1 放大器的基本概念

### 2.1.1 放大器的工作原理

放大器的工作原理基于利用晶体管或其他电子元件的非线性特性,将输入信号的幅度进行增强。在CMOS放大器中,晶体管作为主要的放大元件,通常工作在非饱和区的线性放大区。通过调整晶体管的工作点(静态工作点),可以设置放大器的放大倍数和线性范围。

以NMOS晶体管为例,其漏极电流(Id)与栅极电压(Vg)之间的关系通常在亚阈值区和饱和区是非线性的,但在三角形区是一个近似线性关系,这个线性区域被用于放大器的设计。当在栅极施加一个小的交流信号时,漏极电流会随之线性变化,从而在负载电阻上产生一个放大的交流电压信号。

放大器根据其频率响应可以分为低通放大器、带通放大器、高通放大器等,根据其功能又可以分为电压放大器、电流放大器、功率放大器等。

### 2.1.2 放大器的分类和特性

放大器按照不同的标准可以分为不同的类型。根据其输入和输出的关系,可以分为电压放大器、电流放大器和功率放大器。根据其功能,可以分为运算放大器、缓冲放大器等。根据其应用频段,可以分为低频放大器、高频放大器。

放大器的主要性能参数包括增益、带宽、输入输出阻抗、噪声系数、线性度、失真度等。增益指的是放大器对信号幅度的放大倍数,带宽决定了放大器可以有效放大的频率范围,输入输出阻抗影响着放大器的信号传输特性和与前后级电路的匹配。噪声系数描述了放大器引入噪声的程度,线性度和失真度则与信号失真的程度相关。

放大器的分类和特性是理解和设计放大器不可或缺的基础知识,它们决定了放大器是否适用于特定的应用场景。

## 2.2 CMOS放大器设计理论

### 2.2.1 CMOS技术的特点

CMOS(互补金属氧化物半导体)技术是一种广泛应用于集成电路设计中的技术。CMOS技术最显著的特点是低功耗、高输入阻抗、优秀的噪声性能、以及能够提供对称的N沟道和P沟道晶体管。这些特性使得CMOS放大器在许多应用场合都成为理想选择,尤其是在便携式设备和大规模集成电路中。

低功耗是CMOS技术的另一个重要优势,因为静态电流非常小,晶体管仅在开关状态时才会消耗显著的电流。高输入阻抗意味着CMOS放大器对输入信号源的影响小,能够有效地放大高阻抗源的信号。此外,CMOS放大器通常具有较低的噪声性能,这是由于其采用的晶体管结构和工作方式决定的。

### 2.2.2 CMOS放大器的电路模型

CMOS放大器的电路模型通常包括晶体管、偏置电路、负载元件和反馈网络。晶体管是实现信号放大的核心,偏置电路确保晶体管工作在适当的静态工作点。负载元件通常决定放大器的输出阻抗和增益,而反馈网络则用于稳定放大器的工作状态和调整放大器的频率响应。

CMOS放大器的电路模型可以进一步细化为差分对输入的电路模型、共源放大器模型、共栅放大器模型和共漏放大器模型等。每个模型具有不同的特点和应用,比如差分对输入模型可以提供良好的共模抑制比,而共源放大器模型具有较高的电压增益。

### 2.2.3 噪声分析与优化策略

噪声是放大器设计中的一个重要考虑因素。CMOS放大器中的噪声主要来源于热噪声、闪烁噪声(1/f噪声)和散粒噪声。热噪声是由电阻中的随机热运动产生的,闪烁噪声与晶体管的载流子复合有关,散粒噪声则与载流子的离散特性有关。

在放大器设计中,通常需要分析这些噪声源对整体放大器性能的影响,并寻找降低噪声的策略。比如,可以通过合理设计偏置电流来减少热噪声,通过优化晶体管尺寸来减小闪烁噪声,或者通过增加并联晶体管数量来减少散粒噪声的影响。

此外,设计时还可以采取对称设计、增加晶体管的宽长比、以及使用差分结构来提高CMOS放大器的噪声性能。通过对噪声源的深入理解以及采取相应的设计优化措施,可以在不影响放大器性能的前提下,尽可能地降低放大器的噪声水平。

在此基础上,我们将在下一章节中详细探讨CMOS放大器设计实践,介绍设计前的准备和参数设置、电路设计步骤以及版图设计技巧。这一系列实践性的内容将为读者提供一个从理论到实际操作的完整学习路径。

# 3. CMOS放大器设计实践

## 3.1 设计前的准备和参数设置

### 3.1.1 确定设计规格和要求

在CMOS放大器的设计开始之前,首先需要明确的设计规格和要求,这将决定后续设计的方向和参数设定。设计规格包括放大器的增益、带宽、输入和输出阻抗、噪声水平以及功耗等。例如,一个音频放大器可能要求增益为20dB至60dB,带宽为20Hz至20kHz,总谐波失真(THD)要求小于0.01%。

在实际操作中,设计要求可能会受到芯片制造工艺、成本预算以及应用环境等因素的限制。确定设计规格和要求后,工程师需要根据这些要求选择合适的CMOS工艺,并考虑电路的整体布局和布线策略,以满足上述技术参数。

### 3.1.2 Cadence环境配置和工具介绍

设计工作开始之前,需要在Cadence环境中配置好所需的工具和库文件。Cadence提供了集成电路设计环境,内含许多设计和仿真工具。例如,使用Cadence Virtuoso进行电路设计、使用Spectre或Hspice进行电路仿真等。

在Cadence Virtuoso中,设计师可以绘制电路图,设计版图,并进行初步的电路仿真。此外,Cadence还提供了用于版图验证和参数提取的工具。配置好Cadence环境后,工程师可以加载所需的工艺库,这包含工艺特定的元件模型和设计规则。

## 3.2 CMOS放大器电路设计步骤

### 3.2.1 初始电路搭建

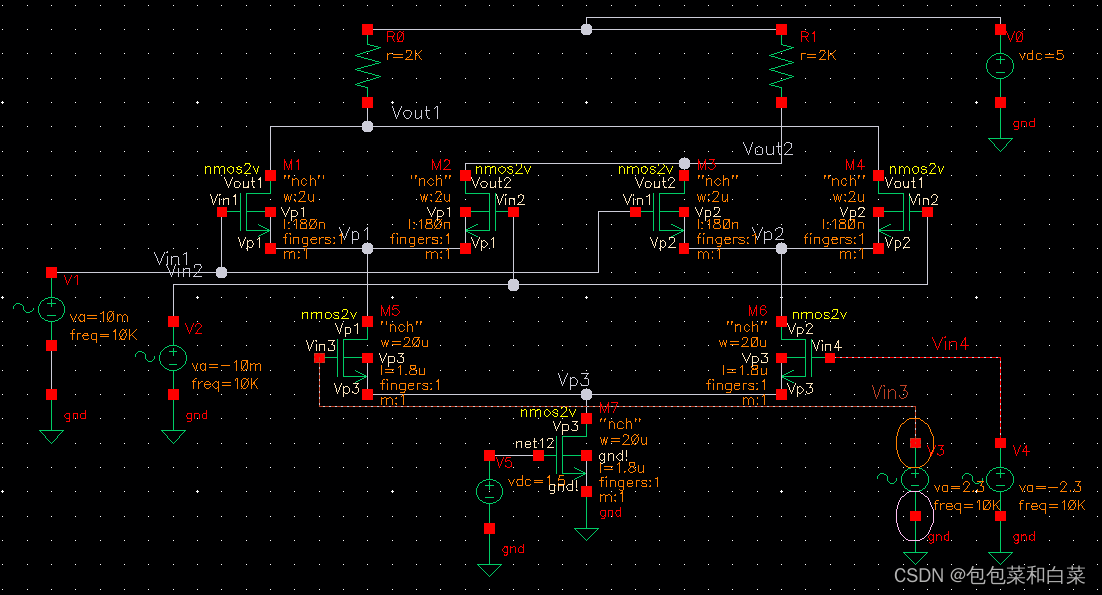

在确定设计要求和环境配置之后,接下来是实际电路的搭建阶段。初始电路搭建是在初步理解需求的基础上,根据放大器理论来构建电路。在这个阶段,设计师会选择合适的晶体管类型和数量,以及决定放大器的拓扑结构。

例如,一个简单的CMOS差分放大器设计通常包括两个N型MOSFET和两个P型MOSFET构成的输入级,以及可能的输出级。在Cadence Virtuoso中,设计师可以使用图形化界面拖放不同的元件,如MOSFET、电阻、电容等,并用线

0

0