CompactPCI Express与传统PCI技术的全面对比分析:优势、局限及未来趋势

发布时间: 2024-12-02 17:59:47 阅读量: 37 订阅数: 19

通信与网络中的CompactPCI Express 混合桥接板设计原理及实现方法

参考资源链接:[CompactPCI ® Express Specification Revision 2.0 ](https://wenku.csdn.net/doc/6401ab98cce7214c316e8cdf?spm=1055.2635.3001.10343)

# 1. CompactPCI Express与传统PCI技术概览

## 1.1 CompactPCI Express与传统PCI技术的兴起

PCI技术在个人电脑领域中历史悠久,随着计算机技术的发展和应用需求的不断变化,CompactPCI Express应运而生。这种技术是对传统PCI技术的改良,旨在提供更高的数据传输速率和更好的系统扩展性。为了深入理解这两项技术,我们首先需要回顾它们的历史发展轨迹。

## 1.2 CompactPCI Express的优势概述

CompactPCI Express相较于传统PCI具有显著的技术优势。其中最为突出的是它支持的高速串行技术,这使得它在数据吞吐量上拥有无可比拟的优势。此外,它的模块化设计提高了系统的灵活性和可维护性,为现代计算机系统提供了更加强大的支持。

## 1.3 传统PCI技术的局限性

尽管传统PCI在历史上扮演了至关重要的角色,但它的并行总线设计和有限的带宽限制了其进一步发展。在现代计算需求下,传统PCI技术很难满足高速和高密度数据传输的要求,这促使了CompactPCI Express等更先进的技术出现。

本章我们仅对CompactPCI Express与传统PCI技术作了简单的对比概览,接下来将深入探讨技术架构和工作原理。

# 2. 技术架构和工作原理

## 2.1 CompactPCI Express的基础架构

### 2.1.1 CompactPCI Express的硬件组成

CompactPCI Express (cPCIe) 是一种针对工业环境而优化的高性能总线技术,它基于PCI Express (PCIe) 技术,同时保持与传统的 CompactPCI (cPCI) 兼容。cPCIe 的硬件组成主要包括以下几个关键部分:

- **背板(Backplane)**: 它是整个系统的基础,提供物理连接和电气接口给各个插槽和模块。cPCIe 背板设计为支持多行插槽,每行插槽都对应一条 PCIe 通道。

- **插槽(Slot)**: 插槽用于安装各种功能板卡,如处理器板、I/O 板等。每块板卡都通过其上的 PCIe 接口与背板相连。

- **功能板卡(Function Card)**: 这些板卡可以是各种功能模块,如以太网卡、SCSI 控制器、图形加速卡等,它们通过 PCIe 总线与系统其他部分通信。

- **管理控制器(Management Controller)**: 管理控制器用于监控和控制整个背板上的模块和资源,它确保系统稳定运行并提供远程管理能力。

接下来,我们通过一个表格来详细了解这些组件的详细信息:

| 组件 | 描述 | 功能 |

|------------|--------------------------------------------------------------|--------------------------------------------------------------|

| 背板 | 提供连接多个板卡的物理和电气接口 | 确保数据传输,提供总线功能 |

| 插槽 | 用于安装和连接功能板卡 | 提供与背板物理连接,支持不同类型的PCIe板卡 |

| 功能板卡 | 各种具备特定功能的扩展卡 | 扩展系统功能,如数据采集、通信、计算等 |

| 管理控制器 | 监控和管理背板上的所有模块和资源 | 确保系统稳定性,支持远程管理 |

### 2.1.2 CompactPCI Express的信号层和传输机制

cPCIe 信号层基于 PCIe 的物理层和数据链路层,并加以扩展以支持更高性能和更严格工业环境的需求。它使用 PCIe 的通道机制进行数据传输,每个通道由一组独立的差分信号线组成。

在 PCIe 中,每个通道由一对差分信号线(发送和接收)组成,这些差分信号线能有效地实现高速数据传输,同时降低外部干扰。PCIe 的传输机制是基于“包”的,每个数据包包含地址、数据和控制信息。

在 CompactPCI Express 中,传输机制也遵循 PCIe 的这一核心概念,但增加了对环境适应性更强的设计。这包括针对工业应用设计的保护措施(如浪涌保护、ESD防护等)和更严格的信号完整性要求。

为了进一步说明这种传输机制,让我们用一个简单的 mermaid 流程图来展示PCIe通道的数据包传输过程:

```mermaid

graph LR

A[应用层产生数据] -->|封装为TLP| B[传输层]

B -->|增加序列号等| C[数据链路层]

C -->|加上CRC校验| D[物理层]

D -->|信号转换| E[物理传输介质]

E -->|信号转换| F[物理层]

F -->|检查CRC校验| G[数据链路层]

G -->|提取数据包| H[传输层]

H -->|解包| I[应用层]

```

这个流程图揭示了从应用层到物理层,再到目标物理层和最终的应用层的过程,展示了一个PCIe通道上的完整数据传输链路。

## 2.2 传统PCI技术的细节剖析

### 2.2.1 传统PCI的硬件与总线特性

传统PCI (Peripheral Component Interconnect) 是一种由Intel公司于1990年代初期开发的局部总线标准。它的设计目标是取代ISA (Industry Standard Architecture) 和EISA (Extended Industry Standard Architecture),为计算机提供更快、更有效的连接方式。

PCI 总线的主要硬件特性包括:

- **统一的地址和数据总线**: PCI 总线使用统一的地址和数据总线,这使得它在传输数据时更加高效。

- **总线仲裁**: PCI 提供了内置的总线仲裁机制,允许在多个主设备之间动态分配总线控制权。

- **即插即用**: PCI 总线支持即插即用 (Plug and Play) 设备,设备可以被动态地添加或移除,而无需重新启动系统。

- **支持多种数据传输模式**: 包括快速、突发、分散和集中式I/O等。

在总线特性方面,PCI 具有以下特点:

- **固定时钟频率**: 早期的 PCI 总线工作在固定的33MHz频率。

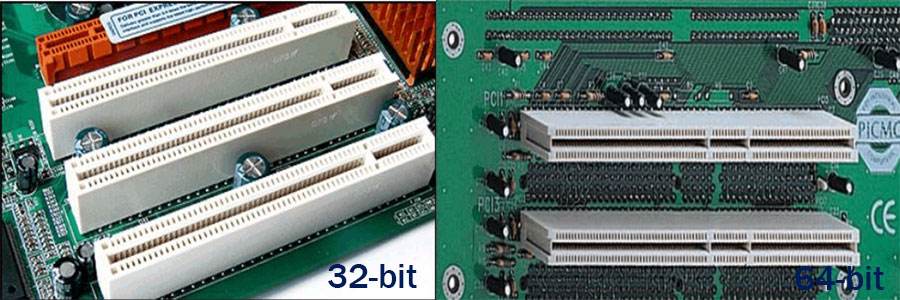

- **多线并行**: 初始版本的PCI总线宽度为32位,后续扩展至64位以提供更大的带宽。

-

0

0