SystemVerilog 3.1a数据流建模:实现高效数据处理逻辑的秘诀

发布时间: 2024-12-17 16:04:33 阅读量: 2 订阅数: 6

SystemVerilog3.1a语言参考手册.chm

参考资源链接:[SystemVerilog 3.1a语言参考手册:PDF中文版详解与特性概览](https://wenku.csdn.net/doc/6412b73bbe7fbd1778d498e8?spm=1055.2635.3001.10343)

# 1. SystemVerilog数据流建模基础

数据流建模是SystemVerilog中一种直观的硬件描述方式,它允许设计者以数据信号的流动来描述硬件行为,从而简化复杂逻辑的设计和验证。本章将带您入门数据流建模,为后续深入学习打下坚实的基础。

## 1.1 数据流建模的基本概念

数据流建模主要依赖于连续赋值语句来描述硬件结构,其中信号间的逻辑关系通过逻辑运算符、位运算符和缩减运算符来表达。这些基本元素共同构成了数据流建模的骨架。

## 1.2 连续赋值语句的重要性

在SystemVerilog中,连续赋值语句(如`assign`语句)是实现数据流建模的关键。它们允许设计者声明信号间的关系,并且这些关系在整个仿真过程中保持有效。

```verilog

assign y = a & b; // 示例:y是a和b的按位与结果

```

通过上述代码,我们定义了一个简单的按位与关系,其中`y`的值总是`a`和`b`的按位与结果。这种持续性的特性是数据流建模的核心优势之一,也是与过程建模的主要区别。

在下一章节中,我们将探讨数据流建模的语法基础,包括连续赋值语句、运算符和表达式,这些都是理解数据流建模至关重要的基础知识。

# 2. ```

# 第二章:数据流建模核心概念

数据流建模是SystemVerilog语言中一种重要的建模方式,它允许设计者描述硬件行为的方式类似于描述数字逻辑电路图。本章节将深入探讨数据流建模的核心概念,包括语法基础、操作符的深入理解,以及数据流建模的高级特性。

## 2.1 数据流建模的语法基础

数据流建模的语法基础涉及到了连续赋值语句和运算符的使用。这些基础概念对于编写简洁、高效的硬件描述至关重要。

### 2.1.1 连续赋值语句

在SystemVerilog中,连续赋值语句使用 `assign` 关键字来实现。连续赋值表达式的右侧是永久活跃的,任何时候如果右侧的表达式值发生变化,左边的变量就会立即被更新。下面是一个简单的例子:

```systemverilog

module dataflow_examples;

wire a, b, c;

assign a = b & c; // 逻辑与操作

initial begin

b = 1'b0;

c = 1'b0;

#10 b = 1'b1; // b值改变,a的值立即更新

#10 c = 1'b1; // c值改变,a的值立即更新

end

endmodule

```

### 2.1.2 运算符和表达式

在SystemVerilog中,许多标准的算术、逻辑和位运算符可以直接使用。数据流建模中,常使用运算符来定义硬件行为。以下是一些常用的运算符:

- 逻辑运算符:`&&`(逻辑与),`||`(逻辑或),`!`(逻辑非)

- 位运算符:`&`(位与),`|`(位或),`~`(位非),`^`(位异或)

- 算术运算符:`+`(加),`-`(减),`*`(乘),`/`(除)

理解这些运算符的优先级和行为对于编写正确的硬件描述至关重要。

## 2.2 数据流操作符深入理解

在数据流建模中,操作符的理解和使用是设计高效硬件的关键。本节将深入探讨逻辑运算符、位运算符和缩减运算符,并展示它们在数据流建模中的应用。

### 2.2.1 逻辑运算符

逻辑运算符用于实现布尔逻辑运算。在数据流建模中,逻辑运算符用于描述控制流和决策逻辑。

### 2.2.2 位运算符

位运算符对二进制位进行操作。它们用于实现位级的逻辑运算和位移运算。

### 2.2.3 缩减运算符

缩减运算符是一种特殊类型的位运算符,它对单个操作数的所有位执行逻辑运算。

## 2.3 数据流建模的高级特性

数据流建模不仅仅局限于基本的语法和运算符。为了实现复杂的设计,SystemVerilog提供了多个高级特性,如模块端口连接方式和延迟及阻塞赋值等。

### 2.3.1 模块端口的连接方式

SystemVerilog支持不同类型的端口连接,包括具名连接和位置连接。理解不同连接方式的使用场景和效果是设计复杂系统的基础。

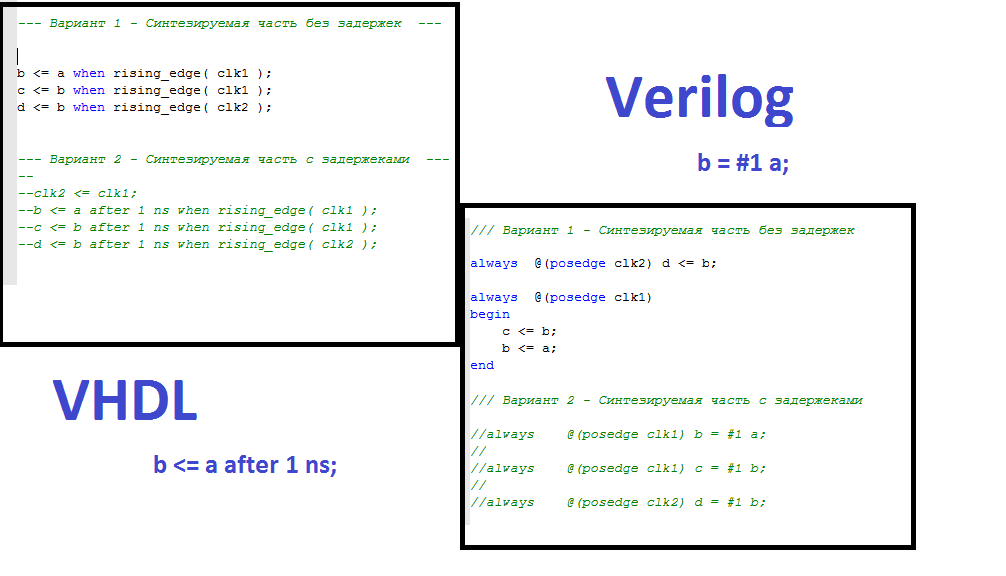

### 2.3.2 延迟和阻塞赋值

SystemVerilog允许在连续赋值语句中使用延迟,但是需要注意的是连续赋值中使用的是非阻塞赋值,而不是传统的阻塞赋值。非阻塞赋值通常用于时序逻辑,它允许模拟硬件在时钟边沿处的状态更新。

下一章将介绍数据流建模的实践技巧,包括如何设计高效的数据路径,数据流建模与FPGA实现的关系,时序控制技巧,以及代码优化和仿真测试的方法。

```

# 3. 数据流建模的实践技巧

在现代数字设计领域,SystemVerilog的数据流建模方法不仅提供了设计的灵活性,还增强了可读性和维护性。本章节深入探讨数据流建模的实践技巧,帮助设计师们实现更高效的逻辑设计、更好地进行时序控制,并优化代码以提高仿真测试的效果。

## 3.1 设计高效的数据路径

### 3.1.1 管线化技术和数据缓存

设计高效的数据路径是数据流建模的关键目标之一。在SystemVerilog中,管线化技术(Pipelining)可以显著提高数据处理的吞吐率。每个处理阶段完成一部分工作,然后将数据传递到下一个阶段,这样可以重叠多个操作,减少等待时间。

为了支持管线化,数据缓存是不可或缺的。缓存可以临时存储数据,以减少访问主存储器时的延迟。在SystemVerilog中,可以使用寄存器数组作为缓存。以下是一个简单的数据缓存示例:

```systemverilog

module data_cache #(

parameter integer DATA_WIDTH = 32,

parameter integer CACHE_SIZE = 16

)(

input logic clk,

input logic rst_n,

input logic write_enable,

input logic [DATA_WIDTH-1:0] data_in,

output logic [DATA_WIDTH-1:0] data_out

);

logic [DATA_WIDTH-1:0] cache_mem[CACHE_SIZE-1:0];

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

// 清空缓存

for (int i = 0; i < CACHE_SIZE; i++) begin

cache_mem[i] <= 0;

end

end else if (write_enable) begin

// 写入缓存

cache_mem[CACHE_SIZE-1] <= data_in;

end

end

// 读取缓存

assign data_out = cache_mem[0];

endmodule

```

在上述代码中,我们定义了一个带有写入使能和读取接口的简单数据缓存模块。缓存大小和数据宽度是参数化的,因此可以根据需要进行调整。

### 3.1.2 数据流建模与FPGA实现

FPGA(现场可编程门阵列)实现是数据流建模的一个重要应用领域。与传统的ASIC设计相比,FPGA可以提供快速的原型设计和迭代验证,同时减少设计成本。在FPGA中实现数据流建模,需要考虑资源利用率、时钟频率和热耗散等因素。

设计时,应尽量避免资源的浪费。例如,使用时序复用技术,可以在不增加硬件资源消耗的情况下,实现更多功能。此外,逻辑单元的适当布局和布线也是提高FPGA性能的关键因素。

## 3.2 数据流建模的时序控制

### 3.2.1 时钟域交叉处理

在数字设计中,时钟域交叉(CDC)是一个复杂且容易出错的问题。在数据流建模中处理CDC问题,需要确保数据在不同的时钟域之间安全传递。

处理CDC问题的一种方法是使用双触发器或双缓冲技术,以稳定数据信号。另一个常用的策略是使用异步FIFO(先进先出队列),它可以在不同的时钟域之间提供缓冲。以下是一个异步FIFO的简化实现:

```systemverilog

module async_fifo #(

parameter integer DATA_WIDTH = 8,

parameter integer ADDR_WIDTH = 4

)(

input logic wr_clk,

input logic rd_clk,

input logic rst,

input logic wr_en,

input logic rd_en,

input logic [DATA_WIDTH-1:0] din,

output logic [DATA_WIDTH-1:0] dout,

output logic full,

output logic empty

);

logic [DATA_WIDTH-1:0] mem[(1 << ADDR_WIDTH)-1:0];

logic [ADDR_WIDTH-1:0] wr_ptr;

logic [ADDR_WIDTH-1:0] rd_ptr;

logic [ADDR_WIDTH:0] count;

// FIFO读写逻辑、状态判断等代码省略

endmodule

```

### 3.2.2 同步与异步信号处理

同步信号处理在数据流建模中相对简单,通常使用阻塞或非阻塞赋值语句来实现。然而,异步信号处理则需要使用特殊的同步器来防止亚稳态的产生。

在SystemVerilog中,可以使用一个简单的两级触发器链来同步异步信号,如下所示:

```systemverilog

module sync_signal (

input logic clk,

input logic async_in,

output logic sync_out

);

logic intermediate;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

intermediate <= 0;

sync_out <= 0;

end else begin

intermediate <= async_in;

sync_out <= intermediate;

end

end

endmodule

```

在这个例子中,`async_in` 是一个异步信号,`sync_out` 是同步后的输出信号。通过两级触发器,降低了亚稳态的风险。

## 3.3 代码优化与仿真测试

### 3.3.1 代码风格与重构技巧

代码风格和重构是提高代码质量、提升可维护性的关键步骤。良好的代码风格应包括一致的命名规则、简洁的逻辑表达以及清晰的注释。

重构是一项持续的活动,它要求我们不断地审视现有代码,寻找改进的机会。以下是一些常见的重构技巧:

- 提取公共子表达式

- 合并条件表达式

- 移除多余的代码

- 重命名变量以提高可读性

通过重构,可以减小设计的复杂性,使得设计更加模块化和清晰。

#

0

0