STM32时钟系统:快速上手手册中的时钟树配置

发布时间: 2024-12-28 04:28:15 阅读量: 9 订阅数: 12

stm32时钟系统RCC配置.zip

# 摘要

本文全面探讨了STM32微控制器的时钟系统,包括其基本架构、配置实践、性能优化和进阶应用。首先介绍了STM32的时钟系统概述和时钟树结构,详细分析了内部与外部时钟源、分频器的作用、时钟树各主要分支的功能以及时钟安全系统(CSS)。接着,重点阐述了时钟树的配置方法,包括使用STM32CubeMX工具和编程实现时钟树配置,以及如何验证和调试时钟设置。文章进一步讨论了时钟系统性能优化策略,包括功耗最小化和性能最大化的时钟配置,动态时钟门控技术,以及动态调整时钟频率的实际应用。最后,文章探讨了系统时钟故障排除的方法,定制化时钟系统设计的实现,以及与实时操作系统(RTOS)结合的时钟管理。本文旨在为STM32微控制器的时钟系统设计与优化提供全面的技术指南和应用案例分析。

# 关键字

STM32;时钟系统;时钟树结构;时钟配置;性能优化;故障排除

参考资源链接:[STM32F10xxx中文参考手册:技术细节与更新](https://wenku.csdn.net/doc/6469c2355928463033e12522?spm=1055.2635.3001.10343)

# 1. STM32时钟系统概述

STM32微控制器的核心优势之一是其灵活的时钟系统设计,允许开发者根据应用需求优化性能和功耗。本章节将提供对STM32时钟系统基础结构的概览,为理解后续时钟树的具体配置打下坚实的基础。

## 1.1 时钟系统的作用

在STM32系统中,时钟系统负责为CPU、外设以及内存提供同步信号,确保系统稳定运行。此外,合理的时钟配置能够减少功耗,延长设备的电池寿命。

## 1.2 核心时钟组件

时钟系统主要由几个核心组件构成:时钟源(内部或外部)、PLL(相位锁定环)、分频器、以及多个时钟输出。每个组件均按其特定功能操作,共同协作保证系统的时序要求。

## 1.3 时钟源的选择与配置

STM32时钟系统支持多种时钟源,包括内部高速时钟(HSI)、外部高速时钟(HSE)等。正确配置时钟源对于系统性能和稳定性至关重要。

```c

// 示例代码:配置时钟源

RCC->CFGR |= RCC_CFGR_SW_HSE; // 选择外部时钟源HSE

while((RCC->CR & RCC_CR_HSERDY) == 0) {;} // 等待外部时钟源就绪

```

通过上述代码,我们可以选择并激活外部时钟源(HSE),为系统提供时钟信号。这种灵活性赋予开发者在不同应用场景中实现性能与功耗之间平衡的能力。接下来的章节将深入探讨时钟源和分频器的详细配置方法,以及如何在实际应用中优化时钟树配置。

# 2. 理解STM32时钟树结构

STM32微控制器的时钟系统设计精妙,确保了性能和能效的最佳平衡。本章将深入探讨STM32时钟树结构的核心元素,以帮助开发者充分理解并优化其性能。

## 2.1 STM32时钟源与分频器

### 2.1.1 内部时钟源

STM32内部拥有高速内部时钟源(HSI)和低速内部时钟源(LSI)。HSI通常用于系统启动或在外部晶振失效时作为备份。LSI则主要为独立看门狗和自动唤醒单元提供时钟。在配置时,开发者需要了解其频率和稳定性,以便正确设置系统时钟。

```c

// 示例代码:HSI时钟初始化

RCC->CR |= RCC_CR_HSION; // 使能HSI时钟

while((RCC->CR & RCC_CR_HSIRDY) == 0); // 等待HSI就绪

RCC->CFGR |= RCC_CFGR_SW_HSI; // 将HSI设置为系统时钟源

```

### 2.1.2 外部时钟源

STM32也支持外部时钟源(HSE),这可以是外部晶振或外部时钟信号。其允许系统使用高精度的外部时钟源,是实现高速通信和高精度计时的关键。

```c

// 示例代码:HSE时钟初始化

RCC->CR |= RCC_CR_HSEON; // 使能HSE时钟

while((RCC->CR & RCC_CR_HSERDY) == 0); // 等待HSE就绪

RCC->CFGR |= RCC_CFGR_SW_HSE; // 将HSE设置为系统时钟源

```

### 2.1.3 分频器的作用与配置

分频器的作用是降低时钟频率,以减少功耗或适应外设的工作频率。STM32支持多种分频器,包括主时钟分频器(HPRE)、高速总线分频器(PREDIV)等。

```c

// 示例代码:配置AHB总线预分频器

RCC->CFGR |= RCC_CFGR_HPRE_DIV1; // AHB总线不分频

// 示例代码:配置APB总线预分频器

RCC->CFGR |= RCC_CFGR_PPRE_DIV2; // APB总线分频2

```

## 2.2 时钟树中的主要时钟分支

### 2.2.1 系统时钟分支

系统时钟分支负责为处理器核心以及大多数外设提供时钟信号。开发者应熟悉其组成,以便在不同的应用场景下进行精确配置。

```c

// 示例代码:配置系统时钟

RCC->CFGR |= RCC_CFGR_SW_HSE; // 选择HSE作为系统时钟源

RCC->CFGR |= RCC_CFGR_HPRE_DIV1; // AHB总线不分频

RCC->CFGR |= RCC_CFGR_PPRE_DIV4; // APB总线分频4

```

### 2.2.2 外设时钟分支

外设时钟分支确保每个外设都能获得正确的时钟频率以正常工作。通常开发者需要对外设时钟进行单独配置。

```c

// 示例代码:使能外设时钟

RCC->APB2ENR |= RCC_APB2ENR_IOPAEN; // 使能GPIOA端口时钟

```

### 2.2.3 时钟输出分支

时钟输出分支允许将内部时钟信号输出到外部引脚,从而进行测量或用于调试目的。

```c

// 示例代码:配置时钟输出

RCC->CFGR |= RCC_CFGR_MCO.Prediv; // 设置时钟输出预分频

RCC->CFGR |= RCC_CFGR_MCO.Source; // 设置时钟输出源

```

## 2.3 时钟安全系统(CSS)

### 2.3.1 CSS的工作原理

时钟安全系统(Clock Security System,CSS)是STM32的硬件特性,用于在检测到外部晶振故障时自动切换到内部时钟源,确保系统稳定运行。

### 2.3.2 CSS的配置与监控

CSS的配置一般在系统初始化阶段完成,监控则依赖于实时检查CSS状态位。

```c

// 示例代码:CSS配置

RCC->CR |= RCC_CR_CSSON; // 使能CSS

while((RCC->CR & RCC_CR_CSIRDY) == 0); // 等待CSS就绪

```

```c

// 示例代码:监控CSS状态

if((RCC->CR & RCC_CR_HSIRDY) == 0) {

// CSS触发,HSE晶振故障

// 处理程序,比如切换到HSI

}

```

通过本章的介绍,读者应当已经具备了对STM32时钟树结构基本的理解,了解了内部和外部时钟源的角色,以及时钟分频器在调整系统性能中的重要性。下章将继续深入配置时钟树的实践操作,确保读者能将理论应用于实际开发中。

# 3. STM32时钟树配置实践

## 3.1 时钟树配置工具使用

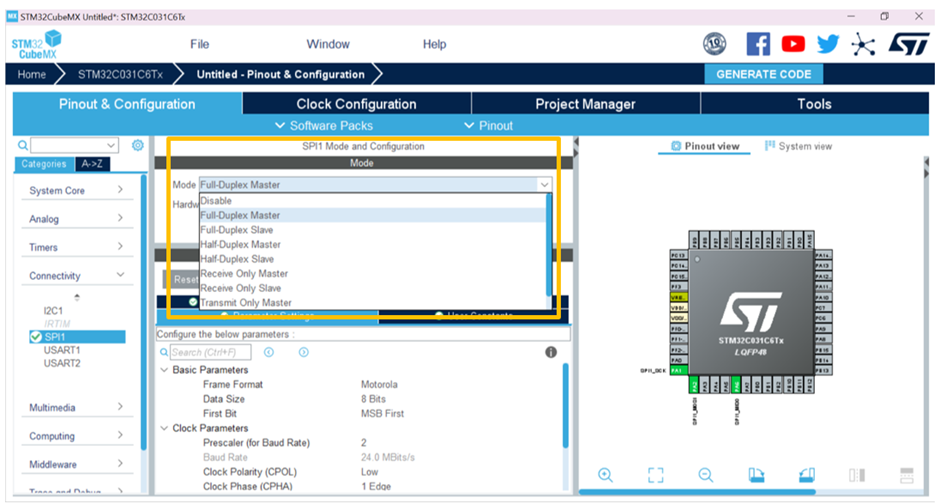

### 3.1.1 STM32CubeMX的介绍

STM32CubeMX是ST官方提供的一个图形化配置工具,它简化了STM32微控制器的配置过程,支持从项目初始化到固件库生成的一系列步骤。这个工具能够通过图形化界面帮助开发者对STM32的外设和时钟树进行配置,并生成初始化代码。除此之外,STM32CubeMX也支持对时钟树的直接操作,允许用户在图形化界面中直观地配置时钟源、分频器以及时钟树的其他相关参数。

### 3.1.2 使用STM32CubeMX配置时钟树

配置STM32时钟树的过程大体如下:

1. 打开STM32CubeMX,选择一个具体型号的STM32微控制器开始新项目。

2. 在Pinout视图中,可以看到微控制器的引脚分布。在这里可以配置外设,STM32CubeMX将自动检查引脚冲突。

3. 切换到“Clock Configuration”视图,此时可以见到STM32时钟树的图形化界面。

4. 在时钟树界面中,用户可以进行时钟源选择、分频器配置以及时钟输出设置。

5. 配置完成后,点击“Project”菜单选项,设置项目名称、选择工具链(例如Keil MDK、IAR、SW4STM32等)并生成项目代码。

这里是一个简单示例代码块,展示了如何使用STM32CubeMX生成的代码片段:

```c

/* 当使用STM32CubeMX生成代码时,此函数由用户扩展,用于配置系统时钟 */

void SystemClock_Config(void)

{

RCC_OscInitTypeDef RCC_OscInitStruct = {0};

RCC_ClkInitTypeDef RCC_ClkInitStruct = {0};

/** Initializes the CPU, AHB and APB busses clocks

*/

RCC_OscInitStruct.OscillatorType = RCC_OSCILLATORTYPE_HSE;

RCC_OscInitStruct.HSEState = RCC_HSE_ON;

RCC_OscInitStruct.PLL.PLLState = RCC_PLL_ON;

RCC_OscInitStruct.PLL.PLLSource = RCC_PLLSOURCE_HSE;

RCC_OscInitStruct.PLL.PLLMUL = RCC_PLLMUL_16;

RCC_OscInitStruct.PLL.PLLDIV = RCC_PLLDIV_2;

if (HAL_RCC_OscConfig(&RCC_OscInitStruct) != HAL_OK)

{

Error_Handler();

}

/** Initializes the CPU, AHB and APB busses clocks

*/

RCC_ClkInitStruct.ClockType = RCC_CLOCKTYPE_HCLK|RCC_CLOCKTYPE_SYSCLK

|RCC_CLOCKTYPE_PCLK1|RCC_CLOCKTYPE_PCLK2;

RCC_ClkInitStruct.SYSCLKSource = RCC_SYSCLKSOURCE_PLLCLK;

RCC_ClkInitStruct.AHBCLKDivider = RCC_SYSCLK_DIV1;

RCC_ClkInitStruct.APB1CLKDivider = RCC_HCLK_DIV1;

RCC_ClkInitStruct.APB2CLKDivider = RCC_HCLK_DIV1;

if (HAL_RCC_ClockConfig(&RCC_ClkInitStruct, FLASH_LATENCY_1) != HAL_OK)

{

Error_Handler();

}

}

```

代码逻辑分析:

此代码段是STM32CubeMX生成的系统时钟配置函数。首先初始化了一个`RCC_OscInitTypeDef`类型的结构体`RCC_OscInitStruct`,并设置时钟源为外部高速时钟(HSE)且启用PLL。然后,使用`HAL_RCC_OscConfig`函数应用这些设置。接着,初始化了另一个结构体`RCC_ClkInitStruct`,其中配置了系统时钟源为PLL,并设置AHB、APB1和APB2分频器的值。最后,使用`HAL_RCC_ClockConfig`函数应用这些时钟设置。错误处理函数`Error_Handler`被调用以处理配置中可能出现的任何错误。

## 3.2 时钟树配置代码实现

### 3.2.1 RCC(Reset and Clock Control)库函数

RCC(Reset and Clock Control)是STM32微控制器中的一个硬件模块,负责时钟和复位的控制。它是用来配置STM32时钟树的主要模块,通过操作其寄存器或调用库函数来实现时钟配置。

RCC库函数为时钟配置提供了一个高级抽象层。例如,为了启用外部高速时钟(HSE),可以调用`RCC_OscConfig`函数,而`RCC_ClockCmd`函数可以用来开启或者关闭特定时钟域。这些函数背后实际上是对相关寄存器进行操作,但库函数隐藏了这些细节,使得开发人员可以更专注于业务逻辑而不是寄存器配置。

### 3.2.2 手动编写时钟树配置代码

手动编写时钟树配置代码涉及直接操作RCC模块的寄存器。虽然这种方法需要对STM32的硬件架构有较深的理解,但可以提供更灵活的配置选项。

以下是一个手动配置STM32时钟树的例子:

```c

void SystemClock_Config(void)

{

// 启用HSE

RCC->CR |= RCC_CR_HSEON;

// 等待HSE就绪

while ((RCC->CR & RCC_CR_HSERDY) == 0);

// 设置PLL配置

RCC->CFGR |= (uint32_t)((RCC_PLLCFGR_PLLSRC_HSE) | (RCC_PLLCFGR_PLLMUL4) | (RCC_PLLCFGR_PLLDIV2));

// 启用PLL

RCC->CR |= RCC_CR_PLLON;

// 等待PLL就绪

while ((RCC->CR & RCC_CR_PLLRDY) == 0);

// 设置系统时钟源为PLL

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_HSE;

// 配置AHB、APB1和APB2分频器

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1 | RCC_CFGR_PPRE1_DIV2 | RCC_CFGR_PPRE2_DIV1;

// 等待PLL成为系统时钟源

while ((RCC->CFGR & RCC_CFGR_SWS) != RCC_CFGR_SWS_PLL);

}

```

逻辑分析:

这段代码通过直接操作`RCC->CR`、`RCC->CFGR`寄存器来启用外部高速时钟(HSE)并配置PLL(相位锁定环)。它设置了PLL的源、乘数和分频器,以产生所需的系统时钟频率。代码中使用了位带操作来开启相应的时钟,并等待直到每个步骤的时钟源准备就绪。最后,代码配置了AHB和APB总线的时钟分频器,并切换系统时钟源到PLL。

### 3.2.3 实时系统时钟(RTC)配置

实时系统时钟(RTC)通常需要使用到一个精确的32.768 kHz的外部晶振来保持时间。RTC的配置也是时钟树配置的一部分。以下是如何通过代码配置RTC时钟的例子:

```c

void RTC_Config(void)

{

RCC->BDCR |= RCC_BDCR_BDRST; // 重置RTC

RCC->BDCR &= ~RCC_BDCR_BDRST; // 重置完成,清除重置位

// 启用LSE

RCC->BDCR |= RCC_BDCR_LSEON;

// 等待LSE就绪

while ((RCC->BDCR & RCC_BDCR_LSERDY) == 0);

// 设置RTC时钟源为LSE

RCC->BDCR |= RCC_BDCR_RTCSEL_LSE;

// 启用RTC时钟

RCC->BDCR |= RCC_BDCR_RTCEN;

// 等待RTC寄存器同步

RTC->CRL |= RTC_CRL_RSF;

// 配置RTC预分频器,设置时钟频率为1Hz

RTC->PRLL = 0x0000;

RTC->PRLH = 0x00FF;

}

```

逻辑分析:

上述代码首先重置了RTC模块。接下来,启用了外部低速时钟(LSE)并在LSE稳定后选择它作为RTC时钟源。然后,通过设置`RCC->BDCR`寄存器的`RTCEN`位来启用RTC时钟。为了设置RTC的时钟频率为1 Hz,代码修改了预分频器寄存器`RTC->PRLL`和`RTC->PRLH`。最后,等待RTC寄存器同步,这允许后续的操作。

## 3.3 时钟配置的验证与调试

### 3.3.1 利用调试工具验证时钟配置

验证时钟配置是否正确通常需要使用调试工具如ST-Link,并结合集成开发环境(IDE)如Keil uVision、STM32CubeIDE等。调试工具能够提供实时的寄存器读取和修改功能,可以帮助开发者确认时钟配置是否正确。

在调试模式下,开发人员可以使用如下步骤检查时钟配置:

1. 启动调试会话,并将程序下载到目标设备。

2. 设置断点在`SystemClock_Config()`函数中,以便在时钟配置完成后立即暂停程序执行。

3. 运行调试器并观察时钟相关的寄存器值是否符合预期配置。

### 3.3.2 常见问题排查与修复

在时钟配置过程中可能会遇到多种问题,如时钟源未能正常工作、PLL未能锁定、时钟频率不符合预期等。排查这些问题通常需要开发者具备对STM32时钟系统的深入了解。

一些常见的问题排查方法包括:

1. **时钟源未启动**:检查时钟源使能位是否被正确设置,并确保晶振外部连接正常。

2. **PLL未锁定**:确保PLL的参数配置正确(乘数、分频器等),并检查时钟源稳定性。

3. **时钟频率不符合预期**:检查时钟树的分频器设置,以及PLL的输入频率是否正确。

4. **外设时钟配置错误**:确保为外设配置了正确的时钟源,并且它们的时钟使能位被正确设置。

通过这些排查步骤,可以定位和修复大多数时钟配置中的问题。如果问题依旧无法解决,可以参考STM32的参考手册、数据手册或联系技术支持获取更深入的帮助。

# 4. STM32时钟系统性能优化

## 4.1 时钟树优化策略

### 4.1.1 最小化功耗的时钟配置

在嵌入式系统中,功耗管理是一个关键因素,特别是在电池供电的便携式设备中。STM32的时钟系统提供了一系列的工具和技巧,以实现功耗的最小化。

在选择时钟源和配置时钟树时,有几个原则可以遵循以最小化功耗:

- **使用低速时钟源**:尽可能使用内部低速时钟(LSI)或外部低速时钟(LSE)替代高速时钟源(如HSE),因为它们通常消耗更少的电流。

- **使用时钟门控**:动态地启用和禁用外设时钟可以减少不必要的功耗。

- **利用时钟输出**:将不需要的时钟输出置为低电平,以减少功耗。

- **调整时钟频率**:当需要的性能不高时,降低时钟频率以降低功耗。

代码示例中,我们可以通过配置RCC库函数来实现上述策略:

```c

// 禁用不必要的外设时钟以降低功耗

RCC->APB1ENR &= ~(TIM2EN | SPI1EN); // 禁用TIM2和SPI1的时钟

RCC->APB2ENR &= ~USART1EN; // 禁用USART1的时钟

// 使用LSI作为RTC的时钟源并启用它

RCC->CSR |= RCC_CSR_RTCSEL_LSI;

RCC->CSR |= RCC_CSR_RTCEN;

// 降低AHB和APB总线时钟频率

RCC->CFGR |= RCC_CFGR_HPRE_DIV16; // AHB分频16

RCC->CFGR |= RCC_CFGR_PPRE1_DIV2; // APB1分频2

RCC->CFGR |= RCC_CFGR_PPRE2_DIV2; // APB2分频2

```

在实际应用中,可以通过动态调整时钟树的配置来优化功耗,这将在下面的章节中详细讨论。

### 4.1.2 最大化性能的时钟配置

在需要最大化性能的应用中,通常会采用外部高速时钟源(HSE)和调整PLL(相位锁定环)来获得更高的时钟频率。为了优化性能,开发者需要注意以下几点:

- **使用高速外部晶振**:外部高速晶振(HSE)通常比内部高速时钟(HSI)提供更稳定的时钟源,有助于提高系统的整体性能。

- **正确配置PLL**:确保PLL的参数被正确设置,以匹配所需的系统时钟频率。

- **启用高速总线时钟**:通过启用AHB和APB的高速时钟,外设可以达到最佳性能。

代码示例:

```c

// 启用外部高速时钟源(HSE)

RCC->CR |= RCC_CR_HSEON;

while(!(RCC->CR & RCC_CR_HSERDY)); // 等待HSE稳定

// 配置PLL,假设使用HSE作为PLL的输入源

RCC->CFGR |= RCC_CFGR_PLLSRC; // PLL源为HSE

RCC->CFGR |= RCC_CFGR_PLLMULL9; // 设置PLL倍频,假设HSE是8MHz,输出9倍频至72MHz

// 等待PLL就绪,并将系统时钟切换到PLL

while(!(RCC->CR & RCC_CR_PLLRDY));

RCC->CFGR |= RCC_CFGR_SW_HSE; // 将PLL作为系统时钟源

while((RCC->CFGR & RCC_CFGR_SWS) != RCC_CFGR_SWS_PLL); // 等待PLL稳定

// 启用高速总线时钟

RCC->CFGR |= RCC_CFGR_HPRE_DIV1;

RCC->CFGR |= RCC_CFGR_PPRE1_DIV2; // APB1时钟频率为36MHz

RCC->CFGR |= RCC_CFGR_PPRE2_DIV1; // APB2时钟频率为72MHz

```

在执行上述配置后,STM32将具有优化的性能。然而,需要注意的是,高速运行将导致功耗的增加,因此在性能和功耗之间需要做出权衡。

## 4.2 外设时钟管理

### 4.2.1 动态时钟门控技术

动态时钟门控(Dynamic Clock Gating)技术是管理外设时钟的有效方式,该技术允许在特定条件下动态地启用或禁用外设时钟。对于STM32微控制器,RCC库提供了相关的功能来实现这一技术。

以下是使用RCC库实现动态时钟门控的步骤:

1. **启用外设时钟**:在需要使用外设之前,首先需要启用对应的外设时钟。

2. **配置外设**:对外设进行配置,以便执行特定的功能。

3. **禁用外设时钟**:在不使用外设时,可以通过编程禁用外设时钟,以减少功耗。

代码示例:

```c

// 启用ADC外设时钟

RCC->APB2ENR |= RCC_APB2ENR_ADC1EN;

// 配置ADC,并开始转换

// ADC配置代码略

// 在完成ADC转换后,禁用ADC外设时钟

RCC->APB2ENR &= ~RCC_APB2ENR_ADC1EN;

```

通过这种方式,可以确保外设只在需要时消耗功率,从而降低整体功耗。动态时钟门控技术是实现STM32低功耗应用的关键技术之一。

### 4.2.2 外设时钟使能与禁用策略

除了动态时钟门控技术,合理规划外设时钟使能和禁用的策略同样重要。对于STM32,可以根据不同的应用场景来制定策略:

- **系统启动阶段**:在系统启动时,应只启用必要的核心外设,如时钟、电源管理、复位和调试组件。

- **运行阶段**:当进入低功耗模式或特定外设不再需要时,应关闭对应的外设时钟。

- **唤醒阶段**:在从低功耗模式唤醒后,必须重新启用之前禁用的外设时钟。

实现时,需注意外设时钟的启用顺序,以及外设在不需要时及时禁用的重要性。

## 4.3 实例分析:动态调整时钟频率

### 4.3.1 动态时钟调整的原理

动态调整时钟频率允许系统在不同的运行模式之间平滑切换,例如在执行计算密集型任务时提高时钟频率,而在待机模式下降低时钟频率以节省电能。STM32的时钟系统支持通过软件配置来实现这一功能。

动态调整时钟频率的原理涉及几个关键步骤:

- **时钟源的选择**:根据需求选择适当的时钟源(HSI、HSE或LSI)。

- **分频器的配置**:在系统时钟和外设时钟之间设置正确的分频值。

- **PLL的动态调整**:根据需要动态地开启或关闭PLL,并调整其参数。

### 4.3.2 实现动态时钟调整的步骤

要实现动态时钟调整,需要编写代码来执行时钟源切换和分频器调整。以下是一个简单的实现示例:

```c

// 假设系统已经运行在HSE时钟源,现在需要切换到LSI时钟源

RCC->CSR |= RCC_CSR_LSEON; // 启用外部低速晶振

while (!(RCC->CSR & RCC_CSR_LSERDY)); // 等待LSI就绪

RCC->CFGR &= ~RCC_CFGR_SW_MASK; // 清除SW字段

RCC->CFGR |= RCC_CFGR_SW_LSI; // 将系统时钟源切换到LSI

while ((RCC->CFGR & RCC_CFGR_SWS) != RCC_CFGR_SWS_LSI); // 等待LSI稳定

// 现在系统运行在LSI时钟源,可以通过调整分频值来降低频率

RCC->CFGR &= ~RCC_CFGR_HPRE_MASK; // 清除AHB分频字段

RCC->CFGR |= RCC_CFGR_HPRE_DIV64; // 设置AHB分频为64

// 如果需要重新启用HSE和PLL,可以执行类似的操作

```

### 4.3.3 动态时钟调整的性能评估

在实现动态时钟调整后,对于性能的评估是必不可少的。评估通常包括以下方面:

- **功耗分析**:比较不同频率下的电流消耗情况。

- **响应时间**:评估从低频率切换到高频率时的延迟。

- **系统稳定性**:检查在动态调整频率时系统是否保持稳定。

性能评估可以通过硬件测量工具进行,如数字示波器和电源分析仪。也可以利用软件工具,例如通过监视系统运行期间的时钟频率和功耗统计。

在本节中,我们详细探讨了STM32时钟系统的性能优化策略,包括最小化功耗和最大化性能的配置方法,以及外设时钟的管理策略。动态时钟频率调整的应用实例展示了如何在实际项目中根据不同的需求调整时钟频率,并进行了性能评估。

在下一章节中,我们将深入探讨STM32时钟系统的进阶应用,包括故障排除、定制化设计以及与实时操作系统集成的时钟管理。

# 5. STM32时钟系统的进阶应用

## 5.1 系统时钟故障排除

在复杂的嵌入式系统中,时钟问题往往会导致不可预测的行为。本节将介绍如何快速定位并解决STM32时钟系统出现的问题。

### 5.1.1 故障排除的基本步骤

故障排除时,应从以下几个步骤开始:

1. **复现问题**:首先尝试复现系统时钟故障,记录发生条件。

2. **检查硬件连接**:确认所有晶振和时钟相关的硬件连接是否正确无误。

3. **检查时钟源状态**:通过阅读STM32的时钟状态寄存器,检查内部和外部时钟源的状态。

4. **软件配置分析**:检查软件中时钟相关的配置代码,确认配置是否与硬件相匹配。

### 5.1.2 使用STM32CubeMX进行故障诊断

STM32CubeMX提供了一个直观的图形用户界面,用于生成时钟树配置代码。故障诊断时,可以:

1. **打开时钟配置视图**:在STM32CubeMX中,加载项目并打开时钟树视图。

2. **可视化时钟配置**:查看时钟树的可视化表示,理解时钟配置是否合理。

3. **实时校验配置**:尝试运行项目,并利用调试器实时检查时钟状态寄存器值是否符合预期。

## 5.2 定制化时钟系统设计

为满足特定应用的性能或功耗要求,可能需要定制化设计时钟系统。

### 5.2.1 设计要求与约束条件

在进行定制化设计时,要先明确以下要求和约束条件:

- **性能要求**:根据应用场景确定CPU和外设的运行频率。

- **功耗限制**:设计低功耗应用时,需要考虑各时钟域的省电模式。

- **时钟精度**:某些应用对时钟精度有特定要求,如无线通信等。

- **成本考虑**:在满足性能和功能的前提下,应尽量减少额外的硬件成本。

### 5.2.2 定制化设计的实现步骤

1. **确定基准时钟源**:选择合适的内部或外部时钟源作为基准。

2. **设计时钟树**:利用时钟树的分频、倍频和开关,设计出所需的时钟结构。

3. **软件配置**:通过RCC库函数编写代码,实现定制化设计的时钟配置。

4. **验证和调整**:运行系统并测试时钟配置是否达到预期效果,必要时进行调整。

## 5.3 与操作系统结合的时钟管理

许多应用场合,特别是在复杂的系统中,需要运行实时操作系统(RTOS)。

### 5.3.1 实时操作系统(RTOS)的时钟需求

RTOS对时钟管理有以下特殊需求:

- **时钟节拍(Tick)**:RTOS依赖定时器产生的周期性中断来实现时间管理。

- **时间片调度**:需要精确的时钟源来保证任务的准确调度。

- **低延迟中断响应**:系统中断响应时间的减少对于RTOS至关重要。

### 5.3.2 集成RTOS的时钟配置方法

集成RTOS时的时钟配置方法包括:

1. **配置系统时钟**:确保系统时钟配置满足RTOS对时钟源和时钟频率的需求。

2. **设置时钟节拍中断**:利用定时器产生周期性中断,设置中断频率(通常为1kHz)。

3. **优化中断优先级**:合理设置时钟中断及其他中断的优先级,保证RTOS的调度器能够正确响应。

```c

// 示例代码:设置时钟节拍中断

void SysTick_Handler(void) {

HAL_IncTick();

osSystickHandler();

}

int main(void) {

HAL_Init();

SystemClock_Config(); // 配置系统时钟

HAL_SYSTICK_Config(SystemCoreClock / 1000); // 配置1ms的时钟节拍

// ...其他初始化代码

while(1) {

// 应用代码

}

}

```

通过本章的内容,您应该能够掌握STM32时钟系统的高级应用和故障排除方法,以及如何将STM32时钟系统与RTOS集成。这将大大增强您在设计复杂嵌入式系统时的信心和能力。

0

0