深入理解74LS273触发器时序:触发机制全面分析

发布时间: 2024-12-14 12:33:52 阅读量: 8 订阅数: 10

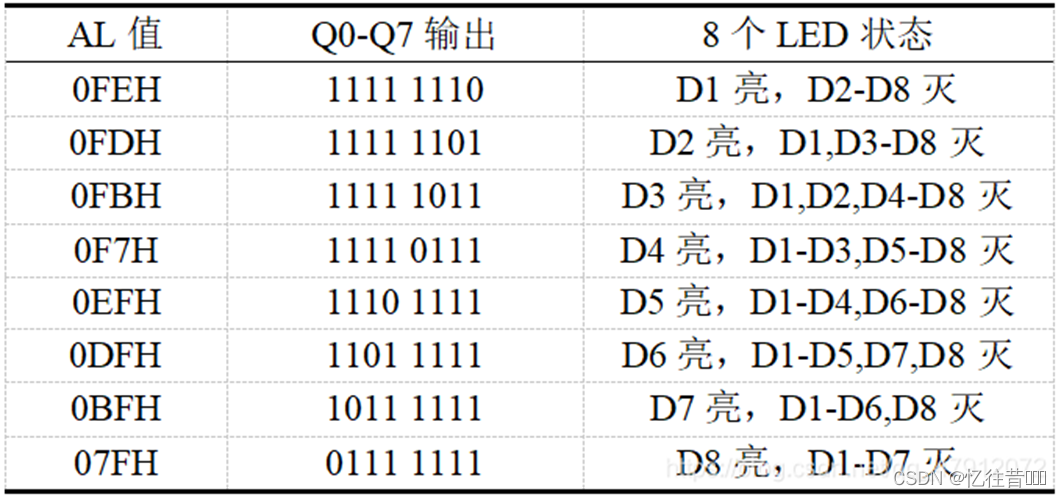

基于Proteus的74LS273的单片机控制仿真

参考资源链接:[74LS273详解:8位数据/地址锁存器](https://wenku.csdn.net/doc/6412b5d8be7fbd1778d449a1?spm=1055.2635.3001.10343)

# 1. 74LS273触发器时序概述

在数字电路设计中,时序控制至关重要,而触发器作为一种基本的时序电路元件,扮演着存储和传递信息的角色。74LS273触发器是8位D型锁存器,具有正边沿触发和清零功能,广泛应用于同步数据传输和存储系统。本章将提供对74LS273触发器时序特性的初步了解,为后续更深入的学习和应用打下基础。通过对触发器时序的分析,我们可以确保数据在系统中的稳定传输和处理,避免诸如竞争和冒险等时序问题。

# 2. 74LS273触发器的基础理论

### 2.1 74LS273触发器工作原理

#### 2.1.1 触发器的定义和分类

在数字电路设计中,触发器(Flip-Flop)是一种基本的双稳态存储元件,其核心功能是存储一位二进制信息。由于其状态可以在特定的时钟信号边沿触发下改变,故名“触发器”。触发器可以用来构建各种复杂逻辑电路,如计数器、寄存器、状态机等。

触发器按照其功能可以分为多种类型,例如:

- D型触发器:数据在时钟信号的上升沿(或下降沿)被锁存。

- T型触发器:在每个时钟周期,其输出状态翻转。

- JK触发器:具有更复杂的逻辑功能,能够在时钟信号边沿触发时根据输入J和K的状态决定其输出状态。

#### 2.1.2 74LS273触发器的内部结构

74LS273是一个8位的D型正边沿触发的寄存器,这意味着当输入信号在时钟脉冲的上升沿时,数据会被锁存到输出。它包含八个独立的D型触发器,能够通过一个共同的时钟信号进行同步操作。每个多路复用器有两个数据输入(D0到D7),一个时钟输入(CLK),一个清除输入(CLR)和八个输出(Q0到Q7)。

内部结构上,74LS273通过将多个D型触发器并联,形成一个多位寄存器。每个触发器均包含一个锁存器,在锁存器中,D输入通过一个门电路传递到一个S-R(置位-复位)触发器的输入端。当门电路因时钟信号的上升沿而打开时,D输入的值被传递到S-R触发器,然后被锁存直到下一个上升沿到来。

### 2.2 74LS273触发器的时序特性

#### 2.2.1 时序参数解析

在使用74LS273触发器时,了解其时序参数至关重要。时序参数描述了触发器在时钟信号控制下的行为。主要参数包括:

- `setup time (tsu)`:在时钟信号的上升沿前,输入信号必须保持稳定的时间。

- `hold time (th)`:输入信号在时钟信号的上升沿后必须保持稳定的时间。

- `clock-to-output delay (tpd)`:时钟信号上升沿到输出信号稳定的时间。

时序参数对于保证数字系统正确运行至关重要,因为它们影响着触发器及整个电路的时序性能。

#### 2.2.2 时序图表的解读

时序图表是理解触发器工作状态随时间变化的重要工具。在74LS273触发器的时序图表中,我们可以看到时钟信号、输入D信号、清除信号CLR以及输出Q信号随时间变化的情况。典型地,一个时序图会展示:

- 清除信号CLR变为低电平,触发器复位。

- 输入信号D稳定。

- 时钟信号CLK上升沿到来,触发器捕获输入信号D的状态并将其传递到输出Q。

通过时序图表,我们可以观察到在时钟信号的每一个上升沿,如果输入信号满足`tsu`和`th`的条件,触发器的输出Q将会更新以匹配输入D。不满足这些条件则可能导致不可预测的输出,是设计时需要避免的。

### 2.3 触发器与存储器的关系

#### 2.3.1 触发器在数字存储系统中的作用

在数字存储系统中,触发器作为最基础的存储单元,是构建其他存储设备,如锁存器、寄存器和内存阵列的基石。触发器可以存储一位二进制数据,而多个触发器并联可形成存储器位宽更大的数据存储单元,如8位、16位、32位等。通过这种方式,触发器在存储器设计中扮演着核心角色。

在CPU中,触发器被广泛用于实现寄存器和高速缓存(Cache)存储。寄存器用于暂存指令、数据和地址信息,而高速缓存则利用触发器快速响应数据请求,提高了计算机的数据处理能力。

#### 2.3.2 提升存储系统时序性能的策略

为了提升存储系统的时序性能,设计者们可以采取以下策略:

- 使用高速触发器:选用具有较小时序参数(如`tsu`和`tpd`)的触发器可以提高存储系统的响应速度。

- 时序优化设计:通过合理安排触发器的时钟分布和路径,减少信号在电路中的传输延迟。

- 信号完整性分析:确保信号在电路中传输时不会因为信号反射、串扰等电磁现象而导致时序问题。

- 同步设计原则:将相关信号同步到同一个时钟边缘,减少因为时钟不同步引起的时序不确定性。

- 使用去抖动电路:在输入信号中加入去抖动电路以确保输入信号的稳定,从而避免因为信号抖动引起的时序问题。

通过这些策略,可以有效提高存储系统整体的时序性能,从而提升整个数字系统的稳定性和响应速度。

# 3. 74LS273触发器的逻辑应用

## 3.1 触发器在同步逻辑中的应用

### 3.1.1 同步逻辑设计原则

同步逻辑设计是一种数字电路设计方法,其中所有触发器都是由同一个时钟信号控制的,这确保了数据在触发器之间的移动是同步进行的。同步逻辑的关键优势在于其可预测性和简化的设计流程,因为所有操作都与一个全局时钟信号同步。为了有效实现同步逻辑设计,需要遵循以下原则:

- 保持所有时钟路径一致。这意味着从时钟源

0

0