【低功耗设计指南】:MIPI D-PHY v2.1 最佳实践探索

发布时间: 2024-12-13 21:15:43 阅读量: 50 订阅数: 47

MIPI DSI Specification V2.1

参考资源链接:[mipi_D-PHY_specification_v2-1-er01.pdf](https://wenku.csdn.net/doc/6401aba4cce7214c316e8f8e?spm=1055.2635.3001.10343)

# 1. MIPI D-PHY v2.1技术概述

## 1.1 接口技术的发展与应用

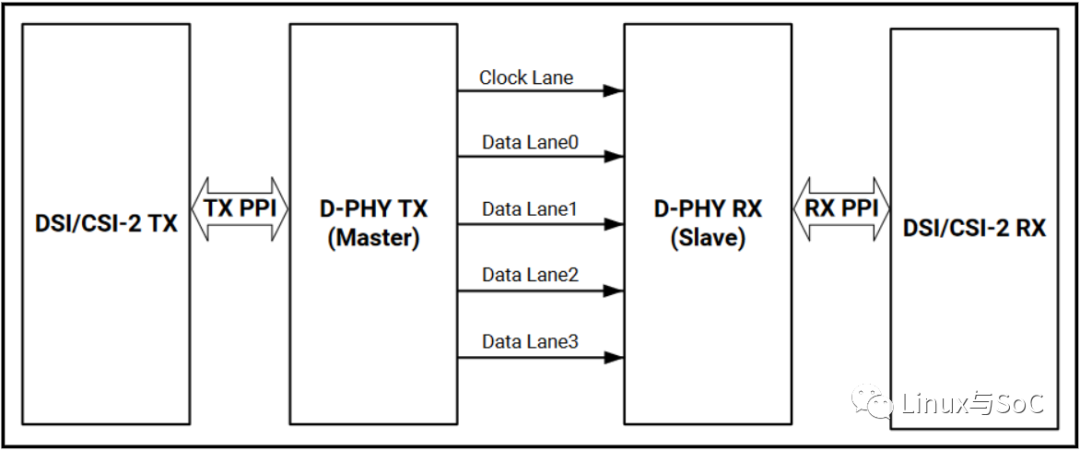

MIPI D-PHY v2.1是移动行业处理器接口(Mobile Industry Processor Interface)的一部分,主要用于移动和手持设备中,将应用处理器与相机传感器、显示器以及其它外设连接起来。它支持多种数据传输类型,并且优化了在高速率与低功耗模式之间的切换,以适应便携式设备的电源管理需求。

## 1.2 MIPI D-PHY v2.1的主要特点

随着版本的升级,MIPI D-PHY v2.1引入了新的时钟模式、改进的通道绑定机制和增强的数据速率。它能在保证图像和视频质量的同时,有效降低功耗。这一代技术特别强调了对更低功耗操作的优化,以适应日益增长的移动设备电池寿命需求。

## 1.3 技术规格与实际应用

本节将详细介绍MIPI D-PHY v2.1的技术规格,包括其物理层设计、通道配置以及操作模式。同时,将结合实际案例,分析该技术在高速数据传输和低功耗领域的应用。通过对比不同版本的D-PHY,突显v2.1版本在性能和功耗管理方面的优势。

接下来的内容将深入探讨低功耗设计的基础理论,分析能效比的定义及其重要性,并引入不同的低功耗关键技术,为理解MIPI D-PHY v2.1的低功耗特性奠定基础。

# 2. 低功耗设计的基础理论

## 2.1 低功耗设计的重要性和原则

### 能效比的定义与重要性

能效比是一个衡量设备性能与能耗之间关系的指标,它是指设备完成单位任务所需消耗的能量。在低功耗设计中,提升能效比意味着在不牺牲性能的前提下,尽可能地减少能量的使用。提高能效比通常涉及到对芯片内部各个子系统的设计进行优化,包括改进电路设计、使用先进的工艺技术以及优化电源管理策略。

从实际应用的角度来看,能效比的重要性在于它直接影响到产品的续航能力和运行效率。例如,在移动设备中,高能效比意味着电池使用寿命更长,用户体验更加友好;在数据中心中,提高能效比可以降低电费和冷却成本,从而减少总体运营开支。

### 设备工作状态的能耗模型

设备在不同的工作状态下,其能耗模型会有很大差异。一般而言,可以将设备的工作状态分为三种:活跃状态、休眠状态和关闭状态。不同的状态决定了设备的功耗水平,这为低功耗设计提供了多种节能策略。

活跃状态是指设备正在执行任务,此时设备的功耗最高;休眠状态是指设备处于待命状态,对任务响应的时间非常短,功耗相对较低;关闭状态则是设备完全不工作,功耗最低。低功耗设计旨在确保设备在不影响功能的前提下,尽可能多地处于低功耗状态,同时快速切换到活跃状态以完成必要的任务。

## 2.2 低功耗设计的关键技术

### 电源门控技术(Power Gating)

电源门控技术是一种有效的低功耗设计技术,它通过在电源和地线之间添加一个开关来实现对电路的控制,从而在某些逻辑块不工作时切断其电源。这样可以显著减少静态功耗,因为它减少了由于漏电流引起的能量损失。

电源门控技术的实施需要考虑多个方面,包括门控结构的选择、门控网络的设计、以及确保信号完整性。例如,为了保证信号能够正常通过门控网络,可能需要引入一些电平转换逻辑,以便在不同电源域间传递信号。

### 多阈值电压技术(MTCMOS)

多阈值电压技术(MTCMOS)是一种基于工艺层面的低功耗技术,它通过使用不同阈值电压的晶体管来构建电路,从而实现降低功耗的目的。高阈值电压晶体管具有较低的漏电流,适用于功耗敏感的部分;而低阈值电压晶体管则用于对速度要求较高的部分。

MTCMOS技术的挑战在于需要在设计阶段充分考虑不同阈值电压晶体管的应用场景和功耗特性,同时还要注意保证电路的性能不受影响。在某些情况下,还可能需要引入特殊的电路设计来适应不同阈值电压晶体管之间的转换。

### 动态电压频率调整(DVFS)

动态电压频率调整(DVFS)是一种电源管理技术,它根据设备当前的工作负载动态调整电压和频率。在负载较低时,DVFS降低电压和频率,从而减少功耗;在负载增加时,则提高电压和频率以确保性能。

DVFS的一个关键设计点是如何准确预测和响应设备的工作负载变化,以便及时调整电压和频率。这通常涉及到复杂的监控机制和预测算法,通过这些机制可以尽可能地在不影响性能的情况下实现功耗的优化。

DVFS策略的实现还需权衡功耗、性能、温度和稳定性等因素。例如,过度降低电压可能会导致电路不稳定,增加错误率,因此需要一个精心设计的电压频率调度策略。

在本章节的讨论中,我们介绍了低功耗设计的基础理论,涵盖了能效比的概念和重要性,以及不同设备工作状态下的能耗模型。接着,我们探讨了电源门控技术、多阈值电压技术以及动态电压频率调整等关键技术,并分析了这些技术的原理、实现方法和应用场景。这些基础理论为后续章节中MIPI D-PHY v2.1的低功耗特性和实际应用案例的讨论提供了理论支撑和设计思路。

# 3. MIPI D-PHY v2.1的低功耗特性

## 3.1 D-PHY传输的低功耗机制

### 3.1.1 低功耗传输模式的实现

MIPI D-PHY v2.1标准通过优化物理层的传输方式,在满足高速传输需求的同时,引入了多种低功耗模式。这些模式通过不同的机制降低了整个通信链路的能耗。

首先,D-PHY支持一种称为HS-Mode(High Speed Mode)的高速传输模式,在此模式下数据以并行方式传输,虽然高速但会产生较大的功耗。为了减少功耗,D-PHY还引入了LP-Mode(Low Power Mode),在此模式下,数据以串行方式传输,速度虽然降低,但功耗显著下降。

除此之外,D-PHY还允许快速从HS-Mode切换到LP-Mode,以及在空闲时将LP-Mode进一步降低功耗。这些快速切换技术是实现低功耗的关键。D-PHY的HS-Mode和LP-Mode之间的切换时间极短,通常在几十纳秒级别。快速切换避免了长时间处于高功耗状态,从而有效减少了总体能耗。

在LP-Mode下,通过使用微小的电流来保持数据传输链路,进一步降低了功耗。即使在待命状态下,D-PHY链路也能通过关闭部分电路来减少能量损失,这使得设备在空闲时也能达到极低的能耗状态。

### 3.1.2 时钟线的节能策略

在高速数据传输中,时钟线的功耗往往占不小的比例。D-PHY设计了一个称为时钟停止(Clock Stopping)的机制,允许在数据传输间隔期间停止时钟信号的传输,从而节省能量。

这种机制在LP-Mode下尤为重要。在低功耗状态下,时钟线不再持续发送脉冲,而是根据需要发送时钟信号。这种按需传输的策略大大减少了时钟线的能量消耗。

在实现时钟停止时,需要确保发送端和接收端能够同步,以避免因时钟不同步导致的数据传输错误。D-PHY协议中规定了一套严格的时钟恢复机制,确保即使在停止时钟的情况下,接收端也能准确地恢复时钟信号。

此外,D-PHY还采用了时钟域交叉技术,允许不同速度的时钟信号之间有效对接,这样

0

0