【高速数字电路】:LVTTL与LVCMOS的应用分析与优化

发布时间: 2024-12-15 08:32:36 阅读量: 3 订阅数: 6

常用电平标准:现在常用的电平标准有TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVPECL、RS232、RS485等,还有一些速度

参考资源链接:[LVTTL LVCMOS电平标准](https://wenku.csdn.net/doc/6412b6a2be7fbd1778d476ba?spm=1055.2635.3001.10343)

# 1. 高速数字电路与接口标准概述

在数字化时代的浪潮下,高速数字电路已经成为各种电子系统不可或缺的核心组成部分。设计高速电路时,正确选择和应用接口标准对于保证数据准确传输、提高系统性能至关重要。本章将简要介绍高速数字电路及其接口标准的基本概念和重要性。

## 1.1 高速数字电路的定义

高速数字电路涉及的数据速率通常以GHz为单位,这些电路被广泛用于计算机、通信设备和消费电子产品等领域。随着技术的发展,对电路的性能要求也越来越高,这就需要先进的接口技术来支持高速、高密度的数据传输。

## 1.2 接口标准的作用

接口标准定义了电路板上不同组件之间或不同设备之间进行通信的规则和参数,它保证了不同制造商生产的设备能够互操作。在高速数字电路设计中,接口标准的选择直接影响系统的可靠性和性能。

## 1.3 高速数字电路的关键特性

高速数字电路设计面临的挑战包括信号完整性问题、时序问题、热管理、电磁兼容性等。一个好的接口标准能够缓解这些问题,保证信号在传输过程中最小化失真和干扰,从而实现高效、稳定的数据传输。

# 2. LVTTL与LVCMOS接口技术基础

## 2.1 LVTTL接口标准

### 2.1.1 LVTTL的工作原理和电气特性

LVTTL(Low Voltage TTL)是一种低压TTL(Transistor-Transistor Logic)接口标准,广泛应用于集成电路(IC)的I/O接口设计中。它属于TTL技术的低压版本,旨在减少功耗并提高速度。LVTTL的工作电压范围通常在2.7V至3.6V之间,与传统的5V TTL标准相比,更低的电压有助于减少功耗和改善电磁兼容性。

LVTTL的逻辑高电平通常定义为2.0V以上,逻辑低电平为0.8V以下,确保了信号的明确区分和噪声容限。在电气特性上,它要求驱动器提供足够的电流以驱动负载,同时要求接收器能够正确识别不同电平状态的信号。LVTTL的负载能力与5V TTL相比略有降低,但在高速和低功耗应用中仍然表现优秀。

### 2.1.2 LVTTL的应用场景和优势

LVTTL接口标准由于其低电压特性,非常适合于便携式设备和手持设备中的集成电路设计。这些设备往往对功耗有严格要求,LVTTL由于其低功耗特性而成为首选。此外,LVTTL还被广泛应用于高密度集成电路设计中,如FPGA、ASIC等,这是因为其能够提供较高的信号密度和较短的信号传输时间。

LVTTL相较于其他接口标准的优势主要体现在以下几点:

- **低功耗**:低工作电压直接导致功耗降低,延长了电池寿命,对于移动设备来说至关重要。

- **高密度**:由于电压低,相同的芯片面积可以集成更多的电路,提高了芯片的集成度。

- **高速性能**:LVTTL在保持低功耗的同时,依然能够维持较高的信号传输速率,适合高速电路设计。

LVTTL由于其广泛的应用和优势,成为了许多标准中的一部分,包括PCI总线和一些专用的数字通信接口。然而,在如今追求更高性能和更低功耗的环境中,LVCMOS正逐渐取代LVTTL成为主流标准。

## 2.2 LVCMOS接口标准

### 2.2.1 LVCMOS的工作原理和电气特性

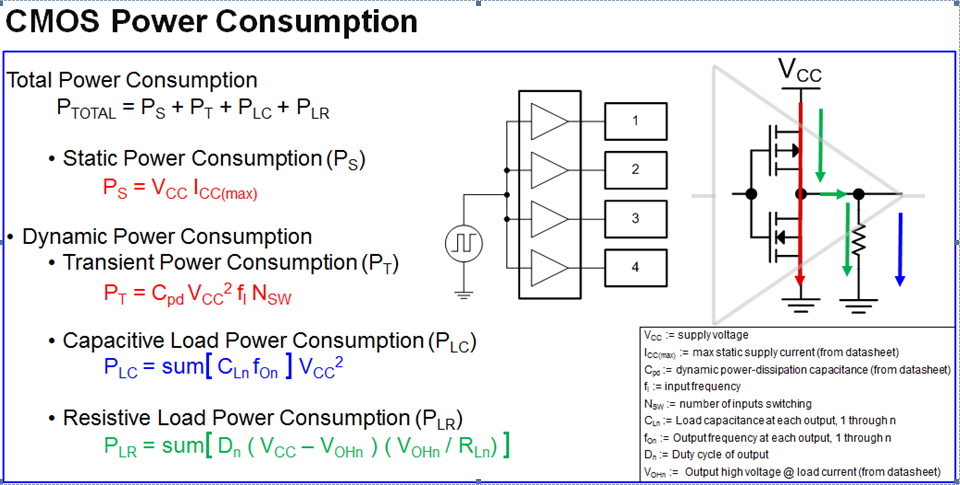

LVCMOS(Low Voltage Complementary Metal-Oxide-Semiconductor)是一种互补金属氧化物半导体接口标准,特别适合于低电压应用。与LVTTL类似,LVCMOS工作于较低的电压范围(通常为1.65V至3.6V),以减少功耗和提高电效率。它通过使用CMOS技术,实现更低的功耗和更高的集成度,同时保持了较高的信号切换速度。

LVCMOS的工作原理基于CMOS的N沟道和P沟道晶体管。在逻辑高电平时,P沟道管导通,电流流经负载,而N沟道管截止;反之,在逻辑低电平时,N沟道管导通,电流方向相反。由于CMOS电路天然具有高输入阻抗和低输出阻抗的特点,LVCMOS可以高效地驱动其他CMOS电路,并减少对驱动器的电流需求。

LVCMOS的电气特性如下:

- **逻辑高电平**:通常是VDD的80%或更高。

- **逻辑低电平**:通常是VDD的20%或更低。

- **输入电平**:能够接受逻辑高和逻辑低电平。

- **输出电平**:与逻辑电平相匹配,保持良好的噪声容限。

### 2.2.2 LVCMOS的应用场景和优势

由于LVCMOS技术的优越性,它在现代电子设计中被广泛采用,特别是在系统芯片(SoC)和微控制器单元(MCU)等应用中。它的低功耗特性使得它非常适合于电池供电的便携设备,如智能手机、平板电脑以及各种穿戴设备。此外,LVCMOS的高速性能也使其适用于高性能计算系统和高速数据通信应用。

LVCMOS相较于LVTTL等其他接口标准的优势包括:

- **更低的功耗**:由于工作电压范围更宽泛,LVCMOS可以进一步降低功耗。

- **更高的集成度**:CMOS技术的特性使得芯片可以集成更多的逻辑电路。

- **更好的抗噪声能力**:由于其高输入阻抗,LVCMOS对噪声和电磁干扰具有更好的抵抗能力。

随着集成电路技术的发展,LVCMOS接口标准正变得越来越重要,特别是在处理速度要求高、电池寿命关键的应用场景中。然而,LVCMOS也存在一些设计挑战,例如在高速信号下可能会遇到信号完整性的问题。因此,设计时需要考虑适当的电路设计和信号优化措施。

在第三章中,我们将深入探讨如何进行LVTTL与LVCMOS的电路设计和仿真,以确保在实际应用中电路的性能达到最佳状态。

# 3. LVTTL与LVCMOS的电路设计和仿真

## 3.1 电路设计原则和注意事项

### 3.1.1 负载计算与驱动能力分析

在高速数字电路设计中,合理计算负载和分析驱动能力是确保信号完整性和系统稳定运行的基础。对于LVTTL和LVCMOS这样的接口标准,电路设计者需要考虑以下几个关键因素:

- **负载电容(CLOAD)**:这是一个关键参数,它表示接口能够驱动的总电容负载。在设计时,应确保信号源的驱动能力大于负载电容,以保持信号的上升沿和下降沿时间在可接受的范围内。

- **驱动电流(IDRIVE)**:每个输出端口提供的最大电流值。电路设计时,驱动电流必须大于负载电流,以确保信号能够稳定输出。

- **传输延迟**:信号从源端到负载端的传播时间,对于同步系统来说,传输延迟必须小于时钟周期的一部分,以保证数据同步。

- **电源电压(VCC)与阈值电压(VT)**:在设计中,必须确保所有的电压都在规定的范围内,以避免信号电平的偏移。

以下是一个示例代码块,展示了如何计算负载电容并进行初步的驱动能力分析:

```python

# LVTTL接口负载计算与驱动能力分析示例

# 定义参数

Vcc = 3.3 # 电源电压,单位V

IOH = 4.0 # 输出高电平时的最大电流,单位mA

IOL = 4.0 # 输出低电平时的最大电流,单位mA

VT = 1.5 # 阈值电压,单位V

# 负载电容计算

# 假设负载电容包括线缆电容、芯片输入电容等,总共为50pF

CLOAD = 50.0 # 负载电容,单位pF

# 驱动能力分析

# 假设LVTTL的输出高电平和低电平对应的电流分别为IOH和IOL

# 使用线性负载电流近似计算上升时间和下降时间

tr = (Vcc - VT) / IOH * CLOAD

tf = VT / IOL * CLOAD

# 输出分析结果

print(f"负载电容: {CLOAD} pF")

print(f"上升时间: {tr} ns")

print(f"下降时间: {tf} ns")

# 驱动能力是否足够

if tr < 2.0 and tf < 2.0: # 假设设计规格要求上升和下降时间不超过2ns

print("驱动能力足够")

else:

print("驱动能力不足,需要重新设计")

```

在上述代码中,我们首先定义了电源电压、输出电流以及阈值电压这些参数,然后计算了负载电容下的信号上升时间和下降时间。接着,通过比较上升和下降时间是否满足设计规格要求

0

0