图腾柱电路信号完整性完全手册:分析与优化秘籍

发布时间: 2025-01-07 10:38:11 阅读量: 12 订阅数: 17

# 摘要

图腾柱电路信号完整性是高速电子系统设计中的关键考量因素。本文从基础概念出发,深入探讨了图腾柱电路的设计原则、信号特性、电源设计、仿真分析、调试测试以及优化策略。通过对图腾柱驱动器与接收器的基本组成、信号路径的分析、电源分布网络(PDN)的设计,以及信号完整性仿真工具和方法的应用,本文提出了有效的调试、测试和优化技术。最后,本文展望了新技术和行业挑战对图腾柱电路信号完整性未来的影响,并强调了专业教育在该领域的重要性。

# 关键字

图腾柱电路;信号完整性;设计原则;仿真分析;调试测试;优化策略

参考资源链接:[图腾柱驱动电路详解:关键参数与设计考虑](https://wenku.csdn.net/doc/ekvfmsrud3?spm=1055.2635.3001.10343)

# 1. 图腾柱电路信号完整性的基础概念

图腾柱电路是电子工程中一种常见的电路配置,广泛应用于数字信号的驱动。在讨论信号完整性之前,我们首先要理解图腾柱电路的基本工作原理。

## 1.1 什么是信号完整性

信号完整性(Signal Integrity, SI)关注的是电子信号在电路板上从驱动器传输到接收器的过程中保持其完整性的能力。具体来说,就是信号的形状、大小以及到达时间的可靠性。在高速数字电路中,信号完整性问题尤为关键,因为它们直接影响到电路的性能和可靠性。

## 1.2 图腾柱电路的作用

图腾柱电路通过上下两个晶体管的组合来驱动信号,可以提供较强的电流驱动能力,使得信号能够更快速地传输。这种结构特别适合于那些需要快速开关和较大电流的应用场景,比如处理器核心供电、存储设备接口等。

## 1.3 信号完整性的影响因素

影响信号完整性的主要因素包括阻抗不匹配、信号反射、串扰、电源噪声等。图腾柱电路设计时,就需要考虑到这些因素,采取相应措施以保证信号的稳定性和可靠性。

通过了解图腾柱电路的基本概念和信号完整性的重要性,我们可以开始深入探索其设计原则和优化策略,确保在实际应用中电路能够稳定工作。接下来的章节,我们将详细介绍图腾柱电路的设计原则以及如何在实际操作中保证信号的完整性。

# 2. 图腾柱电路的设计原则

## 2.1 图腾柱电路的基本组成

### 2.1.1 图腾柱驱动器与接收器

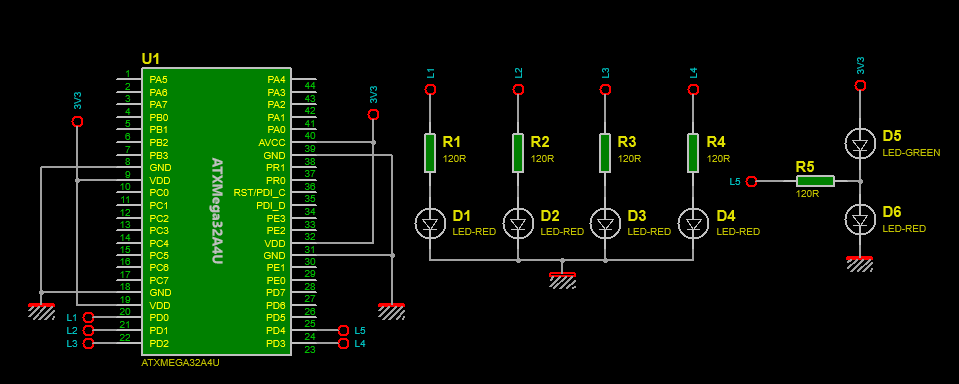

在数字电路设计中,图腾柱驱动器是一种常用的电路组件,用于在电路板上提供足够的电流来驱动负载,比如LED或继电器等。它由两个晶体管组成,一个NPN和一个PNP,它们并行工作以驱动信号。图腾柱接收器用于读取信号,并能识别上升沿和下降沿,这在高速信号传输中尤为重要。

在设计时,需要考虑驱动器的负载能力,以及它与接收器的兼容性。驱动器必须能够提供足够的电流来切换负载状态,同时接收器需要能够在噪声和信号质量不佳的条件下准确读取信号。此外,驱动器和接收器都必须是快速的,以最小化信号的上升和下降时间,这对于高速应用来说是至关重要的。

### 2.1.2 信号路径的关键组成部分

信号路径包括图腾柱驱动器、传输线、接收器以及它们之间的连接点。对于图腾柱电路来说,关键在于维持信号的完整性,防止信号在传输过程中产生失真或噪声干扰。信号路径上的每一个部件都必须精心设计,以确保信号质量。

传输线,如微带线或带状线,应当设计得具有均匀的特性阻抗,这样可以最小化信号反射。此外,传输线的长度和布局方式也需要仔细考虑,以避免信号反射和传输线效应。对于高速信号,阻抗不连续的地方,如过孔、弯角和分叉,都可能导致信号完整性问题。

## 2.2 图腾柱电路的信号特性分析

### 2.2.1 上升和下降时间

在数字电路中,信号的上升和下降时间对信号完整性有很大影响。它们描述了信号从低电平跳变到高电平所需的时间。快速的上升和下降时间对于高速电路而言是非常重要的,因为它们有助于减少信号在电路中的传播延迟,并且降低信号在传输过程中被干扰的可能性。

在设计图腾柱电路时,要确保图腾柱驱动器的输出开关速度快,以提供尽可能短的上升和下降时间。这样可以在信号传输时保持边缘的锐利,减少数据传输过程中的错误。

### 2.2.2 信号反射和传输线效应

信号反射是由于阻抗不匹配引起的,例如当信号从一个特性阻抗传输到另一个特性阻抗的区域时。在图腾柱电路设计中,必须确保传输路径的阻抗连续性,以最小化反射。使用阻抗匹配的传输线和终端匹配技术(如串联电阻或RC匹配网络)可以减少反射。

传输线效应,包括传输线的延迟、信号串扰和电磁干扰(EMI),都是高速信号设计中必须考虑的问题。设计时要对信号路径进行精确控制,以及合理布局关键信号,以最小化这些效应。

### 2.2.3 串扰和电源噪声

串扰发生在高速信号在相邻导线上传输时,一个信号线对另一个信号线产生干扰。这种干扰可以在信号路径上引入额外的噪声,导致数据错误。在图腾柱电路设计中,需要通过合理的布线间隔和屏蔽技术来减少串扰。

电源噪声也是高速信号完整性问题的一个重要方面。开关噪声、瞬态电流和电源线上的干扰可能会影响电路的性能。通过设计有效的电源分布网络(PDN)和去耦电路,可以减少电源噪声对信号的影响。

## 2.3 图腾柱电路的电源设计

### 2.3.1 电源分布网络(PDN)

电源分布网络(PDN)是电源在印制电路板(PCB)上分布的方式,它为IC提供稳定的电源。PDN的设计对确保图腾柱电路的可靠运行至关重要。一个良好的PDN应当能够提供足够的电流和最小的电压波动。

在设计PDN时,必须考虑电源层和地层的布局,以确保电源和地之间的阻抗最小化。这通常涉及使用多个去耦电容器,它们在不同频率下工作,以提供平滑的电源。同时,PDN应该避免高阻抗路径,以减少由于高速开关造成的电压降。

### 2.3.2 电源去耦和去耦电容的选择

去耦是电源系统设计的关键环节,其目的是确保每个IC都有稳定的电源,并且减少电源线上的噪声。去耦电容放置在IC附近,用于吸收IC开关时产生的瞬态电流。

选择去耦电容时,需要考虑其容值、封装类型、等效串联电阻(ESR)和等效串联电感(ESL)。容值的选取需要基于频率响应,ESR和ESL则决定着电容的效能。在高速应用中,通常需要结合不同容值的电容器来覆盖较宽的频率范围。

在第二章中,我们探讨了图腾柱电路设计的基本原则,深入分析了图腾柱电路的组成元素和信号特性,并着重讨论了电源设计的关键方面。接下来的章节将继续深入图腾柱电路的仿真、测试和优化,以及展望图腾柱电路信号完整性的未来趋势。

# 3. 图腾柱电路信号完整性的仿真与分析

图腾柱电路在设计中需要确保信号完整性,而仿真工具和方法提供了一种高效的方式来验证设计的可行性。通过仿真,设计者可以在实物制造前预测电路行为,优化设计参数,降低风险。本章将深入探讨图腾柱电路信号完整性的仿真与分析,包括所用工具、流程、关键步骤和结果解读。

## 3.1 电路仿真工具和方法

### 3.1.1 选择合适的仿真软件

在选择仿真软件时,

0

0