【Zynq-7020性能优化】:解锁计算潜力的5个实用策略

发布时间: 2024-12-25 17:45:28 阅读量: 6 订阅数: 12

ad9361.rar_AD9361 + zynq7020_ZYNQ_7020_Zynq-7020_zc702 AD9361_zy

# 摘要

Zynq-7020是一种将处理系统(PS)与可编程逻辑(PL)集成在同一芯片上的异构多核系统级芯片(SoC)。本文从基础性能挑战入手,详细探讨了Zynq-7020的系统级和软件级性能优化策略。通过硬件加速与资源管理,时钟域和电源管理,以及高效内存管理,系统级性能得到了显著提升。软件性能优化则侧重于操作系统与驱动优化,应用级并行处理,以及编译器优化与分析。此外,网络性能优化章节讨论了网络接口性能调优和无线通信效率改进。最后,综合案例研究通过视频处理和机器视觉应用展示了上述优化策略的实施效果和性能提升。本文旨在为Zynq-7020的用户提供一套全面的性能优化指南,帮助他们在实际应用中达到最佳性能表现。

# 关键字

Zynq-7020;系统级优化;软件性能;网络性能;硬件加速;资源管理

参考资源链接:[xilinx zynq-7020 官方数据手册](https://wenku.csdn.net/doc/6412b6f3be7fbd1778d48900?spm=1055.2635.3001.10343)

# 1. Zynq-7020基础与性能挑战

## 简介

Zynq-7020是由赛灵思(Xilinx)推出的一款系统级芯片(SoC),它集成了双核 ARM Cortex-A9 处理器和可编程逻辑(Programmable Logic, PL),为嵌入式开发者提供了一个既灵活又强大的平台。Zynq-7020在工业控制、智能视频监控、机器视觉等领域拥有广泛应用,其性能直接影响到整个系统的运行效率和稳定性。

## 性能挑战

随着对实时性能和高密度计算需求的日益增长,Zynq-7020在设计时面临着诸多挑战。首先,如何合理分配双核处理器(Processing System, PS)和可编程逻辑(PL)之间的资源,以实现最大化的并行处理能力是一大难题。其次,在保证系统性能的前提下,如何进行有效的时钟域和电源管理,以降低功耗,也是一个亟待解决的问题。最后,Zynq-7020在内存管理上如何通过优化减少延迟,提高数据吞吐量,是性能优化的关键因素之一。

## 本章小结

本章我们将详细介绍Zynq-7020的架构和基础性能,以及在实际应用中可能面临的性能挑战。在后续章节中,我们将进一步探讨系统级、软件层面以及网络层面的性能优化策略,旨在帮助开发者克服这些挑战,最大限度地发挥Zynq-7020的潜能。

# 2.1 硬件加速与资源管理

Zynq-7020作为一款集成FPGA的SoC产品,其硬件加速能力是其核心优势之一。高效地管理和优化PL(Programmable Logic)与PS(Processing System)资源,对于充分利用Zynq-7020的性能至关重要。

### 2.1.1 PL与PS资源优化

PL资源在Zynq-7020中可以实现并行处理和实时数据流的处理,这通常比传统的CPU更高效。为了优化PL资源,设计师需要根据应用需求定制FPGA逻辑,同时也要确保PS的资源被合理利用。对于FPGA的编程,通常使用硬件描述语言(HDL),如VHDL或Verilog。例如,我们可以通过VHDL编写一个简单的并行处理器模块,以加速特定的数学运算:

```vhdl

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.NUMERIC_STD.ALL;

entity ParallelProcessor is

Port ( clk : in STD_LOGIC;

reset : in STD_LOGIC;

data_in : in STD_LOGIC_VECTOR(31 downto 0);

data_out : out STD_LOGIC_VECTOR(31 downto 0));

end ParallelProcessor;

architecture Behavioral of ParallelProcessor is

begin

process(clk, reset)

begin

if reset = '1' then

-- Reset logic here

elsif rising_edge(clk) then

-- Process the data_in and produce data_out

data_out <= std_logic_vector(signed(data_in) + 1);

end if;

end process;

end Behavioral;

```

在这个例子中,`data_in`将被并行地加1并输出到`data_out`。这种类型的自定义硬件模块可以大幅提升数据处理性能。

### 2.1.2 硬件加速器的选择与配置

硬件加速器如专用数字信号处理器(DSP)区块,提供了专用于数学运算的优化逻辑单元。在Zynq-7020中,设计师需要决定哪些运算可以被卸载到硬件加速器上以实现更佳性能。硬件加速器的选择和配置通常需要综合考虑应用需求、功耗、资源占用和加速比。

例如,对于图像处理应用,可以配置FPGA的DSP区块来加速卷积运算,这是一种在图像和信号处理中常见的运算。使用硬件加速器可以减轻CPU负载,实现更快的运算速度。

接下来,让我们探索Zynq-7020的时钟域和电源管理的优化方法。

# 3. Zynq-7020的软件性能优化

随着FPGA技术与处理器技术的融合发展,Zynq-7020这种集成了处理器系统的FPGA成为开发者们的新宠。它为开发者提供了前所未有的灵活性和性能。然而,如果软件性能未得到充分优化,那么其硬件优势将大打折扣。本章将深入探讨如何通过软件层面的优化提升Zynq-7020的整体性能。

## 3.1 操作系统与驱动优化

操作系统是运行在Zynq-7020上的软件生态基础。在实现性能优化之前,首先需要为Zynq-7020选择一个合适且性能优异的操作系统。

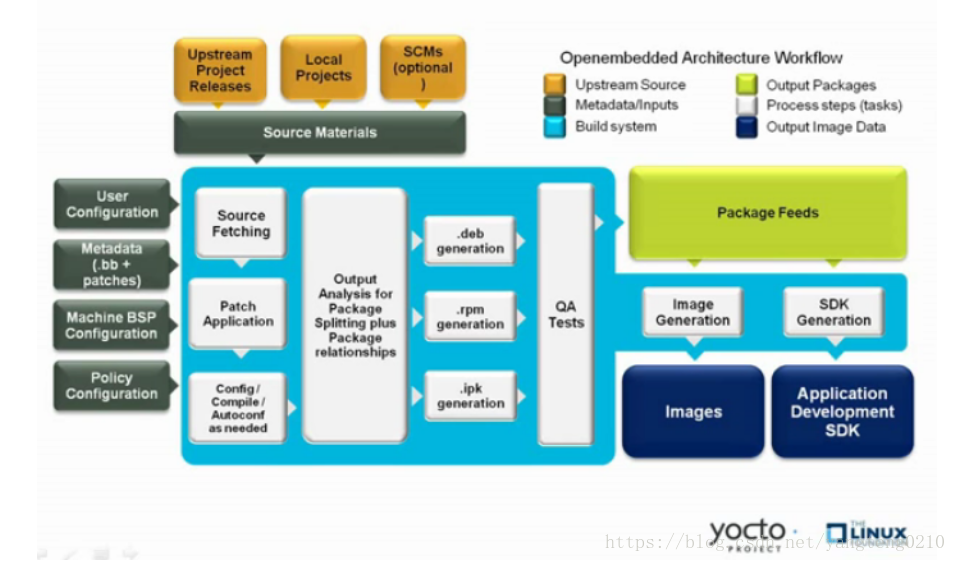

### 3.1.1 选择合适的操作系统

Zynq-7020支持多种操作系统,包括但不限于Xilinx开发的PetaLinux、FreeRTOS和各类通用操作系统。选择合适的操作系统对于优化软件性能至关重要,因为不同的操作系统对资源的利用效率和响应速度各不相同。

一般来说,如果应用对实时性要求较高,可以选择FreeRTOS这类实时操作系统(RTOS)。如果需要运行复杂的、资源占用较大的应用,PetaLinux这类基于Linux的系统可能更加合适。PetaLinux不仅提供了丰富的软件包和开发工具,还支持对硬件资源进行更细致的配置。

### 3.1.2 驱动程序的性能调整

在确定了操作系统之后,接下来就是驱动程序的性能调整。驱动程序是操作系统与硬件之间沟通的桥梁。通过精心编写的驱动程序,可以充分释放硬件的潜力。

驱动程序优化通常包括以下几个方面:

- **中断处理优化**:合理的中断优先级设置和中断服务例程(ISR)的优化可以显著提高系统的响应速度。

- **DMA(直接内存访问)优化**:在Zynq-7020上,DMA可以减少CPU的负担,让CPU从繁重的数据搬运工作中解脱出来,从而专注于处理更加重要的任务。

驱动程序的性能调整通常需要开发者具备深入的操作系统和硬件知识,这样才能达到最优效果。

## 3.2 应用级并行处理

在处理复杂任务时,单线程程序往往难以满足性能需求。此时,多线程编程和多核处理器的任务分配策略就显得尤为重要。

### 3.2.1 多线程编程策略

多线程编程能够充分利用现代处理器的多核资源,实现任务的并发执行。在Zynq-7020上实现多线程编程需要注意以下几点:

- **任务划分**:合理地将大任务分解为若干小任务,确保各个线程之间协作高效,避免过多的线程同步开销。

- **线程同步**:由于多线程共享资源,因此必须使用锁、信号量等同步机制来防止数据冲突。

在编写多线程程序时,可以使用C++11及以上版本的并发库或者POSIX线程(pthread)库。在Linux环境中,pthread库是常用的选择。

### 3.2.2 多核处理器任务分配

在多核处理器中,合理地分配任务可以最大化性能输出。Zynq-7020的双核 ARM Cortex-A9处理器拥有共享的L2缓存,合理的任务分配可以确保缓存的高效利用。

- **静态任务分配**:在应用启动时进行任务分配,这种方法适用于任务性质固定、对响应速度要求不高的场景。

- **动态任务调度**:基于系统负载动态调整任务分配,适合任务数量和复杂度波动较大的应用。

## 3.3 编译器优化与分析

编译器是软件开发中的关键工具,它将高级语言代码转换为可被Zynq-7020执行的机器代码。编译器的选择和优化选项的配置对软件性能有极大影响。

### 3.3.1 编译器优化选项

不同的编译器提供了丰富的优化选项。以GCC为例,它的优化选项如`-O2`和`-O3`可以在编译时自动进行代码优化,提升执行效率。然而,过度优化可能会带来不可预测的副作用,因此需要仔细权衡。

- `-O2`:提供平衡的性能与编译速度的优化。

- `-O3`:执行更多的代码优化,可能包括一些高代价的转换,对性能的提升更显著,但可能会增加编译时间和程序大小。

### 3.3.2 性能分析工具使用

编译器优化之后,如何验证性能是否得到提升呢?这时就需要性能分析工具的帮助。性能分析工具可以揭示程序运行时的瓶颈,例如CPU使用率、内存访问模式等。

- **Valgrind**:可以分析程序中的内存泄漏、缓存未命中的情况。

- **gprof**:提供函数调用的统计信息,帮助开发者识别性能热点。

性能分析是软件优化不可或缺的环节,通过反复迭代,可以持续提升软件性能。

以上就是第三章Zynq-7020的软件性能优化的核心内容。通过操作系统的合理选择、驱动程序的精细调整、多线程策略的精心设计以及编译器优化,可以显著提升Zynq-7020的软件运行效率,充分利用这一强大硬件平台的潜力。在后续的章节中,我们将进一步探讨Zynq-7020的网络性能优化以及结合实际案例来更深入地了解如何将这些理论付诸实践。

# 4. Zynq-7020的网络性能优化

Zynq-7020作为Xilinx推出的一款高度集成的可编程SoC,它具备处理器和FPGA的双重特性,广泛应用于工业、消费电子、通信等领域。网络性能的优化对于提高这些应用的实时性、稳定性和效率至关重要。本章节将详细介绍网络接口性能调优以及无线通信效率改进的方法和策略。

## 4.1 网络接口性能调优

### 4.1.1 网络堆栈优化

在网络接口性能调优中,首先需要考虑的是网络堆栈的优化。网络堆栈是操作系统中处理网络通信协议的软件部分,优化网络堆栈可以显著提高数据传输的效率和稳定性。

由于网络堆栈中涉及的参数较多,调整这些参数需要充分了解网络通信机制和系统的运行情况。以下是一些网络堆栈优化的关键点:

1. 调整TCP/IP缓冲区大小:合理配置发送和接收缓冲区(如`tcp_rmem`和`tcp_wmem`)可以减少丢包,提高网络吞吐量。

2. 调整MTU(最大传输单元):通过设置合适的MTU值(如`net.core.rmem_max`),可以减少数据包分片,降低CPU负载。

3. 开启TCP窗口缩放和时间戳选项:这些TCP选项可以帮助在高延迟或高速网络中维持有效的网络吞吐量。

代码示例如下:

```shell

# 增加TCP的最大接收缓冲区大小

sysctl -w net.core.rmem_max=16777216

# 开启TCP窗口缩放

sysctl -w net.ipv4.tcp_window_scaling=1

# 开启TCP时间戳

sysctl -w net.ipv4.tcp_timestamps=1

```

在进行堆栈优化时,除了上述配置,还应针对具体的网络环境和应用需求进行细致的调整。

### 4.1.2 实时网络数据处理

在处理实时数据流时,网络延迟和数据处理能力成为关键因素。为提高Zynq-7020的实时网络数据处理能力,可以采取以下措施:

1. 使用零拷贝技术:通过减少数据在用户空间和内核空间之间的复制次数(如使用`sendfile`系统调用),可以提高数据处理效率。

2. 优化中断处理:合理配置中断优先级和处理逻辑,减少中断延迟,提高响应速度。

3. 使用DMA(直接内存访问):通过DMA技术,硬件设备可以直接访问系统内存,而无需CPU介入,从而提高数据传输效率。

代码示例:

```c

// 零拷贝示例:使用sendfile系统调用

#include <sys/sendfile.h>

int out_fd, in_fd;

off_t offset;

size_t count;

count = read_in(&buf, len);

offset = 0;

sendfile(out_fd, in_fd, &offset, count);

```

在实际应用中,可能还需要结合操作系统提供的特定机制,如Linux中的实时调度策略,来满足更严格的实时性要求。

## 4.2 无线通信效率改进

### 4.2.1 Wi-Fi性能调优

为了在Zynq-7020上获得更好的Wi-Fi性能,可以通过以下策略进行优化:

1. 选择合适的驱动程序:确保安装了与硬件兼容且更新的驱动程序,可以提供更好的性能和稳定性。

2. 配置无线信道和带宽:合理选择和配置无线信道和带宽(如2.4 GHz vs. 5 GHz),避免干扰,提升连接速度。

3. 调整功率设置:适当提高或降低发射功率,可以平衡覆盖范围与能耗。

代码示例:

```shell

# 配置Wi-Fi信道为1

iwconfig wlan0 channel 1

# 配置Wi-Fi信道宽度为20MHz

iwconfig wlan0 channel_width 20MHz

```

### 4.2.2 蓝牙与ZigBee优化方案

蓝牙与ZigBee也是Zynq-7020在无线通信方面的重要考量。对于这两种技术的优化,可以从以下几个方面入手:

1. 优化连接参数:如调整连接间隔、超时、尝试次数等参数,以适应不同的应用场景。

2. 选择合适的协议栈:选择经过优化的协议栈,并确保其与硬件兼容,可以提供更高的数据传输效率。

3. 减少设备间的干扰:通过使用不同的频道,或者采用跳频技术等措施,减少信号干扰,提高通信质量。

代码示例:

```shell

# 蓝牙扫描发现设备

hcitool lescan

```

在实际应用中,可能需要综合应用多种优化策略,并通过实际测试来确定最佳的优化方案。

在本章节中,我们详细介绍了网络接口性能调优和无线通信效率改进的方法和策略。需要注意的是,网络性能的优化是一个多方面综合考虑的过程,需要根据实际应用场景和需求来调整和选择最合适的优化方法。通过细致的网络堆栈优化、实时数据处理技术的应用,以及无线通信协议的优化配置,可以显著提升Zynq-7020在网络应用中的性能表现。

# 5. Zynq-7020的综合案例研究

## 5.1 案例分析:视频处理优化

### 5.1.1 视频流处理技术

视频流处理是现代嵌入式系统中常见的应用之一,尤其在安全监控、工业视觉检测和多媒体娱乐领域。Zynq-7020作为一款集成了FPGA和ARM处理器的SoC,它为视频流处理提供了灵活的硬件加速选项。

实现视频流处理的基本技术包括:

- **像素处理**:视频流由一系列帧组成,每一帧都是由像素矩阵构成。像素处理通常包括去噪、对比度增强、色彩空间转换等操作。

- **帧率转换**:视频可能需要调整帧率以适应不同的输出设备或网络带宽。这涉及到帧的插值和删除。

- **分辨率调整**:为了适应不同的显示需求或压缩要求,视频流可能需要改变分辨率。

- **压缩与解压缩**:为了减少存储和传输视频所需的空间,通常会对视频数据进行压缩。

针对这些技术,在Zynq-7020上实现视频处理时,我们可以利用FPGA部分进行高速数据处理,如像素级的运算,而CPU部分则可以处理复杂的控制逻辑和不适合硬件加速的算法。

### 5.1.2 实时视频分析的性能挑战

实时视频分析要求系统不仅能够高效处理视频流,还要在规定的时间内完成分析任务。这给Zynq-7020带来了性能上的挑战,因为系统的响应时间取决于多个因素:

- **数据吞吐量**:视频数据量庞大,系统的I/O带宽必须足够高,以避免数据积压。

- **处理延迟**:视频分析算法往往复杂,需要在尽可能短的时间内完成计算。

- **系统负载平衡**:平衡CPU和FPGA的负载,使得两者都能高效运行,避免资源闲置。

为了应对这些挑战,开发者可以采取以下策略:

- **硬件加速器的运用**:将视频分析的关键部分如边缘检测、特征提取等算法部署在FPGA中,利用硬件加速器实现高效处理。

- **多线程处理**:利用Zynq-7020的多核CPU,通过多线程编程技术将不同的任务分配到不同核心,以并行方式提升处理能力。

- **缓存优化**:合理使用和配置缓存,减少内存访问延迟。

## 5.2 案例分析:机器视觉应用

### 5.2.1 机器视觉系统的需求分析

机器视觉系统通常需要完成图像的采集、处理、识别、测量以及判断等功能。在诸如自动化装配、产品质量检测和智能监控等场景中,机器视觉的应用越来越广泛。

对于Zynq-7020这样的嵌入式平台,机器视觉系统通常具备以下需求:

- **高速度**:系统需要快速响应外部事件,如工业相机的高速图像捕获。

- **高精度**:图像处理和识别需要有较高的精度,以确保决策的准确性。

- **实时性**:在许多场合,如运动控制,机器视觉系统需要实时处理图像并做出响应。

为了满足这些需求,开发者需要深入了解机器视觉的算法和Zynq-7020的硬件特性,实现定制化的系统优化。

### 5.2.2 系统性能优化策略

为了提升机器视觉系统的性能,可采取以下优化策略:

- **算法优化**:选择或改进适合硬件加速的图像处理和识别算法,如使用卷积神经网络(CNN)进行物体识别。

- **并行处理**:利用Zynq-7020的PL部分进行图像预处理,并行化关键算法,减少CPU负载。

- **内存管理**:合理分配和管理内存,尤其是在数据传输和缓存中,优化内存的读写效率。

系统优化是一个综合性的工程,需要根据具体应用场景和需求反复调试,以达到最佳的性能效果。

```mermaid

graph LR

A[数据采集] -->|相机| B[图像缓冲]

B --> C[硬件预处理]

C -->|FPGA| D[算法处理]

D -->|ARM| E[结果输出]

E -->|网络/IO| F[应用层]

```

以上流程图描述了机器视觉系统中数据处理的简化流程,展示了不同处理阶段如何在Zynq-7020的架构中协同工作。通过这种优化后的流程,系统可以更高效地完成复杂的机器视觉任务。

0

0