SMBus与PCIe的深度整合:迈向高性能通信的解决方案

发布时间: 2024-12-25 11:33:16 阅读量: 3 订阅数: 10

# 摘要

本论文对SMBus与PCIe技术进行了全面的概览和理论分析,并探讨了两者深度整合的关键技术及实践应用。通过深入解析SMBus协议和PCIe标准的架构及通信协议,本文揭示了现代计算机系统高性能通信的需求与挑战,尤其是在高速数据传输方面。随后,文章详细介绍了SMBus与PCIe深度整合的架构设计、集成方法、实现机制及性能优化策略。通过实践应用案例的分析,如高性能计算和数据中心通信,本文评估了整合技术的实际效果,并探索了物联网与边缘计算领域整合的可能性。最后,本论文展望了技术发展趋势和应用前景,为开发者提供了一份详尽的指南和最佳实践分享。

# 关键字

SMBus;PCIe;深度整合;架构设计;性能优化;实践应用

参考资源链接:[SMBus协议详解与操作指南](https://wenku.csdn.net/doc/64744b82d12cbe7ec310f197?spm=1055.2635.3001.10343)

# 1. SMBus与PCIe技术概览

## 1.1 系统总线技术简介

在现代计算系统中,总线技术是连接硬件组件的关键桥梁。系统管理总线(SMBus)和PCI Express(PCIe)是两种广泛采用的总线技术,分别承担了系统管理任务和高速数据传输任务。

SMBus是一种低带宽串行总线,设计用于管理计算机系统中的传感器和设备,如温度和电压监控器。它的简单性、易用性使其成为硬件监控的标准。

相比之下,PCIe则是一种高速串行计算机扩展总线标准,广泛应用于显卡、SSD硬盘、网络卡等多种高速数据传输场合。PCIe的版本不断迭代,支持了更高的带宽和更低的延迟,极大地推动了计算机性能的提升。

## 1.2 总线技术的重要性

总线技术的优劣直接影响整个系统的性能和效率。SMBus虽然速度较慢,但其稳定性和简便性让它成为系统管理不可或缺的部分。而PCIe,随着技术的进步,正逐渐成为数据传输的主要方式,其速度和效率的提升对计算机系统性能的影响日益显著。

## 1.3 SMBus与PCIe的互补性

虽然SMBus与PCIe在应用上有不同的侧重点,但它们在系统内部起到了互补的作用。SMBus管理着系统的基础健康状态,而PCIe则处理着高速数据传输任务,共同确保整个计算机系统的高效运作。

总结来说,SMBus与PCIe作为系统内连接设备的总线技术,各自拥有独特的功能和优势,是现代计算机系统不可或缺的组成部分。在接下来的章节中,我们将深入探讨这两种技术的理论基础,以及如何在实践中深度整合它们以满足不断增长的性能需求。

# 2. SMBus与PCIe的理论基础

### 2.1 SMBus协议深入解析

#### 2.1.1 SMBus的工作原理

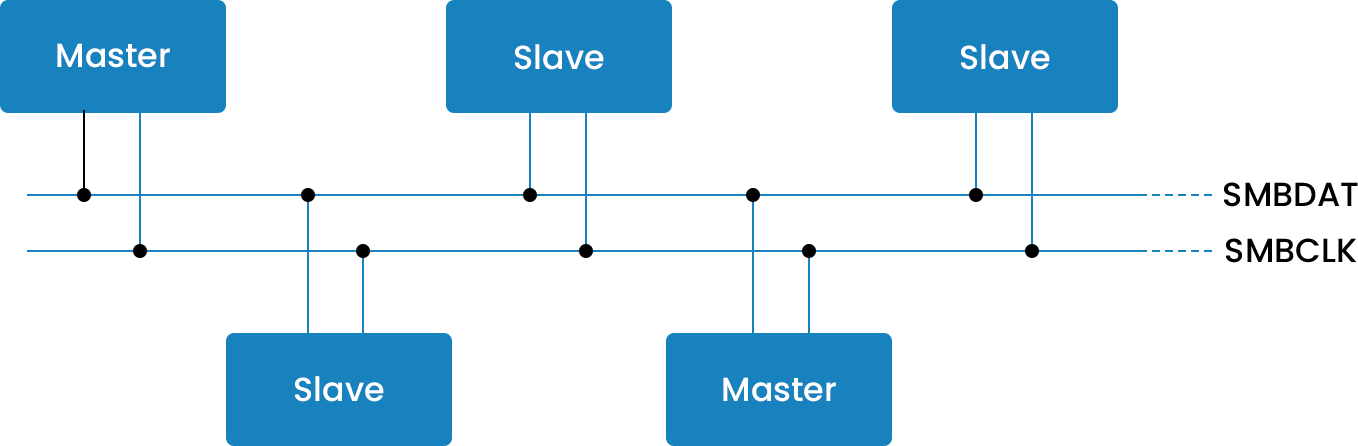

SMBus(System Management Bus)是一种双线串行计算机总线,它基于I²C(Inter-Integrated Circuit)总线协议,并对其进行优化,用于低带宽系统管理通信。SMBus在硬件级别上共享物理层与I²C,但通过不同的协议实现区别开来,主要侧重于更高的数据完整性。

SMBus工作时,两根线分别担任数据(SDA)和时钟(SCL)的角色。通信过程中,主设备发起数据传输,通过发送起始条件、设备地址、读写位、数据及结束条件等来进行。SMBus增加了一些错误检测机制,例如字节计数字段和数据包序列号,增强了数据传输的可靠性。

在SMBus协议中,有三种主要的数据传输模式:

- 快速模式(Fast-mode),传输速率可达400kbps。

- 高速模式(High-speed mode),传输速率可达3.4Mbps。

- 超高速模式(Ultra-fast mode),传输速率可达5MHz。

其中,超高速模式的提出是为了满足系统管理应用中对更高速率的需求,同时保持与前两种模式的向后兼容性。

```mermaid

graph LR

A[开始通信] --> B[起始条件]

B --> C[发送设备地址]

C --> D[读写位]

D --> E[发送数据/接收确认]

E --> F[结束条件]

```

#### 2.1.2 SMBus的数据传输机制

数据传输是通过一系列的读写操作完成的。当SMBus设备被寻址时,它可能执行一个读操作或写操作。在写操作中,主机发送起始条件,然后发送设备地址和写位,接下来发送数据,最后发送停止条件。在读操作中,过程类似,但主机在发送起始条件后,发送设备地址和读位,然后接收来自从设备的数据,最后发送停止条件。

为了保证数据传输的完整性,SMBus引入了仲裁机制和时钟同步机制。仲裁机制确保了当多个主设备试图同时控制总线时,只有一个主设备能够进行通信。时钟同步机制则确保了在高速数据传输时,主设备和从设备的时钟频率能够保持一致,避免数据错位。

### 2.2 PCIe标准的架构剖析

#### 2.2.1 PCIe的层次模型

PCI Express(PCIe)是一种高速串行计算机扩展总线标准,它用于连接主板与各种插卡,以及与其他硬件设备的互连。PCIe采用点对点串行连接,每个连接都由一对差分信号线组成,每个方向一个。PCIe连接由一系列的层组成,从物理层到逻辑层,以实现数据的高速传输。

- 物理层(PHY):负责信号的发送与接收,确定电气特性和信号的物理接口。

- 数据链路层:负责数据的序列化和反序列化,以及流量控制。

- 事务层:定义了数据包的格式,处理事务请求和响应。

- 软件层:与操作系统的驱动程序和API进行交互。

这些层次一起工作,确保数据可以在不同层次间无缝传输,同时保持数据的完整性和可靠性。

```mermaid

graph TB

A[应用层] -->|控制命令| B(事务层)

B -->|数据包| C(数据链路层)

C -->|帧| D(物理层)

D -->|物理连接| E[硬件设备]

E -->|物理连接| D

D -->|帧| C

C -->|数据包| B

B -->|控制命令| A

```

#### 2.2.2 PCIe的通信协议

PCIe通信协议基于包交换,与SMBus协议不同,PCIe没有固定长度的数据包。数据包的大小可以从几个字节到几千字节不等,这种灵活性使得PCIe可以支持高带宽的应用。通信时,数据包被分段发送,接收设备负责重新组装这些数据包。

PCIe使用“事务层包”(TLPs)来执行数据传输,这些包包含地址、数据以及控制信息。TLPs通过“数据链路层包”(DLLPs)传输,DLLPs则用于维护连接的可靠性和数据完整性。由于PCIe是一个全双工通信协议,因此可以同时在两个方向上进行数据传输,大大提升了带宽效率。

### 2.3 高性能通信的需求与挑战

#### 2.3.1 现代计算机系统中的通信需求

随着计算机技术的发展,现代计算机系统对通信的需求越来越高。高性能计算(HPC)系统、数据中心、云计算和大数据分析等应用场景需要大量的数据在不同组件之间高效传输。这些需求推动了通信技术的发展,尤其是对高速和可靠的数据通信机制的要求。

系统对低延迟和高吞吐量的需求,使得设计师必须考虑如何优化硬件架构,以及如何通过软件层实现高效的数据管理。此外,系统管理方面的通信需求也不容忽视,例如温度监控、电压控制等,它们需要实时的数据更新,这就对通信协议的实时性和可靠性提出了更高的要求。

#### 2.3.2 高速数据传输的挑战

高速数据传输面临的挑战是多方面的。首先,随着数据传输速率的提升,信号完整性

0

0