电路板设计与布局:在PCB设计中正确布局74LS279的策略

发布时间: 2024-12-13 16:19:15 阅读量: 7 订阅数: 13

电路板设计课件辅学:电子CAD电路板设计考证.pptx

参考资源链接:[74LS279中文资料与应用:引脚图详解](https://wenku.csdn.net/doc/647958e8543f8444881a589b?spm=1055.2635.3001.10343)

# 1. 电路板设计与布局基础

在现代电子设计领域,电路板(PCB)设计与布局是确保设备性能和可靠性的关键步骤。本章将为读者提供电路板设计与布局的基础知识,为理解后续章节中74LS279芯片的应用打下坚实的基础。

## 1.1 设计流程简介

电子设备的设计流程包括需求分析、电路原理图设计、PCB布局与布线以及后期的测试与验证。在这些步骤中,PCB布局与布线阶段决定了电路板的电气性能和物理特性。

## 1.2 设计原则

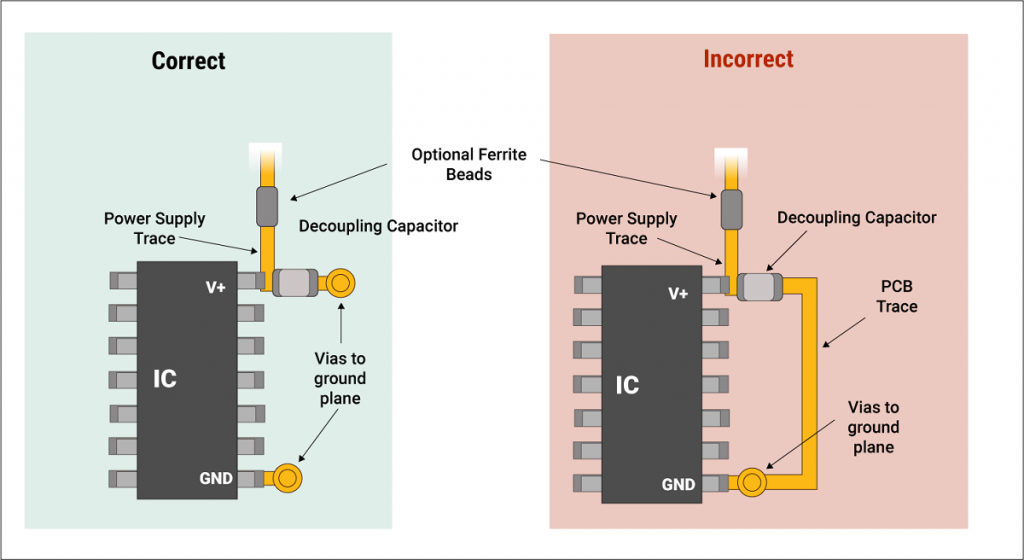

在电路板设计的初期,设计者需要遵循一些基本原则,比如元件布局应尽量紧凑,走线应短且直,避免不必要的过孔,以及考虑信号的完整性、电源管理和热管理等因素。

## 1.3 PCB布局与布线技术

设计一个良好的PCB不仅仅是将元件放在板子上那么简单,它还需要合理的信号路径设计、元件的适当排列以及对电源和接地的精心规划。这有助于减少干扰、电磁兼容性问题,并确保电路板能够稳定工作。

本章旨在让读者对PCB设计与布局的基本知识有一个全面的了解,为深入学习74LS279芯片的应用和PCB设计软件的使用做好准备。接下来的章节,我们将详细介绍74LS279芯片的特性和应用,以及它如何在PCB设计中发挥作用。

# 2. 理解74LS279芯片特性及其应用

### 2.1 74LS279芯片功能概述

#### 2.1.1 74LS279芯片的逻辑功能

74LS279是一款四路集电极开路的RS触发器集成电路,用于存储二进制信息。每个RS触发器都有两个输入端(Set和Reset),一个输出端(Q),以及一个非反向输出端(\~Q)。RS触发器的主要功能是根据输入信号来改变输出状态。Set输入置高电平时,会使得输出端Q置为高电平,而Reset输入置高电平时,则会使Q置为低电平。当两个输入端都为低电平时,RS触发器保持当前状态不变。值得注意的是,高电平有效(正逻辑)。

#### 2.1.2 74LS279的应用场景

由于RS触发器能够存储一位信息,74LS279在很多数字逻辑设计中都非常有用。比如,它可以用于构建计数器、寄存器、移位寄存器、存储器等数字逻辑电路。它也经常用于接口电路设计中,为逻辑电平提供缓冲,或者在一些控制电路中用于存储临时状态。另外,74LS279的集电极开路输出可以驱动较大的负载,这对于诸如继电器驱动、LED驱动等应用场景尤其重要。

### 2.2 74LS279芯片的电气特性

#### 2.2.1 电源和接地要求

74LS279芯片采用正逻辑供电,其标准工作电压为5伏直流电。供电电压(Vcc)范围在4.75V到5.25V之间,超过这个范围可能会损坏芯片或影响其性能。接地(GND)端是电路的共同参考点,芯片中所有的逻辑低电平都参考于此。

#### 2.2.2 输入输出特性分析

74LS279芯片的输入端对输入信号的高低电平要求严格,通常输入高电平为2V以上,输入低电平为0.8V以下。输出特性则包括集电极开路输出,这意味着输出端可以外接上拉电阻,从而输出驱动更大的电流或更高的电压。输出高电平时,电流取决于外接上拉电阻和输出电压之间的关系。

### 2.3 74LS279与其他集成电路的接口

#### 2.3.1 驱动能力与匹配问题

由于74LS279是集电极开路输出,因此在与具有TTL输入的其他集成电路连接时,需要考虑驱动能力匹配问题。为了确保可靠的工作,必须使用适当的上拉电阻来保证输出高电平的有效性。同时,电阻值的选择还要考虑到功耗和速度的平衡,避免过大的电流导致的热量积累或过小的电流导致的信号完整性问题。

#### 2.3.2 高速信号完整性和信号同步

在高速信号设计中,为了保证信号完整性和同步,74LS279芯片的布线应该尽可能短,以减少信号传输延迟。同时,输出信号路径需要与其它高速信号路径保持一致的长度,以避免由于路径差异引起的信号时序问题。如果可能,需要使用终端匹配技术,例如串联终端电阻或采用差分信号布线,来进一步提升信号质量。

以下是部分代码块和表格的示例:

```mermaid

graph LR

A[开始] --> B[理解74LS279芯片]

B --> C[功能概述]

B --> D[电气特性]

B --> E[与其他IC接口]

C --> C1[逻辑功能]

C --> C2[应用场景]

D --> D1[电源和接地要求]

D --> D2[输入输出特性]

E --> E1[驱动能力与匹配]

E --> E2[信号完整性和同步]

```

```markdown

| 项目 | 描述 |

|------------------|-----------------------------------|

| 工作电压范围 | 4.75V 到 5.25V |

| 输出类型 | 集电极开路 |

| 最大输出电流 | 50mA |

| 逻辑电平 | 高电平2V以上,低电平0.8V以下 |

| 上拉电阻推荐值 | 1KΩ到10KΩ |

```

```电路

+Vcc (5V)

|

+----+----+----+----+

| | |

RS1 RS2 RS3

(74LS279) (74LS279) (74LS279)

| | |

\ / \ / \ /

Q Q Q

| | |

+-----------+-----------+

|

GND

```

请注意,以上示例代码、表格和流程图仅为说明用途,并非实际可用于74LS279芯片。实际电路设计中需要根据具体需求和电气规格来设计。

# 3. PCB布局的理论基础

### 3.1 PCB布局的重要性

#### 3.1.1 布局对信号完整性的影响

在数字电路中,信号完整性(SI)是一个关键因素,决定了电路板能否正常运行。PCB布局对信号完整性的影响主要体现在走线长度、阻抗匹配以及信号的互连等方面。信号在传输路径上的反射、串扰和衰减等现象可以通过合理的布局策略来降低。

为了维持信号完整性,设计者必须确保信号走线短而直,尽量减少分支。这意味着关键信号线应尽可能短,以减少传播延迟和电磁干扰。此外,高速信号路径应该避免急转弯,以防止阻抗突变,从而减少信号反射。

信号的阻抗匹配也是非常重要的,如果源和负载之间的阻抗不匹配,将导致信号反射,影响信号的质量。在设计中,可以通过使用特性阻抗匹配的走线来优化信号路径,确保信号的顺利传输。

#### 3.1.2 布局对电源完

0

0