时钟管理大师:EP4CE10的时钟域处理技巧

发布时间: 2024-12-28 09:23:55 阅读量: 5 订阅数: 10

FPGA EP4CE10驱动RTC实时时钟,数码管显示(Verilog HDL实现).zip

# 摘要

本文重点探讨了EP4CE10 FPGA的时钟管理技术,从基础理论到高级应用技巧进行了全面的分析。首先介绍了EP4CE10 FPGA的基本概念以及时钟域的基础知识,接着深入讨论了时钟域交叉和同步问题,包括同步机制的基本原理、各种同步技术及其调试与预防方法。第三章通过具体实践,详细说明了时钟域处理的管理、编程实践和性能评估。第四章则探讨了动态时钟域切换技术、故障安全设计及时钟域技术的未来发展趋势。最后,通过案例研究与实战演练,分析了实际问题的解决方案,并设计了优化的时钟域管理实例,提供了一系列性能测试的分析结果。本文为设计者提供了一套完整的FPGA时钟管理解决方案,旨在提升时钟域处理的性能与可靠性。

# 关键字

EP4CE10 FPGA;时钟域交叉;同步机制;动态时钟切换;故障安全设计;性能评估

参考资源链接:[EP4CE10F17C8 FPGA引脚图与教程手册](https://wenku.csdn.net/doc/2h5hghnfv6?spm=1055.2635.3001.10343)

# 1. EP4CE10 FPGA简介与时钟概念

随着现代电子系统变得越来越复杂,FPGA(现场可编程门阵列)技术因其可重配置性和高性能而变得越发重要。在众多FPGA产品中,Cyclone IV系列的EP4CE10F17C8N器件,凭借其低成本、高集成度和丰富的I/O资源,成为了中端应用的理想选择。本章节将简要介绍EP4CE10 FPGA的特点,并概述其时钟概念,为后续章节中对时钟域的深入探讨打下基础。

## EP4CE10 FPGA特点概述

EP4CE10是Altera(现为Intel旗下品牌)Cyclone IV系列中的一员,它的主要特点包括:

- **集成度高**:具有超过10万个逻辑单元(LEs)和4 Mbits的嵌入式存储器。

- **I/O资源丰富**:提供多达172个用户I/O引脚,支持多种I/O标准。

- **成本效益**:价格适中,适合预算有限的应用。

- **低功耗设计**:优化的功耗特性使其适用于低功耗要求的场合。

## 时钟在FPGA设计中的作用

时钟信号在FPGA设计中扮演着至关重要的角色,因为它负责协调和同步所有的内部操作。时钟信号必须保持稳定且精确,才能确保FPGA内部逻辑和时序约束的正确执行。理解时钟的工作原理和特点对于设计高效且稳定的FPGA系统是必不可少的。

- **时钟信号**:作为数字电路的“心跳”,它定义了数据处理的速率和同步机制。

- **时钟域**:在FPGA设计中,不同的模块可能需要运行在不同的时钟频率下,这些不同的时钟范围被称作时钟域。

- **时钟管理单元(CMU)**:包括相位锁环(PLL)和时钟树,它负责生成、分配和调节内部时钟信号,以满足系统需求。

本章的后续部分将探讨EP4CE10 FPGA的时钟管理单元,并介绍时钟域的基础概念,为深入理解后续章节中的时钟域交叉和同步问题奠定基础。

# 2. 时钟域交叉与同步问题

## 2.1 时钟域交叉的基础理论

### 2.1.1 时钟域交叉的定义和影响

在数字电路设计中,时钟域交叉(CDC)是指信号从一个时钟域传输到另一个时钟域,而这两个时钟域的时钟频率可能不同,甚至无法保证同步关系。信号的采样可能在错误的时间点进行,导致数据不稳定,甚至产生毛刺(Glitch),从而引起数据丢失或错误。这种情况下,就需要使用同步技术来保证数据传输的正确性和可靠性。

影响方面,时钟域交叉主要导致以下问题:

- **数据失真**:由于在不恰当的时钟边沿采样,导致数据无法正确反映其真实状态。

- **同步失败**:在多时钟域系统中,信号的同步失败可能引起系统不稳定。

- **设计复杂度增加**:需要在设计中增加额外的同步电路来处理时钟域之间的转换。

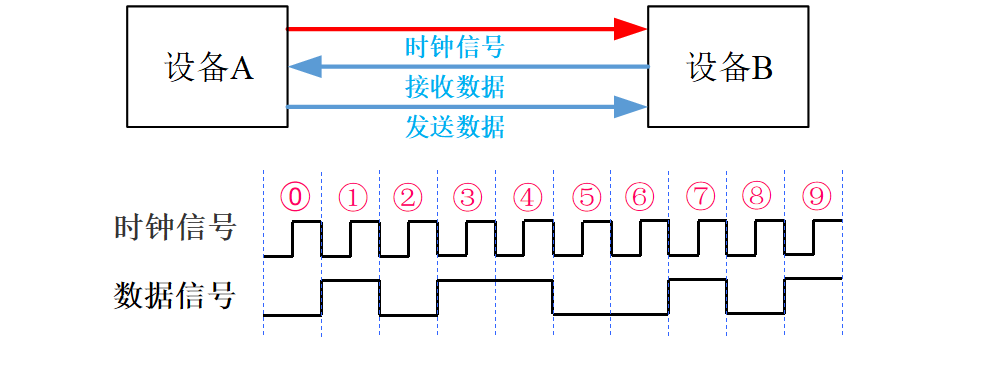

### 2.1.2 同步机制的基本原理

同步机制的目的是保证数据在跨越时钟域时的正确性和稳定性。基本原理是使用一个或多个触发器(如D触发器)对信号进行采样,这些触发器被配置在一个稳定的时钟域内,以确保采样的一致性和可靠性。下面简述几种常见的同步机制:

- **双触发器同步法**:在一个时钟域中用两个触发器连续采样信号。这种方法利用了亚稳态的原理,可以极大地降低由于时钟域交叉而造成的亚稳态错误。

- **中继器和握手协议**:在发送和接收时钟域之间使用中继器来检测和响应信号。握手协议用于确认信号成功传输,确保数据传输的准确性和完整性。

- **多拍稳定法**:在高速时钟域中,使用多个时钟周期来对信号进行稳定采样,然后才认为信号可靠地跨越了时钟域。

## 2.2 时钟域同步技术

### 2.2.1 双触发器同步法

双触发器同步法是解决时钟域交叉问题的最基本和有效的方法之一。其核心思想是在信号进入接收时钟域之前,先经过两个连续的D触发器进行采样,如下图所示:

其中,`CLK1`和`CLK2`是两个不同的时钟域,而`DFF1`和`DFF2`是触发器。当信号从`CLK1`域切换到`CLK2`域时,先通过`DFF1`,然后通过`DFF2`。在经过第一个触发器后,如果信号产生了亚稳态,第二个触发器的时钟边沿将会在一个稳定的点采样,从而消除了亚稳态的风险。

### 2.2.2 中继器和握手协议

中继器和握手协议是一种同步机制,适用于大量数据在不同时钟域之间传输的场景。以下是中继器和握手协议的基本步骤:

1. **发送中继器检测**:当数据准备发送到另一个时钟域时,首先由发送端的中继器检测数据是否准备就绪。

2. **握手信号发送**:一旦检测到数据准备好,发送端中继器会通过握手协议发送一个信号到接收端。

3. **接收端确认**:接收端中继器收到信号后,会返回一个确认信号。

4. **数据传输**:确认信号接收后,数据会被发送到接收端的时钟域。

### 2.2.3 先进的同步技术:多拍稳定法

多拍稳定法是一种更为先进的同步技术,适用于高速信号穿越时钟域的场景。其主要思想是让信号在接收时钟域中经过多个时钟周期的稳定采样,以确保信号稳定。

在实现上,这通常需要设置多个寄存器对信号进行连续采样,示例代码如下:

```verilog

module multi_stage_sync(

input wire clk接收域, // 接收时钟域

input wire rst_n, // 接收时钟域复位信号

input wire signal源域, // 来自源时钟域的信号

output reg signal_稳定 // 稳定后的信号输出

);

reg [N-1:0] sync_reg; // N个寄存器组成同步链,N根据需要设定

always @(posedge clk接收域 or negedge rst_n) begin

if (!rst_n) begin

sync_reg <= 0;

signal_稳定 <= 0;

end else begin

sync_reg <= {sync_reg[N-2:0], signal源域};

signal_稳定 <= sync_reg[N-1]; // 取最后一个寄存器的输出作为稳定信号

end

end

endmodule

```

在上述代码中,`N`表示同步链的长度,其值的选择依据于信号稳定性和设计需求。较长的同步链可以增加信号稳定的可靠性,但同时也会增加延迟。

## 2.3 时钟域问题的调试与预防

### 2.3.1 常见的时钟域问题及其解决方案

时钟域交叉问题在FPGA设计中非常常见,以下是常见的问

0

0